# Zeitgenaue Simulation gemischt virtuell-realer Prototypen

Der Fakultät für Elektrotechnik und Informatik der Universität Hannover zur Erlangung des akademischen Grades Doktor-Ingenieur genehmigte

Dissertation

von Dipl.-Ing. Stefan Eilers geboren am 5. Juni 1971 in Wilhelmshaven

Referent: Prof. Dr.-Ing. C. Müller-Schloer Korreferent: Prof. Dr.-Ing. Bernardo Wagner

Tag der Promotion: 12.01.2006

### Vorwort

Die vorliegende Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Systems Engineering, FG System- und Rechnerarchitektur der Universität Hannover.

Mein besonderer Dank gilt Herrn Prof. Dr.-Ing. C. Müller-Schloer für die wissenschaftliche Betreuung dieser Arbeit. Besonders dankbar bin ich dafür, dass er mich in meinen Bemühungen immer bestärkt und kritisch begleitet hat sowie mir den nötigen Freiraum für die Gestaltung dieser Arbeit gewährte.

Herrn Prof. Dr.-Ing. Bernardo Wagner danke ich für die Übernahme des Korreferats.

Allen Kollegen und Studenten danke ich für die persönliche und wissenschaftliche Unterstützung. Besonders möchte ich mich bei Herrn Dipl.-Ing. Tim Oodes bedanken, dessen konstruktiv kritische Haltung mir immer ermöglichte, den richtigen Weg zu finden.

Abschließend möchte ich diese Arbeit Dr. Annette Schultz widmen. Ohne sie erschiene mir nichts als erstrebenswert.

### Kurzfassung

In Systemen der Automobil-, Telekommunikations- und Automatisierungstechnik steigt der Anteil eingebetteter Systeme drastisch an. Neben komplexer werdenden mechatronischen Komponenten, ist ebenfalls ein zunehmender Einsatz von eingebetteten Steuerungen auf Basis von *Embedded Control Units* (ECU) zu verzeichnen. Diese steuern und überwachen nicht nur die mechatronischen Systemteile, sondern stehen untereinander in Verbindung und beeinflussen sich gegenseitig. Dies führt zu einer deutlichen Erhöhung der Komplexität und des prozentualen Anteils an Software innerhalb des Gesamtsystems.

Ein Entwickler hat somit einen Weg zu finden, um die Lücke zu schließen, die sich aufgrund der gegensätzlichen Randbedingungen – die Reduzierung der Entwicklungskosten und der Entwurfszeiten einerseits sowie die Gewährleistung der Korrektheit des Designs andererseits – ergibt. Hierzu existieren bereits verschiedene Methoden, wie z.B. das *Virtual Prototyping* und das *Rapid Prototyping*.

Werden das Virtual Prototyping und das Rapid Prototyping genau betrachtet, so ist zu erkennen, dass sich beide Konzepte nicht gegenseitig widersprechen, sondern sich ergänzen. Aus dieser Erkenntnis heraus entstand die Idee, beides miteinander zu einer gemeinsamen Entwurfsmethode zu vereinigen und somit eine effiziente Lösung für das Überprüfen der Korrektheit des Designs zu finden.

In der vorliegenden Arbeit werden beide Methoden diskutiert und bewertet. Aufbauend auf dieser Bewertung wird die Kombination beider Methoden zu einer neuen vorgestellt, wobei die Schwächen des Virtual Prototypings durch die Stärken des Rapid Prototypings ausgeglichen werden. Dies führt zu der Vorstellung einer inkrementellen virtuell-realen (V/R) Entwurfsmethode.

Mittels einer Beispielimplementation wird gezeigt, inwieweit diese Methode auf aktuellen Simulationsrechnern umsetzbar ist. Desweiteren wird demonstriert, wo die technischen Grenzen hinsichtlich maximaler Modellkomplexität bei der verwendeten Echtzeitsimulation und bei den unvermeidlichen Verzögerungen der notwendigen Schnittstellen zwischen virtuellen und realen Systemteilen liegen.

Die Einsatzfähigkeit der hier geschaffenen Realisierung und die Nutzbarkeit des vorgestellten V/R-Entwurfsablaufs werden abschließend anhand von Beispielen untermauert.

#### **Schlagworte**

Echtzeit-Simulation

Entwurfsmethode

Eingebettete Systeme

Softwareintensive Systeme

#### **Abstract**

Modern systems of the automobile, telecommunication and automation technology tend towards huge systems, contain mechatronic components and so-called embedded control units (ECU). These ECUs control the mechanical components and therefore leads to software extensive systems. Interaction via communication networks, is responsible for the bloat of the software complexity.

Developers have to close the increasing gap between minimizing design costs and time market on one hand, while they still have to assure the correctness of the design on the other hand. Existing methods are for example Virtual Prototyping and Rapid Prototyping which have several disadvantages if they are used on its own. The combination of Virtual- and Rapid Prototyping minimize these disadvantages and direct to an incremental virtual-real (V/R) design method.

The aim of this work is to discuss the advantages and disadvantages of both methods and how to combine them by using a proof of concept implementation of a hard real time simulation environment. It is shown, how this design method is practically realizable on a todays industrial personal computer.

The maximum complexity of the models to gain real time is analyzed as well as and the unavoidable delays by interfacing the virtual and the real parts of the system.

The practical usablility of the introduced V/R design method is shown successfully by means of real examples.

#### **Keywords**

real time simulation

design flow

embedded systems

software extensive systems

# Inhaltsverzeichnis

| 1 | Einf | ührung   | in die Themenstellung                                           | 1 |

|---|------|----------|-----------------------------------------------------------------|---|

|   | 1.1  | Übersi   | cht über diese Arbeit                                           | 3 |

| 2 | Star | nd der ' | Technik                                                         | 5 |

|   | 2.1  |          | legende Begriffe                                                | 5 |

|   |      | 2.1.1    | Die Domäne                                                      |   |

|   |      | 2.1.2    | Der Systembegriff                                               |   |

|   |      | 2.1.3    | Das Aktorkonzept                                                |   |

|   |      | 2.1.4    | Echtzeitbetriebssysteme                                         |   |

|   |      | 2.1.5    | Unterscheidung: Entwurfsmethoden, -techniken und -prozesse      |   |

|   |      | 2.1.6    | Eingebettete Systeme                                            |   |

|   | 2.2  |          | rfsmethoden und Techniken                                       |   |

|   | 2.2  | 2.2.1    | Hardware-Software Codesign                                      |   |

|   |      | 2.2.2    | Interface-Based System Design                                   |   |

|   |      | 2.2.3    | Model Driven Architecture                                       |   |

|   |      | 2.2.5    | 2.2.3.1 Techniken zur Model Driven Architecture                 |   |

|   |      | 2.2.4    | Rapid Prototyping                                               |   |

|   |      |          | 2.2.4.1 Techniken zum Rapid Prototyping                         |   |

|   |      | 2.2.5    | Virtual Prototyping                                             |   |

|   |      | 2.2.0    | 2.2.5.1 Techniken zum Virtual Prototyping                       |   |

|   | 2.3  | Model    | lierungsmethoden                                                |   |

|   | 2.0  | 2.3.1    | Single-Language Ansätze                                         |   |

|   |      | 2.3.2    | Multi-Language Ansätze                                          |   |

|   | 2.4  | _        | ationsmethoden                                                  |   |

|   |      | 2.4.1    | Kontinuierliche Simulation                                      |   |

|   |      | 2.4.2    | Diskrete Simulation                                             |   |

|   |      |          | 2.4.2.1 Ereignisgesteuerte Simulation (Event-Driven Simulation) |   |

|   |      |          | 2.4.2.2 Zeitgesteuerte Simulation (Time-Driven Simulation)      |   |

|   |      | 2.4.3    | Hybride Simulation                                              |   |

|   |      | 2.4.4    | Cosimulation                                                    |   |

|   |      | 2.4.5    | Echtzeitsimulation                                              |   |

|   |      |          | 2.4.5.1 Mixed-Reality Simulation:                               |   |

|   |      | 2.4.6    | Emulation                                                       |   |

|   | 2.5  |          | ng der Simulation beim Test von Prototypen                      |   |

|   | 2.6  |          | right and Tucommonfoccume                                       |   |

VIII Inhaltsverzeichnis

| 3 | Lösı  | ingskonzept und Voraussetzungen                                               | 39    |

|---|-------|-------------------------------------------------------------------------------|-------|

|   | 3.1   | Der inkrementelle $V/R$ -Entwurfsablauf                                       |       |

|   |       | 3.1.1 Modellvalidierung über Cross Checking                                   |       |

|   | 3.2   | Notwendige Voraussetzungen                                                    | . 44  |

| 4 | Real  | lisierung der inkrementellen Entwurfsmethode                                  | 47    |

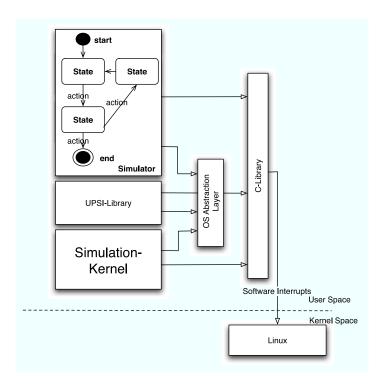

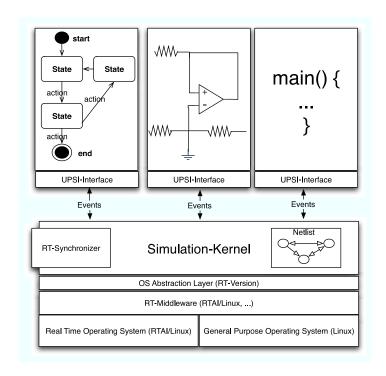

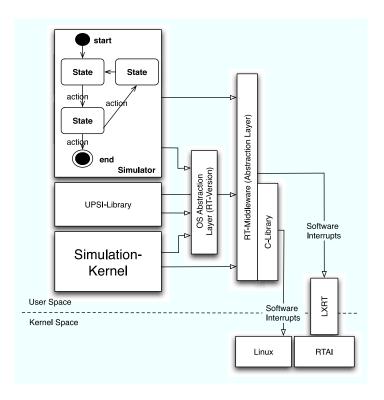

|   | 4.1   | Cosimulationsumgebung ClearSim-MultiDomain                                    | . 47  |

|   |       | 4.1.1 Der Simulations-Kernel und die Simulationsmodule                        |       |

|   |       | 4.1.2 Das "Universal Portable Simulation Interface" (UPSI)                    |       |

|   |       | 4.1.3 Die Betriebssystem-Abstraktionsschicht                                  |       |

|   | 4.2   | ClearSim-MultiDomain: gemischt virtuell-reale Systemsimulation                |       |

|   |       | 4.2.1 Echtzeitbetriebssystem RTAI/Linux                                       |       |

|   |       | 4.2.2 Hart-Echtzeitfähige Umgebung                                            |       |

|   |       | 4.2.3 Middleware für allgemeine Echtzeitbetriebssysteme                       |       |

|   |       | 4.2.3.1 Realisierung des I/O-Managements in der RT-Middleware                 |       |

|   |       | 4.2.3.2 Memory Management in einer RT-Umgebung                                |       |

|   |       | 4.2.3.3 Transparente RT-Abstraktionsschicht                                   |       |

|   |       | 4.2.5 Schnittstelle zwischen virtuellem und realem System bei zeitgenauer Sy- | . 04  |

|   |       | stemsimulation                                                                | . 66  |

| 5 | Valid | dierung des Konzeptes                                                         | 69    |

| 3 | 5.1   | Validierung der Umgebung für die Echtzeitsimulation                           |       |

|   | 5.2   | Validierung des Interfaces zwischen dem virtuellen und realen System          |       |

|   | 5.3   | Zusammenfassung                                                               |       |

|   |       |                                                                               |       |

| 6 |       | nersage der maximalen Modellkomplexität für eine harte Echtzeitsimulation     | 81    |

|   | 6.1   | Grundlegende Zusammenhänge                                                    |       |

|   | 6.2   | Zusammenfassung                                                               | . 88  |

| 7 |       | vendungsbeispiele                                                             | 89    |

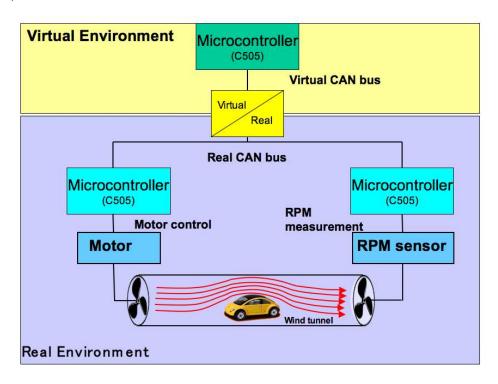

|   | 7.1   | Beispiel 1: Regelung eines Windkanals                                         |       |

|   |       | 7.1.1 Phase 1: Aufbau und Simulation des virtuellen Prototypen                |       |

|   |       | 7.1.2 Phase 2: Anschließen des realen Windkanals an die Simulation            |       |

|   |       | 7.1.3 Phase 3: Anschluss des virtuellen Regelcontrollers über den CAN-Bus     |       |

|   | 7.0   | 7.1.4 Phase 4: Ausführen des Regelprogramms auf dem realen Controller         |       |

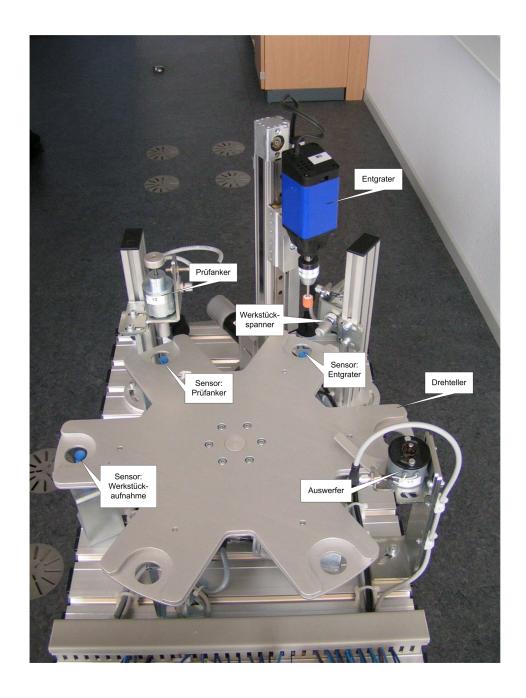

|   | 7.2   | Beispiel 2: Steuerung einer industriellen Fertigungsanlage                    |       |

|   |       | 7.2.2 Phase 2: Übergang zum realen Prototypen                                 |       |

|   |       | 7.2.3 Phase 3: Validierung des Modells der Fertigungsanlage                   |       |

|   |       | 7.2.4 Phase 4: Implementierung des AWL-Programms für die Siemens-SPS          |       |

|   |       | 7.2.5 Abschließende Überprüfung des AWL-Programms                             |       |

|   | 7.3   | Zusammenfassung                                                               |       |

| 8 | Zusa  | ammenfassung und Ausblick                                                     | 105   |

|   |       |                                                                               |       |

| 9 | Anh   | _                                                                             | 107   |

|   | 9.1   | Index                                                                         | . TAQ |

| Inhaltsverzeich | nis | IX |

|-----------------|-----|----|

|                 |     |    |

Literaturverzeichnis 111

X Inhaltsverzeichnis

# Abbildungsverzeichnis

| 2.1  | Autbau eines Gesamtsystems                                                     | 6  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | Beispiel eines allgemeinen Entwurfablaufs                                      | 10 |

| 2.3  | Hardware/Software Codesign                                                     | 12 |

| 2.4  | Model Driven Architecture                                                      | 13 |

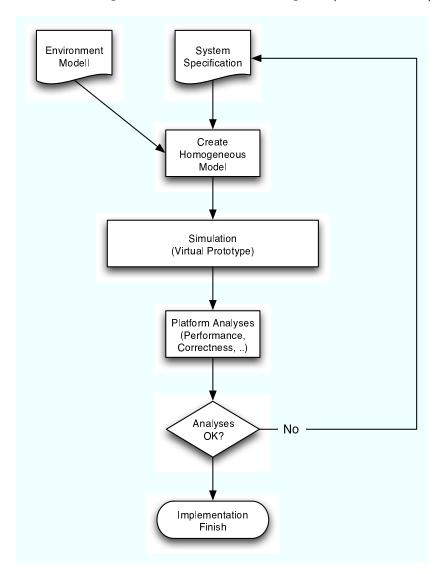

| 2.5  | Virtual Prototyping mit homogener Modellsimulation (Single-Language Ansatz) .  | 19 |

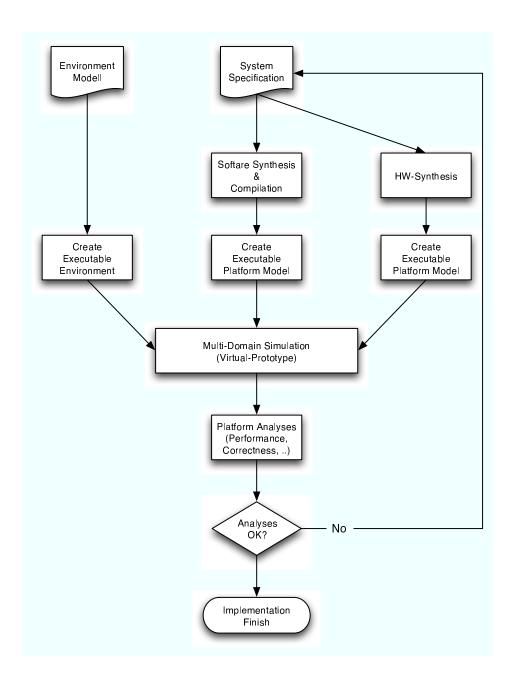

| 2.6  | Virtual Prototyping mit heterogener Modellsimulation (Multi-Language Ansatz) . | 20 |

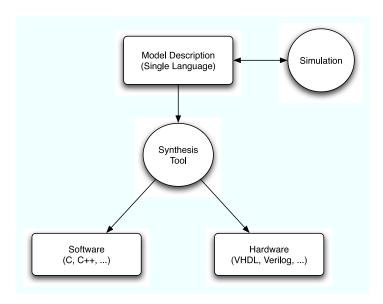

| 2.7  | Single-Language Ansatz                                                         | 23 |

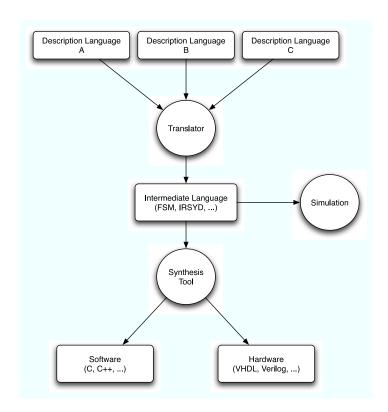

| 2.8  | Multi-Language Ansatz mit gemeinsamer Zwischensprache                          | 25 |

| 2.9  | Multi-Language Ansatz ohne gemeinsame Zwischensprache                          | 25 |

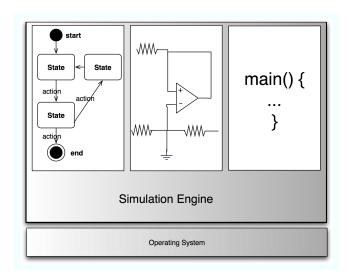

| 2.10 | Single-Engine Simulation                                                       | 30 |

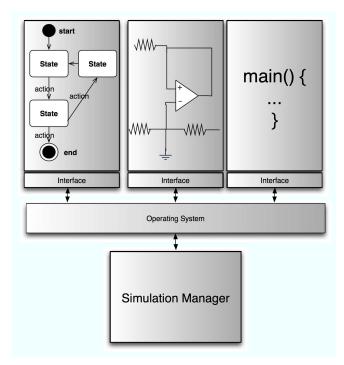

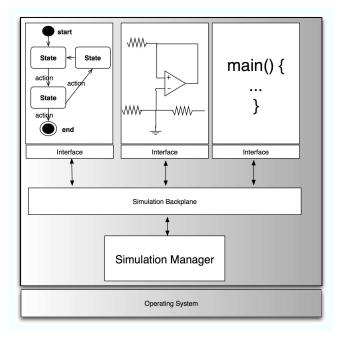

| 2.11 | Multi-Engine Simulation                                                        | 31 |

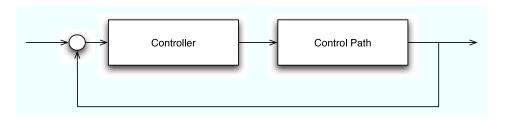

| 2.12 | Regelkreis                                                                     | 34 |

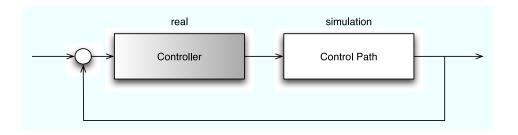

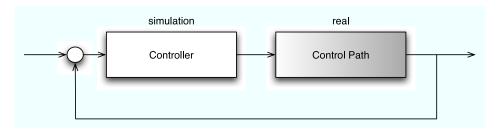

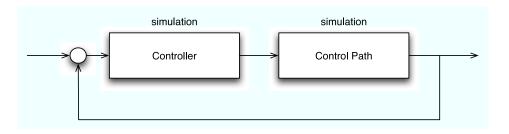

|      | Hardware-in-the-loop                                                           |    |

|      | Control-prototyping                                                            |    |

|      | Software-in-the-loop                                                           |    |

|      | Beispiel eines komplexen rückgekoppelten Systems                               | 36 |

| 3.1  | Top-Down Entwurfsablauf mit Multi-Domain Simulation                            | 40 |

| 3.2  | Inkrementeller Übergang von einem virtuellen zu einem realen Prototypen        | 41 |

| 3.3  | Beispiel des Cross Checking anhand der Steuerung einer Industrieanlage         | 43 |

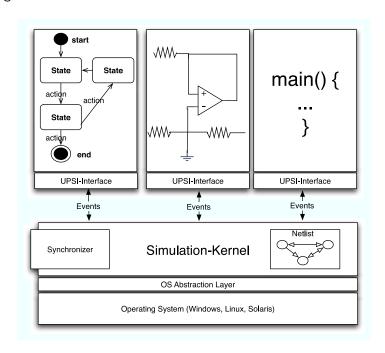

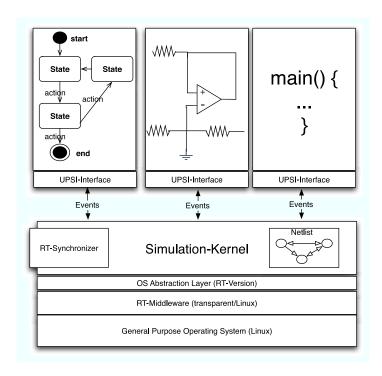

| 4.1  | Grundsätzlicher Aufbau von ClearSim-MultiDomain                                | 48 |

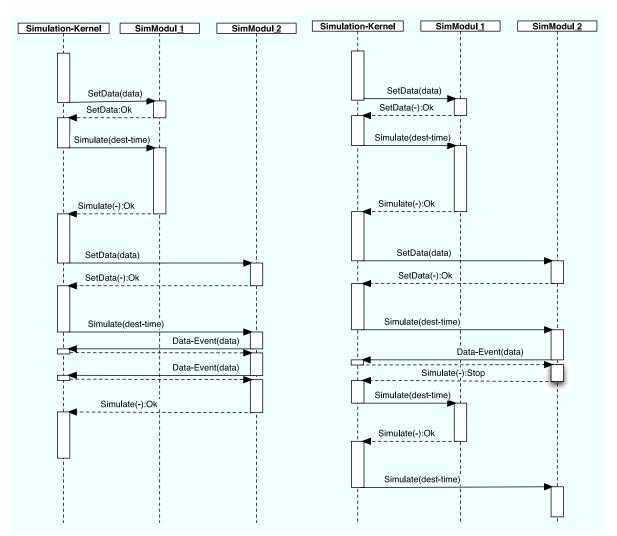

| 4.2  | Beispiele des Kernel-Scheduling                                                | 49 |

| 4.3  | UPSI I/O Abstraktionsschicht                                                   | 51 |

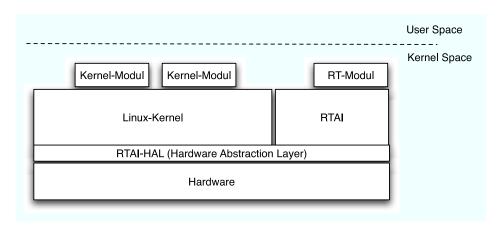

| 4.4  | Prinzipieller Aufbau von RTAI/Linux                                            | 53 |

| 4.5  | Aufbau der Echtzeiterweiterung RTAI/Linux mit LXRT                             | 54 |

| 4.6  | Darstellung der Systemzugriffe durch ClearSim-MultiDomain                      | 54 |

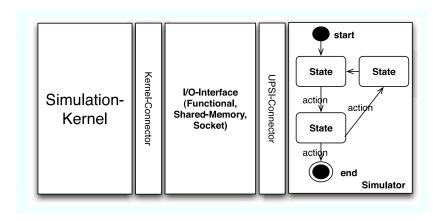

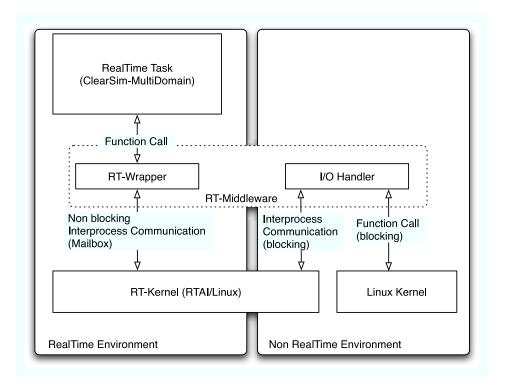

| 4.7  | Integration von ClearSim-MultiDomain in ein RT-Betriebssystem                  | 55 |

| 4.8  | Betriebssystemzugriffe werden korrekt über die RT-Middleware geleitet          | 56 |

| 4.9  | Prinzipieller Aufbau der RT-Middleware                                         | 59 |

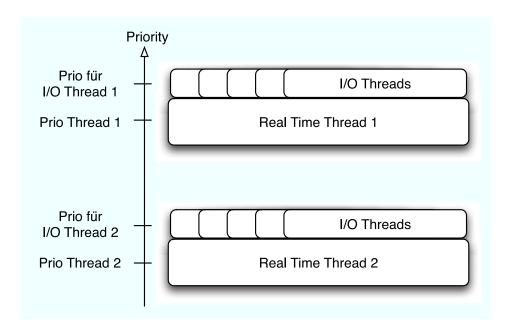

| 4.10 | Prioritäten bei der Real-Time Middleware                                       | 60 |

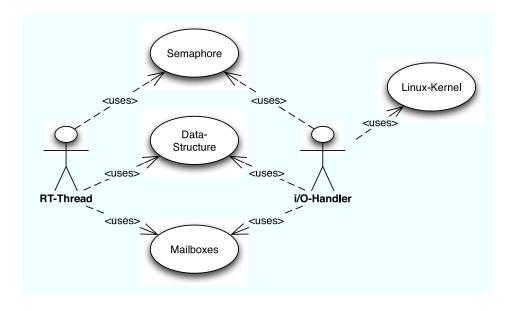

| 4.11 | Gemeinsame Elemente zwischen RT-Thread und I/O-Handler                         | 60 |

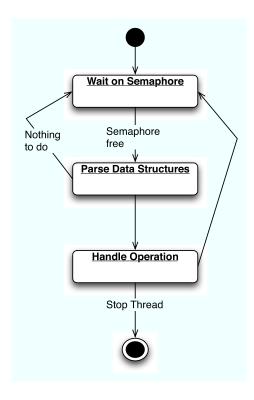

| 4.12 | Darstellung des prinzipiellen Ablaufs des I/O Handlers                         | 61 |

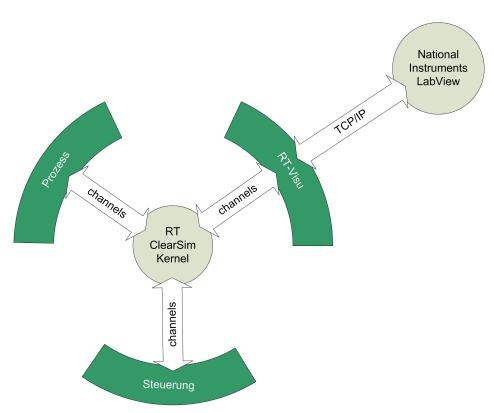

| 4.13 | Simulationsumgebung mit transparenter RT-Middleware                            | 64 |

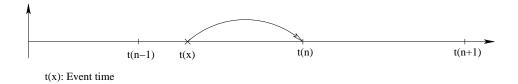

| 4.14 | Verzögerung der Ereignisse zum nächsten zeitsynchronen Punkt                   | 65 |

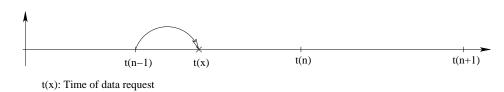

| 4.15 | Verzögerung der vorgespeicherten Ereignisse zum Zeitpunkt der Anforderung      | 65 |

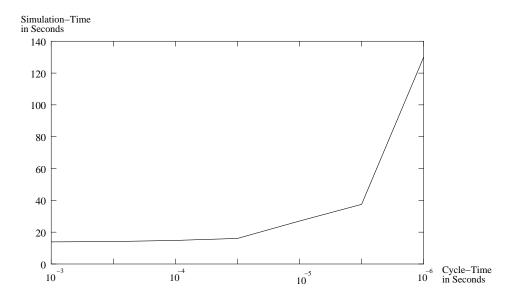

|      | Einfluss der Zykluszeit auf die Simulationszeit                                | 66 |

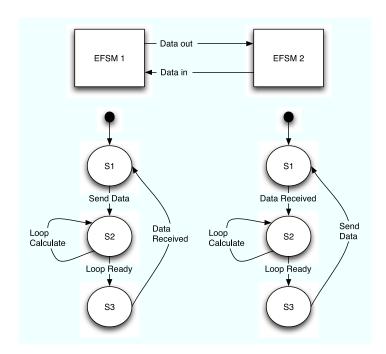

| 5.1  | Verwendete Zustandsmaschine für die synthetischen Tests                        | 70 |

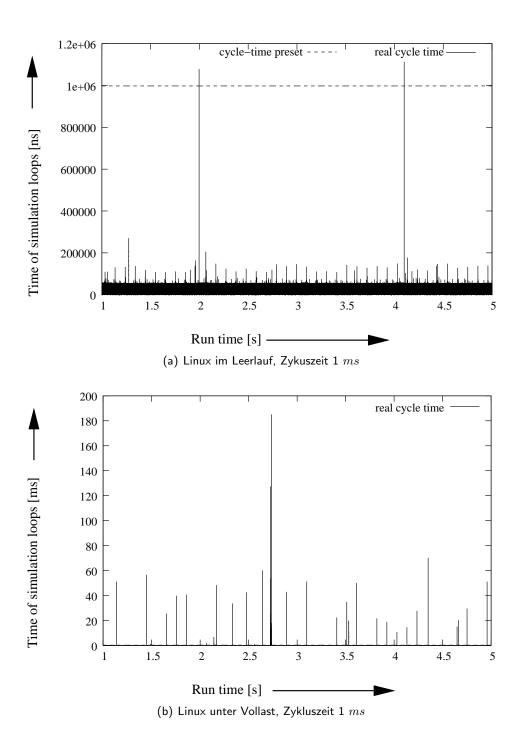

| 5.2        | Simulation in der nicht echtzeitfähigen ClearSim-Umgebung                                                                 | 72  |

|------------|---------------------------------------------------------------------------------------------------------------------------|-----|

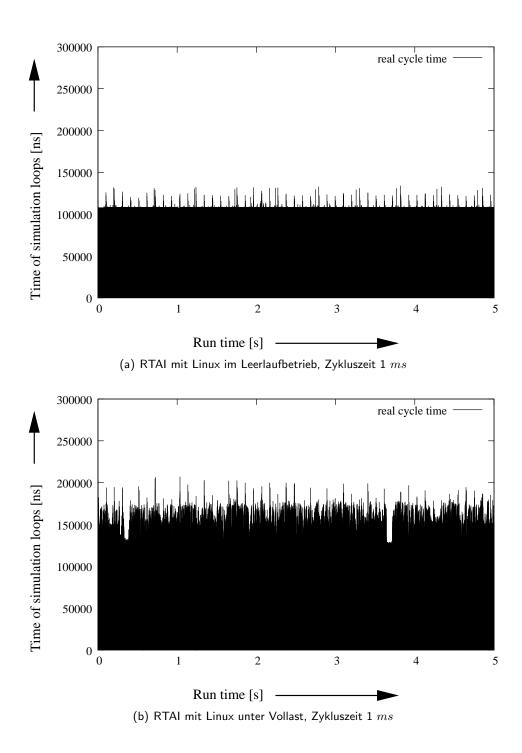

| 5.3        | Simulation von ClearSim-MultiDomain auf der Echtzeiterweiterung                                                           | 73  |

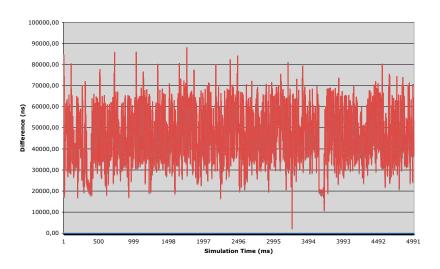

| 5.4        | Differenz zwischen den Messungen von Abbildung 5.3                                                                        | 74  |

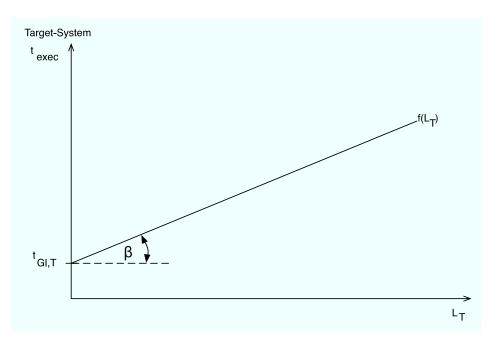

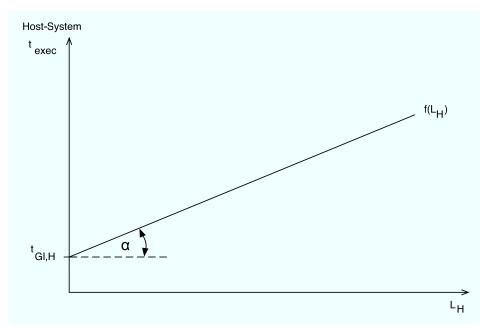

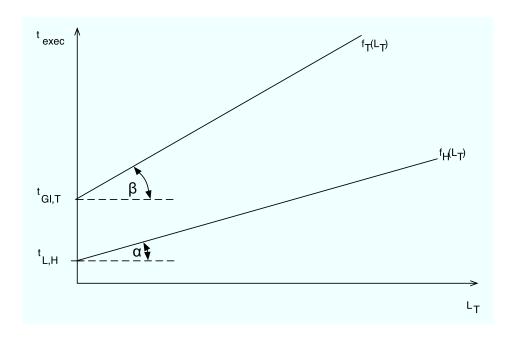

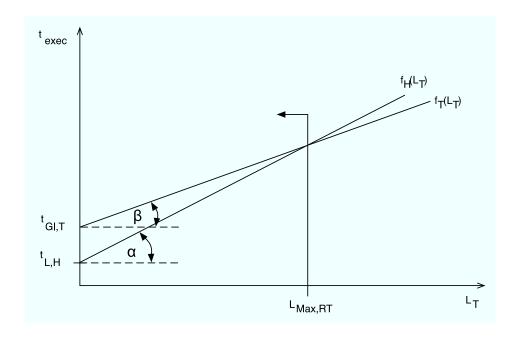

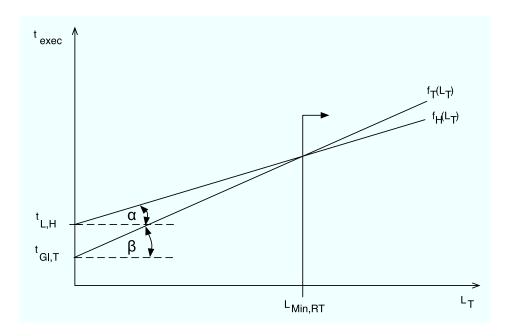

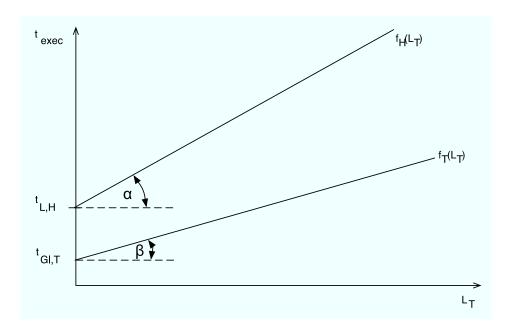

| 6.1        | Darstellung der Zusammenhänge zwischen Last und Ausführungszeit                                                           | 83  |

| 6.2        | Möglichkeit 1: $\alpha < \beta$ , $t_{GL,T} > t_{L,H}$                                                                    | 84  |

| 6.3        | Möglichkeit 2: $\alpha < \beta$ , $t_{GL,T} > t_{L,H}$                                                                    | 84  |

| 6.4        | Möglichkeit 3: $\alpha < \beta$ , $t_{GL,T} < t_{L,H}$                                                                    | 85  |

| 6.5        | Möglichkeit 4: $\alpha > \beta$ , $t_{GL,T} < t_{L,H}$                                                                    | 86  |

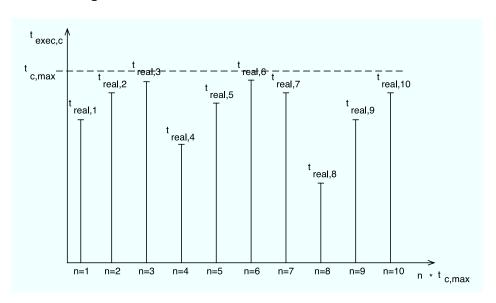

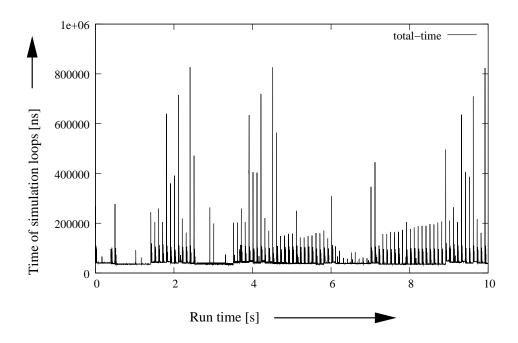

| 6.6        | Darstellung der Ausführungszeiten für jeden Zeitschritt in einer Echtzeitsimulation                                       | 87  |

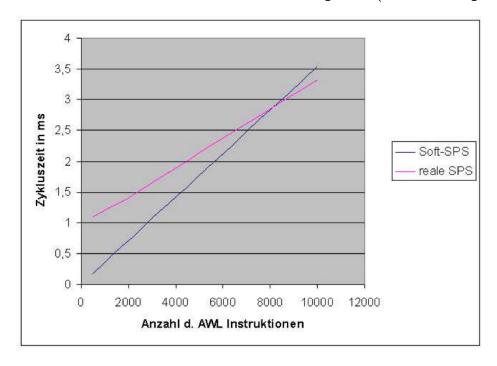

| 6.7        | Vergleich der Laufzeiten zwischen echter und simulierter SPS [32]                                                         | 88  |

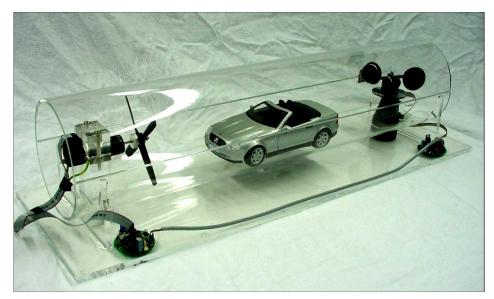

| 7.1        | Der Windkanal                                                                                                             | 90  |

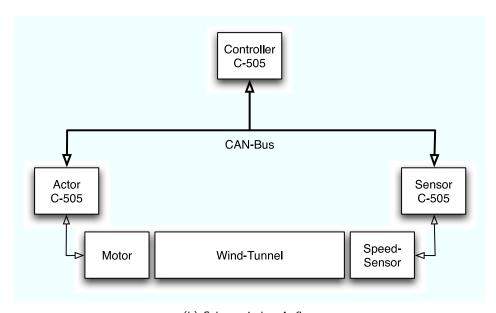

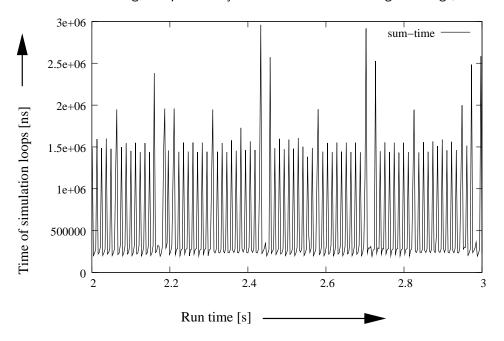

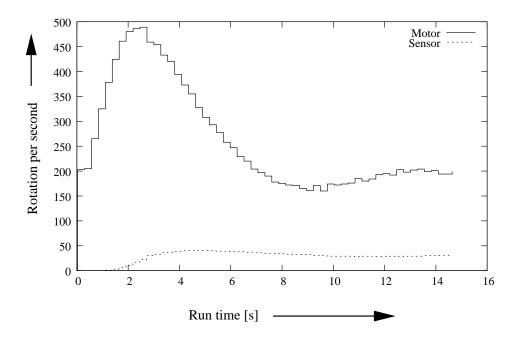

| 7.2        | Summe der Ausführungszeiten aller Modellkomponeten des virtuellen Prototypen                                              | 00  |

| 7.0        | (max. Zykluszeit: 3 ms, Rechner: 2 GHz Pentium 4)                                                                         | 92  |

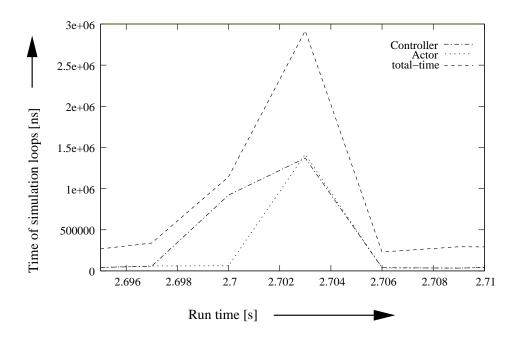

| 7.3        | Vergrößerter Ausschnitt mit maximaler Zykluszeit des Reglers (Controller) und der Motoransteuerung des Propellers (Actor) | 93  |

| 7.4        | Vergleich der Umdrehungszahlen zwischen Motor+Propeller und Windmesser im                                                 | 02  |

| <b>7</b> F | realen System                                                                                                             | 93  |

| 7.5        | Mixed Prototype: Nur der Regelcontroller ist in der Simulation verblieben                                                 | 94  |

| 7.6        | Vergleich der Windgeschwindigkeiten zwischen einer komplett virtuellen und einer                                          | ٥٦  |

| 7 7        | gemischten Simulation                                                                                                     |     |

| 7.7        | Die industrielle Fertigungsanlage von FESTO [32]                                                                          |     |

| 7.8        | Darstellung der Zykluszeiten in der Simulation                                                                            |     |

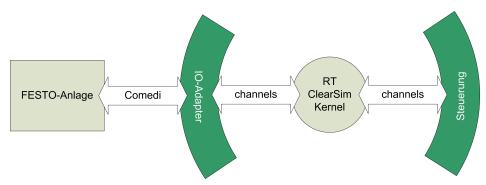

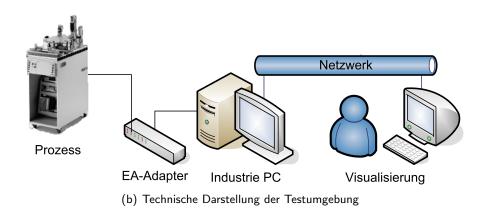

| 7.9        | Testumgebung für Mixed-Reality Simulationen [32]                                                                          |     |

| 7.10       | 0 0 1                                                                                                                     |     |

|            | Simulation der UML-Steuerung mit dem V/R-Interface                                                                        |     |

| 1.12       | Virtuelle Simulation der SPS und der Fertigungsanlage in Echtzeit                                                         | 102 |

## Häufig verwendete Abkürzungen

ABS ..... Anti Blockier System ASIC ..... Application Specific Integrated Circuit AWL ..... Anweisungsliste CAN ..... Controller Area Network CFSM ..... Co-design Finite State Machine COSYMA ..... Cosynthesis for Embedded Architectures Cx ..... C Extended DFG ..... Deutsche Forschungsgemeinschaft DIN ..... Deutsche Industrie Norm DLL ..... Dynamic Linked Library DVB-T ..... Digital Video Broadcasting - Terrestrial ECU ..... Embedded Control Units ESP ..... Elektronisches Stabilitätsprogramm FPGA ..... Field Programmable Gate Array FSM ..... Finite State Machine GP-OS ..... General Purpose Operating System GPS ...... Global Positioning System GSM ...... Global System for Mobile Communication HIL ..... Hardware-in-the-Loop HW ..... Hardware I/O ..... Input/Output MDA ..... Model Driven Architecture MSC ..... Message Sequence Charts OS ..... Operating System PIM ..... Platform Independent Model PSM ..... Platform Specific Model R ..... Realtime-Faktor RT ..... Real Time RTAI ..... Real Time Application Interface RTL ..... Real Time Linux RTL ..... Register Transfer Layer SDL ..... Specification and Description Language SOC ..... System on a Chip SPS ..... Speicher Programmierbare Steuerung STL ..... Standard Template Library SUD ...... System Under Development SUT ...... System Under Test SW ..... Software UML ..... Unified Modeling Language

| UPSI Universal Portable Sir | iulation Interface |

|-----------------------------|--------------------|

|-----------------------------|--------------------|

V/R ......<u>V</u>irtual/<u>R</u>eal

XMI ..... XML Metadata Interchange XML .... Extensible Markup Language

# 1 Einführung in die Themenstellung

In Systemen der Automobil-, Telekommunikations- und Automatisierungstechnik steigt der Anteil eingebetteter Systeme drastisch an. Neben komplexer werdenden mechatronischen Komponenten ist ebenfalls ein zunehmender Einsatz von eingebetteten Steuerungen auf Basis von *Embedded Control Units* (ECU) zu verzeichnen. Diese steuern und überwachen nicht nur die mechatronischen Systemteile, sondern stehen untereinander in Verbindung und beeinflussen sich gegenseitig. Dies führt zu einer deutlichen Erhöhung der Komplexität und des prozentualen Anteils an Software innerhalb des Gesamtsystems.

Hinsichtlich der notwendigen Kostensenkungen und der immer kürzer werdenden Produktionszyklen (time to market) erhöht sich der Druck auf die Entwickler in zunehmendem Maße. Verschlimmernd kommt hinzu, dass immer mehr sicherheitsrelevante Komponenten durch softwarebasierte Systeme gesteuert oder geregelt werden müssen. Während vor einigen Jahren, beispielsweise in der Automobilindustrie, ECUs lediglich für einfache Aufgaben, wie z.B. die Steuerung der Scheibenwischer und der Zentralverriegelung, verwendet wurden, sind sie heute ebenfalls für das Anti-Blockiersystem (ABS), für die Fahrzeugstabilisierung (ESP) und für das korrekte Auslösen der Airbags zuständig. In naher Zukunft werden sie außerdem die komplette Steuerung des Fahrzeugs kontrollieren (x-by-wire), was bei Fehlfunktionen lebensbedrohliche Folgen haben könnte.

In Folge dessen ist der Entwickler in immer stärkerem Maße gezwungen, unterschiedliche Subsysteme in den Systementwurf einzubeziehen und vor allem die Einflüsse aufeinander zu prüfen und zu bewerten. Weiterhin hat dies aufgrund des Zeitdrucks oftmals vor der Verfügbarkeit einiger der realen Komponenten zu erfolgen, wodurch ein realer Aufbau des gesamten Systems erst zu einem sehr späten Entwurfszeitpunkt möglich wird und somit hohe Kosten für notwendige Änderungen entstehen.

In der Vergangenheit führten diese Randbedingungen in der Automobilindustrie gerade bei den Luxus-Modellen zu erheblichen Ausfällen, in die besonders viele dieser neuen und softwarebasierten Systemen integriert wurden. Die aktuelle Folge dieser Entwicklung ist, dass die Anzahl und Komplexität softwarebasierter Systeme entweder wieder reduziert oder zumindest nicht weiter erhöht werden, da sich die resultierende Gesamtkomplexität als nicht beherrschbar darstellt.

Im Flugzeugbau sind Systeme bereits erfolgreich und relativ störungsfrei im Einsatz, obwohl sie deutlich komplexer als heutige Kraftfahrzeuge sind, wenn z.B. die Technik eines modernen Airbus als Vergleich herangezogen wird. Es stellt sich somit die Frage, warum die offensichtlich funktionierenden Entwurfsmethoden der Flugzeugindustrie nicht verwendet werden, um auch in anderen Bereichen ähnliche Ziele zu erreichen. Die Antwort muss wohl lauten, dass ein Automobil, welches mit den Entwurfs- und vor allem den Testmethoden des Flugzeugbaus entworfen wäre, wahrscheinlich technisch einwandfrei funktioniert, aber bezüglich des Preises gegenüber konkurrierender Automobile kaum eine Chance hätte. Auch eine Mehrfachauslegung von sicherheitsrelevanten Systemkomponenten wäre nicht zu bezahlen.

Ein Entwickler hat somit einen Weg zu finden, um die Lücke zu schließen, die sich aufgrund der gegensätzlichen Randbedingungen – die Reduzierung der Entwicklungskosten und der Entwurfszeiten

einerseits sowie die Gewährleistung der Korrektheit des Designs andererseits - ergibt.

In der Praxis existieren hierzu verschiedene Ansätze, die versuchen, dieses Spannungsfeld aufzulösen. Diese Methoden und Techniken können erfolgreich demonstrieren, wie die Entwurfszeiten reduziert werden können. Um aber korrekte Implementationen zu erhalten, muss eine Verifikation oder Validierung des Entwurfs herangezogen werden. Während die *Verifikation* bei heterogenen Systemen sehr schwierig ist, wird in der Praxis üblicherweise auf die Validierung mittels *Simulation* oder auf praktische Tests anhand *realer Modelle* oder so genannter *Rapid-Prototypen* zurückgegriffen. Anhand möglichst vollständiger Testszenarien wird mit diesen Vorgehensweisen die Korrektheit des Designs überprüft.

Die Simulation heterogener Systeme konnte bereits mittels des so genannten Virtual Prototyping erfolgreich realisiert werden. Bei dieser Methode werden das zu entwickelnde System und die Umgebung in verschiedene Domänen (z.B. digitale und analoge Elemente, Software, usw.) zerlegt und jeweils das zeitliche sowie das funktionale Verhalten modelliert, was zu Beginn durchaus auf abstrakter Ebene geschehen kann und im Laufe des Entwurfsprozesses zunehmend konkretisiert wird. Die so modellierten Domänen können immer zu einem simulierbaren Gesamtsystem zusammengefügt werden, wodurch zu jedem Entwurfszeitpunkt eine sehr genaue Validierung des Prototyps ermöglicht wird. Weitere Vorteile dieser Methode liegen in der guten Beobachtbarkeit des Systemverhaltens und der prinzipiellen Möglichkeit, jegliche Art von Messeinflüssen herauszurechnen.

Diese Methode zeigt in der Praxis allerdings verschiedene Schwachpunkte, da sie sehr genaue und validierte Modelle verlangt und darüber hinaus eine Methodik für den Übergang zum realen System nicht vorsieht. Zeigt der angefertigte reale Prototyp später ein fehlerhaftes Verhalten, so wird es für den Entwickler sehr schwierig, dieses mit Hilfe seiner virtuellen Entwurfsumgebung aufzuklären.

Ein anderer Ansatz wurde mit dem *Rapid Prototyping* verfolgt. Bei dieser Methode wird der Modellierungsaufwand bewusst vermieden, indem die zu testende Software möglichst früh in eine reale Umgebung integriert wird. Modellierungsfehler der Software werden somit prinzipiell erkennbar, gleichzeitig werden aber Aussagen über die notwendige Leistungsfähigkeit der später einzusetzenden ECUs schwierig oder unmöglich, da diese nicht modelliert und somit auch nicht berücksichtigt werden. Ebenfalls werden verschiedene Fehlerquellen durch diese Methode nicht sichtbar, da das Rapid-Prototyping-System in den meisten Fällen auf einer anderen Hardware basiert als das spätere Zielsystem und somit Einflüsse der Target Toolchain (Codegenerator, Compiler, Bibliotheken) nicht in die Beurteilung der Korrektheit einfließen können.

Werden das *Virtual Prototyping* und das *Rapid Prototyping* genau betrachtet, so ist zu erkennen, dass sich beide Konzepte nicht gegenseitig widersprechen, sondern sich ergänzen. Aus dieser Erkenntnis heraus entstand die Idee, beides miteinander zu einer gemeinsamen Entwurfsmethode zu vereinigen und somit eine effiziente Lösung für das Überprüfen der Korrektheit des Designs zu finden.

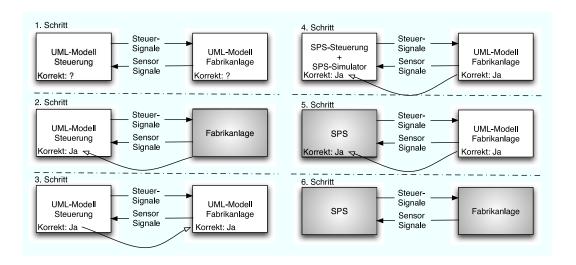

In der vorliegenden Arbeit werden beide Methoden diskutiert und bewertet. Aufbauend auf dieser Bewertung wird die Kombination dieser beiden Methoden zu einer neuen vorgestellt, wobei die Schwächen des Virtual Prototypings durch die Stärken des Rapid Prototypings ausgeglichen werden. Dies führt zu der Vorstellung einer inkrementellen virtuell-realen (V/R) Entwurfsmethode, die anhand einer Beispielimplementierung praktisch demonstriert wird.

Da das hier angesprochene Themengebiet naturgemäß sehr umfangreich und fragmentiert ist, wurde die folgende Analyse auf den Bereich der Entwicklung "softwareintensiver eingebetteter

Systeme" eingegrenzt, der den Hauptfokus dieser Arbeit darstellt. Der Entwurf von Hardware ist in dieser Betrachtung nur von untergeordneter Bedeutung und wird somit nur am Rande behandelt.

### 1.1 Übersicht über diese Arbeit

Im nachfolgenden Kapitel wird der Stand der Technik in dem oben skizzierten Umfeld – der Entwicklung softwareintensiver eingebetteter Systeme – dargelegt. Zum besseren Verständnis wird zu Beginn auf grundlegende Begriffe eingegangen, bevor mit der Vorstellung der Entwurfs-, Modellierungs- und Simulationsmethoden begonnen wird. Ergänzend zu den jeweiligen Methoden werden ebenfalls Entwurfstechniken aufgeführt und verglichen. Das Kapitel schließt mit einer zusammenfassenden Bewertung, in der diskutiert wird, inwieweit die vorgestellten Methoden für die oben beschriebene Aufgabenstellung befriedigende Lösungsansätze liefern und an welchen Stellen noch Bedarf an Verbesserung gesehen wird.

In Kapitel 3 werden die aus der Analyse resultierenden Anforderungen, in ein Lösungskonzept überführt, aus dem im Anschluss die notwendigen Voraussetzungen für die Realisierung der Beispielimplementierung formuliert werden.

Im Kapitel 4 werden die zur Realisierung notwendigen Aspekte weiter konkretisiert, indem sie in eine technische Realisierung übersetzt werden. Als Basis wird der im Institut für Systems Engineering, System- und Rechnerarchitektur entwickelte Systemsimulator ClearSim-MultiDomain für diese Arbeit herangezogen und hinsichtlich harter Echtzeitsimulation und der Realisierung von virtuell-realen Mischsystemen erweitert. Hierzu wird mit der Beschreibung des grundlegenden Aufbaus begonnen. Daraufhin werden die durchgeführten Änderungen und Erweiterungen erläutert in im Anschluss im Anschluss in Kapitel 5 validiert. In diesem Kapitel werden weiterhin die Eigenschaften und Randbedingungen des Systems mittels Messungen untersucht. Eine zusammenfassende Analyse der aus den gewonnenen Erkenntnissen resultierenden Anwendungsmöglichkeiten und Grenzen dieser Realisierung schließt das Kapitel ab.

Aufgrund der Tatsache, dass eine Echtzeitsimulation eine anspruchsvolle Zielsetzung ist und von den verschiedensten Randbedingungen, wie z.B. der Komplexität der simulierten Modelle und der Leistungsfähigkeit des Simulationssystems, abhängt, wird in *Kapitel 6* die Fragestellung diskutiert und beantwortet, inwieweit die maximal zulässige Modellkomplexität für eine erfolgreiche Simulation unter Echtzeitbedingungen vorhersagbar ist. Anschließend wird mittels zweier Anwendungsbeispiele, die praktische Nutzbarkeit des Systems in *Kapitel 7* demonstriert. Die Beispiele sind jeweils so gewählt, so dass sie die Aspekte des hier vorgestellten inkrementellen Entwurfsablaufs inklusive des so genannten Cross Checkings demonstrieren und den Vorteil gegenüber den herkömmlichen Ansätzen unterstreichen.

Abgeschlossen wird diese Arbeit mit einer Zusammenfassung, einer abschließende Bewertung sowie einem Ausblick auf zukünftige Erweiterungen in *Kapitel 8*.

### 2 Stand der Technik

Im Folgenden soll – nach einer kurzen Einführung grundlegender Begriffe – mit einer Darstellung der gegenwärtigen Entwurfsmethoden und -techniken begonnen werden. Anschließend wird in Abschnitt 2.3 auf bekannte Modellierungsmethoden und -techniken eingegangen, die das Fundament für eine korrekte Realisierung der anschließend in Abschnitt 2.4 dargelegten Simulationsmethoden legen, gefolgt von einer Darstellung der Nutzungsmöglichkeiten der Simulation beim Test von Prototypen (Abschnitt 2.5). Abschließend werden in Abschnitt 2.6 die wesentlichen Punkte dieses Kapitels zusammengefasst und beurteilt.

### 2.1 Grundlegende Begriffe

Im Folgenden werden zunächst die grundlegenden Begriffe erläutert, die zum Verständnis der vorliegenden Arbeit entscheidend sind.

#### 2.1.1 Die Domäne

Unter einer Anwendungsdomäne, häufig auch verkürzend Domäne, versteht man in der Informatik und insbesondere in der Softwaretechnik ein abgrenzbares Problemfeld des täglichen Lebens oder – etwas spezieller – einen bestimmten Einsatzbereich für Computersysteme oder Software. Anwendungsdomänen stellen typischerweise sehr spezielle Anforderungen an ein technisches System, welches zur Bewältigung der domänenspezifischen Aufgaben und Probleme eingesetzt werden soll. Diese Anforderungen fließen insbesondere im Rahmen der Anforderungsanalyse, die einer Systementwicklung vorausgeht, und während des Entwurfs des Systems in den Entwicklungsprozess ein und bestimmen maßgeblich die Modellbildung, die der späteren Realisierung zu Grunde liegt. Der Begriff wird häufig dann eingesetzt, wenn es für den betreffenden Einsatzbereich eine Vielzahl ähnlicher Systeme gibt, die allesamt die Anforderungen der Domäne umsetzen müssen. Anwendungsdomänen eignen sich daher gut für die Wiederverwendung von Architekturen und Systemkomponenten [4].

#### 2.1.2 Der Systembegriff

Im Allgemeinen wird als *System* ein aus Einzelteilen bestehendes Ganzes bezeichnet (siehe Brockhaus). Was unter einem System genau verstanden wird, hängt sehr stark von dem jeweiligen Anwendungsfall ab, daher kann es keine befriedigende allgemeingültige Definition geben.

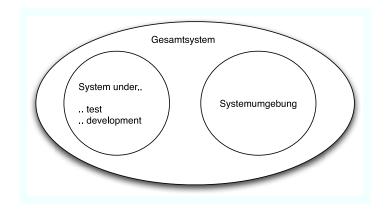

Bei den verschiedenen Entwurfsmethoden wird dieser Begriff oft zur Bezeichnung des Objektes verwendet, welches im Interesse des Entwicklers liegt und von der *Systemumgebung* unterschieden wird. In diesem Fall wird von dem *System under test* (SUT) bzw. *System under development* (SUD)

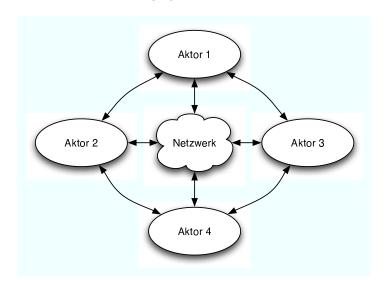

gesprochen. Beide befinden sich zueinander in einer Wechselbeziehung, indem zwischen ihnen Informationen ausgetauscht werden. Beide bilden zusammen als *Gesamtsystem* ein vollständiges Ganzes (siehe Abbildung 2.1).

Abbildung 2.1: Aufbau eines Gesamtsystems

Auch wenn das Entwurfsziel sich ausschließlich auf das zu entwickelnde System bezieht, kann ein Systemtest nur anhand eines Gesamtsystems realisiert werden. Somit muss die Umgebung ebenfalls berücksichtigt werden. Hierzu existieren die verschiedensten Konzepte und Methoden, die im Kapitel 2.2 näher erläutert werden.

In unserem Kontext besteht das Gesamtsystem in der Regel aus technischen Komponenten. Woraus diese Komponenten aber bestehen, kann höchst unterschiedlich sein:

Während sich beim Hardware/Software Codesign das System ausschließlich auf digitale Komponenten und Software bezieht, kann dieser Begriff bei anderen Entwurfsansätzen, wie z.B. dem Multi-Domain Ansatz, sehr viel umfangreicher gefasst sein. Als weitere Domänen sind z.B. analoge oder auch stochastische Verhaltensmodelle denkbar, die mit den anderen Domänen in ständiger Wechselbeziehung stehen.

Somit ist festzuhalten, dass sich der Umfang und die Komplexität eines Systems und dessen Umgebung stark unterscheiden kann, je nachdem was genau im Interesse des Entwicklers liegt und somit beschrieben werden muss!

#### 2.1.3 Das Aktorkonzept

Das Aktorkonzept oder Aktormodell wurde unter anderem durch Lisp, Simula und frühere Smalltalk Versionen inspiriert und 1973 zum ersten mal von Carl Hewitt et al. formuliert. Dieses Modell beschreibt verteilte, konkurrierende Systeme, indem sie als so genannte Aktoren dargestellt werden, die untereinander Nachrichten austauschen. Erhält ein Aktor eine Nachricht, so kann es lokale Entscheidungen treffen, neue Aktoren erzeugen und weitere Nachrichten aussenden. Weiterhin kann der Empfang einer Nachricht die Art der Verarbeitung einer zukünftigen Nachricht beeinflussen. Ein Aktor hat somit ein Gedächtnis.

Dieses Konzept beschreibt einen Paradigmen-Wechsel, der sich zu dieser Zeit in der Informatik vollzog. Konkurrierende Computermodelle verwendeten zu dieser Zeit globale Zustände, die über

gemeinsamen Speicher (Shared Memory) untereinander geteilt wurden und somit eine nichtdeterministische globale Zustandsmaschine (nondeterministic global state machine) darstellten.

Im Gegensatz hierzu zeichnet sich das Aktorkonzept durch folgende Aspekte aus:

- Es existieren keine globalen Zustände.

- Es herrscht Lokalität bezüglich der Nachrichtenverarbeitung, indem ein Aktor nur Nachrichten an andere Aktoren schicken kann, die durch Absender in empfangenen Nachrichten bekannt wurden, die selbst erzeugt wurden oder deren Adresse durch die Verarbeitung von Nachrichten errechnet werden konnten.

- Ebenfalls besteht Lokalität, indem keine simultanen Änderungen in mehreren Aktoren möglich sind, wie z.B. bei den Petri-Netzen, bei der so genannte Token simultan an mehreren Orten entfernt werden können.

- Es wird das Konzept der Kompositionalität (Compositionality) verwirklicht, also die Möglichkeit des Zusammenfügens von Aktor-Modellen zu größeren Strukturen, was die Grundlage für Modularität darstellt.

Ungefähr 8 Jahre nach der ersten Veröffentlichung, wurde das Aktorkonzept durch Will Clinger in seiner Domänen-Theorie (Domain Theory) erstmals als mathematisch beschreibbares Modell formuliert [4].

#### 2.1.4 Echtzeitbetriebssysteme

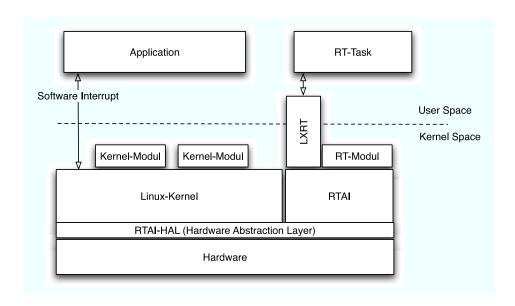

Grundsätzlich kann zwischen zwei Arten von Echtzeitbetriebssystemen unterschieden werden. Es sind hier einerseits die homogenen Echtzeitbetriebssysteme und andererseits die Betriebsystem-Erweiterungen.

Betriebssystem-Erweiterungen sind Systeme, bei denen ein Standard-Betriebssystem (general purpose operating system, GP-OS), wie Windows oder Linux, durch eine Komponente ergänzt wird, die dem Entwickler ermöglicht, hart-echtzeitfähige Prozesse zu verwenden. Hierbei handelt es sich in der Regel um eine Software, welche die eingesetzte Hardware gegenüber dem GP-OS kapselt, die Interrupts virtualisiert und einen eigenen Echtzeitscheduler einsetzt, der vom GP-OS unabhängig ist. Dieser Scheduler ist so konzipiert, dass alle Realtime-Prozesse höher priorisiert sind als das GP-OS selbst.

**Homogene Echtzeitbetriebssysteme** sind Betriebssysteme, die vollständig und homogen echtzeitfähig konzipiert wurden. Somit gibt es bei diesen Systemen nicht die oben beschriebene Dualität.

Typische Vertreter der Betriebssystem-Erweiterungen sind "Real Time Linux" (RTL) und das "Real-Time Application Interface" (RTAI) für Linux und OnTime, sowie RTX für Windows NT. Bei den homogenen Betriebsystemen sind z.B. QNX, RTOS-UH, Nucleus, VxWorks, OS-9 und LynxOS zu nennen.

Beide Varianten ermöglichen prinzipiell ähnlich gute Echtzeiteigenschaften und bieten neben eigenen API's (Application Programming Interface) ebenfalls POSIX [54]-ähnliche Programmierinterfaces an. Der Vorteil der Erweiterungen liegt darin, dass gleichzeitig mit dem Einsatz von Echtzeitprozessen die Möglichkeit besteht, das System wie gewohnt einzusetzen, da es sich gegenüber Standardapplikationen identisch zu einer unmodifizierten Variante verhält. Bei den homogenen Systemen ist im Gegensatz hierzu eine unterschiedlich starke Einschränkung bezüglich der Kompatibilität gegenüber Standardapplikationen festzustellen. Weiterhin sind alle dem Autor bekannten homogenen Lösungen kommerziell und nicht quelloffen, was die Einflussnahme der Entwickler auf das System deutlich einschränkt.

Bei den Erweiterungen wird zumindest bei den linuxbasierten Lösungen die Quelloffenheit garantiert. Somit weisen sie eine sehr hohe Dynamik bezüglich Weiterentwicklung und Unterstützung verschiedenster Hardware auf. Die Dualität der Erweiterungen stellt für den Entwickler allerdings eine nicht zu unterschätzende Komplexität und Gefahr dar:

Da diese Dualität in der zu entwickelnden Software ebenfalls zu berücksichtigen ist, muss der Programmierer die Unterscheidung von Programmteilen mit bzw. ohne Echtzeitanforderungen programmtechnisch korrekt umsetzen. Hierzu kann schon die Verwendung eines einfachen "printf()" anstatt z.B. eines "rt\_printf()" theoretisch zu einer Nichtvorhersagbarkeit der Zeitschranken führen. Weiterhin sind standardmäßig keine Lösungen vorgesehen, aus den Programmteilen mit harter Echtzeitforderung notwendige Operationen wie Datei- oder Socketkommunikation durchzuführen, was bei den homogenen Echtzeibetriebssystemen üblicherweise einfach möglich ist.

#### 2.1.5 Unterscheidung: Entwurfsmethoden, -techniken und -prozesse

Zum besseren Verständnis der folgenden Kapitel ist die genaue Unterscheidung zwischen "Entwurfsmethoden", "Entwurfstechniken" und "Entwurfsprozessen" wichtig:

Bei einer Entwurfsmethode handelt es sich um ein prinzipielles methodisches Vorgehen, ohne die technische Realisierung zu betrachten. Eine Entwurfstechnik stellt die technischen Grundlagen zur Realisierung einer Entwurfsmethode dar, wobei der Entwufsprozess den genauen Ablauf des Entwurfs inklusive der Benutzung und Kombination der Tools beschreibt.

#### 2.1.6 Eingebettete Systeme

Unter einem eingebetteten System versteht man ein spezialisiertes (special purpose) Computersystem, welches ein anderes System kontrolliert, von dem es komplett umlossen ist. Ein eingebettetes System erfüllt im Gegensatz zu einem allgemeinen (general purpose) Computersystem ausschließlich eine spezielle Aufgabe [4].

#### 2.2 Entwurfsmethoden und Techniken

Das Design eines Produktes kann mittels verschiedener Abstraktionsebenen beschrieben werden, wobei jede an der Entwicklung beteiligte Gruppe entsprechend ihrer Aufgabe eine unterschiedliche Perspektive einnimmt. Im Allgemeinen wird während des Entwurfsprozesses schrittweise die Abstraktionsebene von einer reinen Verhaltensbeschreibung über eine gröbere strukturelle Beschreibung bis hin zu einer exakten physikalischen Repräsentation präzisiert. Zum Schluss des Prozesses

liegt somit das fertige Produkt in einer der verwendeten Technologie und den vorher spezifizierten Randbedingungen entsprechenden Beschreibung vor, die keinen Spielraum für Interpretationen oder Ungenauigkeiten mehr enthält.

Diese Methode kann als allgemeingültig angesehen werden und wird häufig auch als "Top-Down Approach" bezeichnet [22].

Da der Mensch nur ein begrenztes Maß an Komplexität wirklich erfassen kann, sind ihm beim Abstieg der Abstraktionsebenen und dem damit verbundenen Anstieg an Komplexität Grenzen gesetzt. Generell besteht die Gefahr, dass ab einer gewissen Komplexitätsgrenze die Übersicht verloren geht und sich somit Probleme oder Fehler in das Design einschleichen, die nur schwer zu finden sind, da die Entwickler überfordert sind. Lösungsansatz für zu hohe Komplexität ist somit die Aufteilung eines Systems in viele, weniger komplexe Einzelteile, die noch von den Entwicklern beherrscht werden können (so genanntes "Teile und Herrsche" Prinzip [17]).

Die oben bezeichnete, allgemeingültige Entwurfsmethode kann sich in der Praxis in Variationen darstellen, die von Professor Daniel D. Gajski in drei verschiedene Gruppen aufgeteilt wurden [18]:

- 1. Capture-and-Simulate

- 2. Describe-and-Synthesize

- 3. Specify, Explore and Refine

Bei frühen Entwurfsmethoden wurde auf den hohen Abstraktionsebenen ausschließlich mit natürlichsprachlichen Beschreibungen gearbeitet, um die Eigenschaften und das gewünschte Verhalten – also die Spezifikation – des zu entwickelnden Systems zu beschreiben. Automatische Entwicklungstools unterstützten hier den Entwurfsprozess ausschließlich auf den unteren Abstraktionsebenen, wie beispielsweise der Logik- und der Schaltungsebene. Diese Methode kann als "Capture-and-Simulate"-Methode bezeichnet werden.

Modernere Entwurfsmethoden begannen schließlich, das Verhalten eines Systems mittels einer formalen Beschreibungssprache anstatt natürlichsprachlich zu definieren, um somit die Ungenauigkeiten der natürlichen Sprache zu vermeiden. Da die strukturelle und physikalische Beschreibung automatisch aus dieser formalen Beschreibung erzeugt (oder synthetisiert) werden kann, führte dies zu einer deutlichen Beschleunigung des Entwurfsprozesses und zur Vermeidung vieler Fehlerquellen. Dieser so genannte "Describe-and-Synthesize" Ansatz beschränkte sich zu Beginn auf Beschreibungen der Gate-Ebene, wo mittels Zustandsmaschinen (FSM) und booleschen Gleichungen das funktionale Verhalten beschrieben wurde. Mit Verbesserung der Entwurfstools wurde es später möglich, auch mittels höherer Sprachkonstrukte, wie Flow-Charts, Datenflussgraphen und Hardware-Beschreibungssprachen, diese Verhaltensbeschreibungen auf Register-Transfer-Ebene (RTL) durchzuführen.

Aktuelle und zukünftige Modellierungsmethoden erweitern nun diesen Ansatz dahingehend, dass die rechnergestützte Beschreibung des Verhaltens zu einer formalen und ausführbaren Spezifikation wird, die zum frühen Entwurfszeitpunkt frei von technologischen oder physikalischen Eigenschaften definiert ist, aber zum späteren Entwurfszeitpunkt entsprechend präzisiert werden muss. Sie enthält nun erstmalig auch die formale Beschreibung von Eigenschaften und Randbedingungen (Constraints), welche das System einzuhalten hat. Diese vollständige und formale Systembeschreibung hat die Eigenschaft einer vollständigen Dokumentation und ermöglicht das automatisierte Erforschen verschiedener Designentscheidungen. Sobald die Entscheidung für eine spezifische

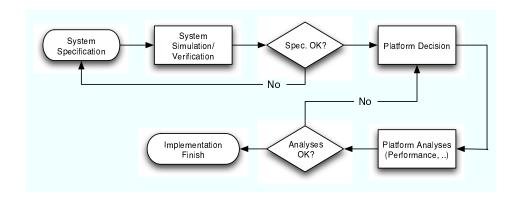

Technologie von den Entwicklern durchgeführt wird, wird es unmittelbar und einfach möglich, die Auswirkungen von Änderungen in der Spezifikation auf das System zu beobachten. Eine vollständige und ausführbare Systembeschreibung ermöglicht weiterhin, dass die Entwickler sich erst zu einem späten Entwurfszeitpunkt entscheiden müssen, welche Teile des Systems in Hardware oder in Software synthetisiert werden sollten. Die Folgen dieser Entscheidungen sind mittels Simulation der Spezifikation analysierbar und dienen somit als Kriterium für die endgültige Entscheidung des zu verwendenden Designs, weswegen Gajski diese Methode als "Specify-Explore-Refine" Konzept bezeichnet hat (siehe allgemeinen Entwurfsablauf in Abbildung 2.2).

Abbildung 2.2: Beispiel eines allgemeinen Entwurfablaufs

Die hier beschriebenen Vorgehensweisen haben allgemeingültigen Charakter und schlagen sich in den verschiedenen Entwurfsmethoden entsprechend der jeweiligen Aufgabenstellung und der gewählten Perspektive unterschiedlich nieder. Im Folgenden sollen typische Entwurfsmethoden dargestellt werden, die für den Fokus dieses Papiers – die Entwicklung von eingebetteten Systemen mit dem Schwerpunkt auf Software-Entwicklung – relevant sind. Die folgende Auflistung kann nicht alles abdecken, was zu diesem Thema verfügbar ist, da der Schwerpunkt auf der Darstellung der üblichen Entwurfsmethoden liegt.

Es wird hierbei mit der Beschreibung des "Hardware-Software-Codesign" und des "Interface Based Systemdesign" begonnen (2.2.1, 2.2.2), bei denen rein digitale Systeme auf hoher Ebene beschrieben werden, die ausschließlich aus Software und Hardware bestehen. Bei der Model-Driven Architecture steht der Entwurf reiner Softwaresysteme im Vordergrund, indem Systeme mittels UML oder SDL abstrakt beschrieben und möglichst automatisch für eine später zu definierende Zielarchitektur übersetzt werden (2.2.3).

Ein so spezifiziertes System bildet die Grundvoraussetzung des oben eingeführten Konzeptes der "Specify-Explore-Refine"-Entwurfsmethode, wobei für die vollständige Umsetzung die Validierung oder Verifizierung der Spezifikation sowie die Validierung der möglichen Implementationen fehlt. Dies wird mittels Rapid Prototyping (2.2.4) und Virtual Prototyping (2.2.5) ermöglicht.

Zu jeder der praktisch eingesetzten Entwurfsmethoden wird eine Auswahl der verfügbaren Entwurfstechniken dargestellt, um das Bild abzurunden.

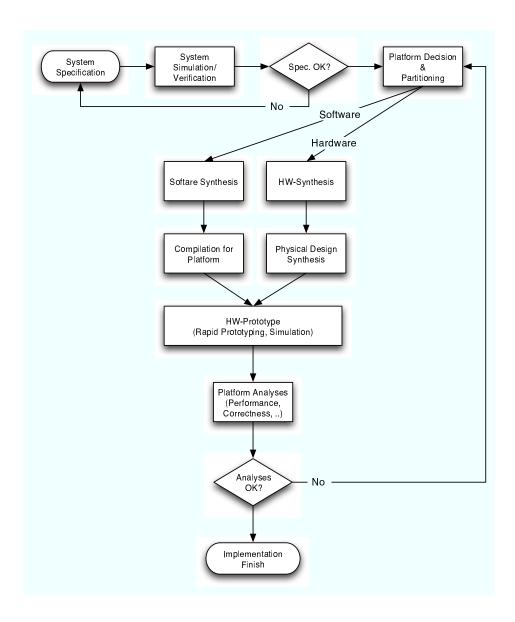

#### 2.2.1 Hardware-Software Codesign

Da Software und Hardware konzeptuell sehr ähnlich sind und heutzutage Hardware generell mit ähnlichen Sprachen wie Software beschrieben wird (über so genannte Hardware-Beschreibungssprachen), ist der Gedanke naheliegend, beides mit einer Sprache zu beschreiben und somit eine homogene Systembeschreibung zu bilden. Als mögliche Eingabesprachen sind, neben vielfältigen proprietären Spracherweiterungen wie z.B. Cx bei COSYMA [30], vor allem SystemC [43] und verschiedene Varianten von endlichen Automaten, wie z.B. CFSM [16] sowie in Zukunft auch UML-Statecharts [59] zu nennen. Ein Entwickler erhält bei diesem Ansatz die Möglichkeit, sich zu Beginn seines Entwurfs vollkommen auf die funktionalen Aspekte seines Designs zu konzentrieren. Erst zu einem späten Zeitpunkt im Entwurf, nach Implementierung und Validierung der Funktion des Systems, wird entschieden, welche der Elemente des spezifizierten Systems in Hardware und in Software synthetisiert werden. Dadurch wird das System partitioniert. Als Grundlage für eine Entscheidung werden die Kosten für die benötigten Hardware-Komponenten, welche die entsprechenden Aufgaben übernehmen sollen, sowie die Analyse der Gesamtleistung eines partitionierten Systems herangezogen. Ist das System zu langsam, so müssen besonders zeitaufwendige Systemelemente in schnelle Hardware übersetzt werden. Ist ein System zu teuer (da Hardwarekomponenten zu aufwendig werden), so muss stärker in Software synthetisiert werden [28] (siehe Abbildung 2.3).

Nach Durchführung der Partitionierung wird die Systembeschreibung in eine Hochsprache für Software (typischerweise in C/C++) und Hardware (oftmals VHDL) synthetisiert und somit von einer homogenen zu einer heterogenen Beschreibung überführt. Die Software wird anschließend über eine übliche Compiler-Toolchain in Maschinensprache für den einzusetzenden Mikrocontroller übersetzt. Die Hardware-Beschreibung wird mittels Hardware-Synthesetools abhängig von der Zielarchitektur in Implementationen für FPGAs, ASICs oder Custom-Chips überführt.

Das Design kann durch eine Simulation der homogenen, aber auch der heterogenen Beschreibung überprüft werden. Weitere Möglichkeiten zur Validierung ergeben sich durch eine Ausführung auf einem Prototypensystem, was dann zu der Methode des Rapid Prototyping führt (siehe Kapitel 2.2.4).

#### 2.2.2 Interface-Based System Design

Das Interface Based System Design beschreibt eine Erweiterung der Hardware/Software Codesign Methode. Diese Erweiterung wurde eingeführt, da für komplexere Systeme die Kommunikation zwischen den digitalen Systemkomponenten untereinander und mit der Software nicht mehr ausschließlich über speichergekoppelte Schnittstellen (memory mapped I/O) realisiert werden kann. Heutige Schnittstellen beinhalten verschiedene Bussysteme und sogar Netzwerkschnittstellen [26, 33]. Somit ist die oben beschriebene Entscheidung bezüglich der Implementierung einer Spezifikation, die sich beim reinen Hardware-Software-Codesign auf die Frage der optimalen Software/Hardware-Partitionierung beschränkte, um den Aspekt der Auswahl und Implementierung einer optimalen Schnittstelle erweitert.

Das Ziel dieser Methode ist somit, die im Hardware-Software-Codesign entwickelten Konzepte um Beschreibungsmöglichkeiten für Schnittstellen zu erweitern [63] und dadurch einen Top-Down Entwurf von der Spezifikation bis zur Implementation zu ermöglichen. Der Ansatz hierfür ist die Trennung der Kommunikation eines Systems von deren Funktion. Dies ermöglicht eine erhöhte

Abbildung 2.3: Hardware/Software Codesign

Modularität beim Chipdesign, da Funktionsblöcke somit einfacher und freier kombinierbar sind. Das Interface wird entsprechend der ausgewählten Kombination dieser Funktionsblöcke entwickelt, aus Bibliotheken ausgewählt (z.B. um standardisierte Busse zu nutzen) oder sogar automatisch erzeugt [55].

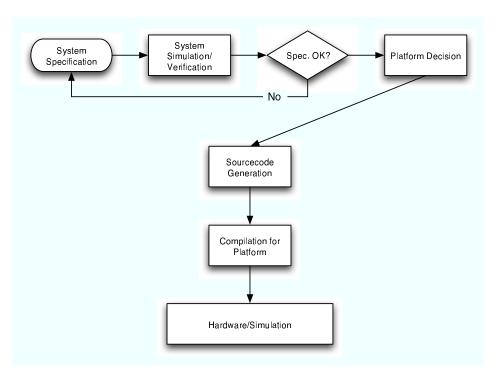

#### 2.2.3 Model Driven Architecture

Als so genannte "Model-Driven Architecture" (MDA) wird eine Methode bezeichnet, bei der das Verhalten der Software unabhängig von der Zielplattform modelliert und simuliert wird (Platform Independent Model, PIM). Nach der Definition der Zielplattform erfolgt anschließend automatisch die Erzeugung des plattformabhängigen Modells (Platform Specific Model, PSM) mittels entsprechender Tools unter Verwendung von Plattform-Bibliotheken [3]. In diesem Konzept wird die Rückwirkung der Plattformentscheidung auf das Verhalten des Systems nicht berücksichtigt (siehe Abbildung 2.4). Somit wird angenommen, dass die automatische Codegenerierung und die Abbildung auf die jeweiligen Fähigkeiten der Zielplattform befriedigend funktionieren.

Abbildung 2.4: Model Driven Architecture

#### 2.2.3.1 Techniken zur Model Driven Architecture

Zu dieser Methode gibt es bereits kommerzielle Entwurftools, die vor allem für Entwicklungen geeignet sind, welche ihren Schwerpunkt in dem Entwurf von Software für eingebettete Systeme haben. Der Entwurf von Hardware wird somit nicht unterstützt.

ETAS (ASCET-MD): Das zu entwickelnde System wird auf physikalischer Ebene anhand von Blockdiagrammen, Zustandsautomaten, Konditionstabellen oder Textuell in den Hochsprachen ESDL oder C spezifiziert. So spezifizierte Modelle können beliebig miteinander zu einem System verbunden werden. Dieses System wird nun in C und anschließend für verschiedene Embedded Control Units (ECU) oder einer Rapid-Prototyping-Hardware übersetzt, wodurch Hardware-in-the-loop-Tests ermöglicht werden. Diese Übersetzung ist sehr aufwendig, da auf der hochsprachlichen Ebene keine Rücksicht auf spezielle Eigenschaften der später zu verwendenden Hardware genommen wird. Fehlt auf dem Zielsystem z.B. eine arithmetische Einheit für Fließkomma-Operationen, so muss dies bei der Codegenerierung mühselig berücksichtigt/nachgebildet werden. Eine fehlerfreie Funktion dieser sehr komplexen Umsetzung ist ebenfalls fraglich und müsste auf dem realen Target aufwendig überprüft werden.

**Telelogic (Telelogic Tau Suites):** Die Tools von Telelogic bieten verschiedene Sprachansätze für den Entwickler und entsprechen somit dem Multi-Language Ansatz, wie er in Kapitel 2.3.2 beschrieben wird. Je nach eingesetztem Tool kann das System mit *UML* oder *SDL* (Specification and Description Language) spezifiziert und implementiert werden. Wird UML gewählt, so wird er in eine SDL-Beschreibung überführt, die anschließend in ausführbaren Code für *ECUs* mündet.

Die beiden hier beschriebenen Tools setzen den schon von Gajski geforderten Trend um, bei dem Entwurf der Spezifikation und der Implementierung möglichst auf hoher Ebene zu bleiben. Die hier entwickelte Software wird im praktischen Ansatz auf ein Rapid-Prototypingsystem übertragen und anhand einer realen Testumgebung überprüft. Ist der Test erfolgreich, so wird die Software für das einzusetzende Zielsystem übersetzt und dort ausgeführt. Die Folgen für den Fall, dass die Software auf dem Target System nicht oder nur unvollkommen funktioniert, werden hierbei nicht erwähnt. Dieser Fall kann aufgrund vielfältiger Ursachen auftreten, selbst wenn die Spezifikation an sich auf hoher Ebene korrekt sein sollte:

- 1. Die Codegenerierung für die Zielplattform schlägt fehl (Compiler-Fehler, Inkompatibilitäten zwischen Bibliotheken, usw.)

- 2. Die Bibliotheken, die fehlende Funktionen auf der Zielplattform nachbilden sollen (z.B. das Fehlen einer Fließkomma-arithmetischen Einheit), zeigen nicht exakt das Verhalten, das auf der hohen Ebene erwartet wurde. Dies kann z.B. dadurch passieren, dass bei einer Fließkomma-Berechnung eine andere Genauigkeit realisiert wurde als im Modell vorausgesetzt. Weiterhin kann eine reale Hardware, wie z.B. ein Digital/Analog Wandler, andere Auflösungen zeigen, als es auf hoher Ebene berücksichtigt/erwartet wurde. So ein Problem lässt sich auch mit einer Plattform-Bibliothek nicht lösen und darf prinzipiell nicht zu einer Erzeugung von Programmcode führen!

- 3. Das Zeitverhalten auf der realen Plattform führt zu fehlerhaftem Verhalten, da z.B. Informationen nicht rechtzeitig verarbeitet werden können und somit vorgeschriebene Sampling-Raten nicht eingehalten werden können.

All die hier genannten Probleme sind erst nach der Produktion der Zielhardware zu erkennen und verursachen möglicherweise hohe Kosten bei der Änderung oder bei der Analyse der Ursachen, zumal das Vorhandensein einer Testumgebung auf dem Zielsystem nicht vorgesehen und somit auch kein Mapping von Fehlern auf das Modell (Back annotation) realisiert ist.

#### 2.2.4 Rapid Prototyping

In der Forschung wird die Notwendigkeit der Verbindung von virtuellen und realen Komponenten zu einem Gesamtsystem schon länger untersucht und z.B. im DFG Schwerpunktprogramm 1020 mit dem Thema "Rapid Prototyping für integrierte Steuerungssysteme mit harten Zeitbedingungen" behandelt. Das erklärte Ziel dieses Ansatzes ist es, möglichst schnell von einer ausführbaren Spezifikation zu einem lauffähigen Prototypen zu kommen, welcher über programmierbare Schnittstellen in eine reale Umwelt integriert wird. Ziel ist somit das Validieren einer Spezifikation (!) in der Praxis.

Die Motivation beim Rapid Prototyping liegt klar in der Vermeidung von Simulationen. Insbesondere soll eine Modellierung einer Umwelt vermieden werden. Es ist damit in diesem Punkt von dem Ansatz des virtuellen Prototypen zu unterscheiden (siehe Abschnitt 2.2.5).

Entsprechend der Abstraktionsebene des Prototypen kann zwischen den folgenden Varianten dieser Methode unterschieden werden [15, 48]:

- Konzept-orientiertes Rapid Prototyping: Hier wird die Spezifikation automatisch in einen ausführbaren Prototypen übertragen, wobei der hier auftretende Speicherverbrauch und die Hardwarekosten nicht von Interesse sind. Für die Abarbeitung der Software wird Echtzeitfähigkeit gefordert. Im Automobilbereich wird diese Art von Prototypen auch als A-Muster bezeichnet, welches die Machbarkeit eines Konzeptes aufzeigen soll und somit ausschließlich Demonstratorcharakter hat. Das Ziel dieses Prototypen ist ausschließlich die Klärung der Systemziele.

- Architektur-orientiertes Rapid Prototyping: Die endgültige Architektur des Systems steht

fest. Einige Komponenten sind vorhanden, während andere sich noch in der Entwicklung

befinden. Die Zielhardware (Mikrocontroller, FPGA, Signalprozessor) findet schon Verwendung, ist aber noch nicht für den Serieneinsatz optimiert. Diese Art von Prototyp wird im

Automobilbereich als B-Muster bezeichnet und stellt das Vorbild für die Serienfertigung dar.

- Implementierungs-orientiertes Rapid Prototyping: Es handelt sich hier um ein hochgradig

optimiertes System, welches zur Evaluierung der einzelnen Applikationen für den Serieneinsatz verwendet wird. Es werden nur noch letzte Änderungen evaluiert. Diese Prototypen sind

als Vorlagen für die Serienfertigung geeignet und werden im Automobilbereich als C-Muster

bezeichnet.

In der Forschung liegt der Schwerpunkt auf dem Konzept-orientierten Rapid Prototyping und – aufgrund seiner geringeren Allgemeingültigkeit – eher nachranging auf dem Architektur-orientierten und Implementierungs-orientierten Rapid Prototyping. Mittels HW/SW Codesign kann von dieser Methode aus ebenfalls der Entwurf der B- und C-Muster realisiert werden.

Im Gegensatz zum Ansatz des Virtual Prototyping wird dabei auf die Vorteile der Simulation weitestgehend verzichtet, da die Modellierung als zu zeitraubend angenommen wird, wie im nächsten Kapitel erläutert wird.

#### 2.2.4.1 Techniken zum Rapid Prototyping

Wie bereits oben beschrieben wurde, versucht das Rapid Prototyping den Ansatz, möglichst früh von einer ausführbaren Systemspezifikation zu einem realen Prototypen zu kommen, welcher an-

hand einer realen Umgebung auf seine Tauglichkeit getestet wird. Der Schwerpunkt liegt in diesem Zusammenhang bei dem konzept-orientierten Rapid Prototyping. In der Forschung sind verschiedene Ansätze zu finden, wobei einige exemplarisch im Folgenden aufgezählt werden:

• Bei dem Projekt EVENTS [50] der Universität Oldenburg wird, aufbauend auf selbstentwickelten SPARC-Prozessoren (nach der Sparc V.8 Spezifikation) und der Verbindung mit FPGAs, versucht, ein System zu konstruieren, welches extrem schnell auf äußere asynchrone Ereignisse reagieren kann. Die eingesetzten Prozessoren sind jeweils in der Lage, bis zu 4 Threads direkt auf dem Prozessor zu verwalten (Multithreading Prozessor), welche innerhalb von nur 5 Prozessortakten gewechselt werden können. Da die Prozessoren über einen, hier nicht näher zu erwähnenden, Mechanismus als Slave-Einheit an die FPGA-Einheit angeschlossen sind, wird die Umschaltung der Threads über eine spezielle FPGA-Schaltung ausgelöst, die sehr schnell auf externe Ereignisse reagiert. Dieses Konzept ersetzt das übliche interruptbasierte Reagieren auf Ereignisse.

Neben diesem extrem schnellen Reaktionsmechanismus ist es weiterhin möglich, über herkömmliches Software-Scheduling auf normale Ereignisse zu reagieren.

Dieses Konzept ist aufgrund seiner Zielsetzung und seiner technischen Umsetzung nur für Spezialfälle und kaum für den Standardeinsatz geeignet, zumal die Spezialhardware aufgrund der hohen Kosten nicht für große Stückzahlen Verwendung finden wird. Erkenntnisse aus einem solchen Prototypen sind wohl auch kaum allgemeingültig zu verwerten.

• Im Zuge einer Kooperation zwischen den Universitäten München und Erlangen-Nürnberg ist ein System entwickelt worden, das aus einer formalen Systemspezifikation auf SDL-und MSC- (Message Sequence Charts) Basis, welche mit Zeitanforderungen angereichert wurde (SDL\*, PMSC), eine Prototypen-Implementation erzeugt [23]. Nach dem üblichen Hardware/Software-Codesign Ansatz wird diese Beschreibung in C und VHDL Code synthetisiert und ausgeführt. Während die C-Beschreibung auf einem Echtzeit-Betriebssystem (RTEMS) ausgeführt wird, wird die VHDL Beschreibung entweder auf einem HW-Laufzeitsystem in Software ausgeführt oder in ein FPGA-System übertragen. Für die Ausführung stehen hierbei zwei Laufzeitumgebungen zur Verfügung, welche für unterschiedliche Fragestellung eingesetzt werden können und sich gegenseitig ergänzen:

Das System, mit dem Namen "Phoenix", besteht aus einer CPU, welche mit derjenigen des jeweiligen Zielsystems übereinstimmen sollte, und FPGAs. Hauptaufgabe für dieses System ist die Überprüfung der in SDL\* spezifizierten Zeitschranken, indem in der Spezifikation die Instrumentierungspunkte definiert werden und anschließend mittels HW-Monitoring ausgemessen werden. Somit kann die Einhaltung der Zeitgrenzen validiert werden.

Bei dem zweiten System, mit dem Namen "REAR", wird die Spezifikation auf einem skalierbaren heterogenen Multiprozessorsystem ausgeführt, das keinen Bezug zu einem späteren Target hat. Ziel dieses Systems ist die Ermöglichung einer Echtzeitanalyse der Spezifikation, für die alle Ausführungszeiten der in SDL\* spezifizierten Transitionen benötigt werden. Hierzu wird jede Transition am Eingangs- und Ausgangspunkt der Zustandsmaschine instrumentiert und mittels Hardware-Monitoring ausgemessen.

Das Mechatronik-Laboratorium Paderborn legt seinen Schwerpunkt auf die Realisierung von hierarchischen Regelungen, die auf einem Workstation-Cluster als Offline-Simulation ausgeführt werden [65]. Bei diesem System werden die gleichen Regel-Algorithmen (in ANSI-C programmiert) auf dem Simulator wie auch in einer HIL-Umgebung<sup>1</sup> eingesetzt, um Vergleichbarkeit zu gewährleisten, wobei kein Prozessormodell des späteren Target-Systems Verwendung findet.

Stufenweise werden Elemente der Simulation durch reale Komponenten ersetzt, wobei die Schnittstelle zwischen realem und virtuellem System ausschließlich auf gleicher Abstraktionsebene (einfache digital/analog Schnittstellen) realisiert wird. Die Ermittlung der Leistungsanforderung für ein später zu wählendes Target-System basiert auf Zeitmessungen (Hardware-Monitoring) im Zusammenhang mit Codeanalysen (Zählen und Gewichten) und Worst-Case Abschätzungen der Kommunikationslatenzzeiten.

Der Prototyp besteht aus mindestens einem Board mit PowerPC Prozessor und besitzt so die Möglichkeit, mehrere Boards transputerähnlich oder über einen CAN-Bus zu verbinden. Somit werden mögliche Einflüsse der Codegenerierung bezüglich des realen Targets in diesem System nicht betrachtet.

Auch in kommerziellen Produkten wird das Rapid Prototyping bereits genutzt. Der aktuelle Stand der Technik soll beispielhaft an den folgenden Produkten dargestellt werden:

Mathworks inc. (Matlab/Simulink): Die Firma Mathworks bietet ein erfolgreiches Softwarepaket an, welches die Bereiche Software-in-the-loop, Hardware-in-the-loop und eingeschränkt auch Control-Prototyping<sup>2</sup> unterstützt. Mittels Blockdiagrammen ermöglicht das Paket den Aufbau komplexer Regelstrecken, die auch in C-Code und somit in ausführbare Programme gewandelt werden können.

**dSPACE:** Die Firma dSpace erweitert das Paket von Mathworks durch ein selbst entwickeltes Rapid-Prototyping-System, basierend auf AMD-Opteron und PPC-Prozessoren, die über einen speziellen I/O-Prozessor vernetzbar sind. Der Schwerpunkt liegt auf *Hardware-in-the-loo*p, aber es ist mittels spezieller Software ebenfalls möglich, die C-Sourcen von Matlab/Simulink für spezielle Target-ECUs zu übersetzen.

Somit besteht auch mit diesem Produkt die Möglichkeit zum Control Prototyping.

Beide oben genannten Firmen verfolgen einen traditionellen, regelungstechnischen Ansatz, der durch die Verwendung von Blockdiagrammen deutlich wird. In neueren Arbeiten wird der stärkeren Verbreitung von standardisierten Notationen, wie SDL und vor allem UML, Rechnung getragen sowie die Kopplung kommerzieller CASE-Tools über das CDIF-Datenaustauschformat [20, 15] und XMI [6] realisiert. Somit werden die Techniken der Model Driven Architecture (MDA) verstärkt genutzt und die Spezifikation des Systems standardisiert. Weiterhin wird erkannt, dass die existierenden kommerziellen Entwurfstools die Kopplung von zeitkontinuierlichen und informationstechnischen Subsystemen in vielen Fällen nur auf der Codeebene unterstützen und dadurch die Erweiterung vom sehr eng gefassten Ansatz des Hardware/Software Codesigns auf einen umfassenderen Systembegriff erschwert. Ziel muss daher sein, die Kopplung auf Modellebene zu realisieren. Hierzu ist gerade UML hervorragend geeignet, da es die Umwandlung zwischen Blockund UML-Diagrammen ermöglicht [41].

All diese Ansätze zeigen einige wesentliche *Schwächen*: Da die abstrakten Spezifikationen lediglich auf einer Testhardware ausgeführt werden, fehlen Modelle der Zielsysteme und der Umgebung sowie

<sup>&</sup>lt;sup>1</sup>Definitionen siehe in Kapitel: 2.5

<sup>&</sup>lt;sup>2</sup>Definitionen siehe in Kapitel: 2.5

die Berücksichtung der später verwendeten Compiler-Toolchains. Auf den Prototypen-Systemen wird keine Simulation unter Berücksichtung eines Plattformmodells durchgeführt, sondern die lauffähige Spezifikation ausgeführt, was einen wesentlichen Unterschied zum Virtual Prototyping darstellt. Somit ist neben der schon erwähnten Problematik einer korrekten Performance-Analyse auch z.B. der durchaus relevante Einfluss der Compiler nicht in der Untersuchung enthalten. Die beste Performance-Analyse auf einem synthetischen Prototypen hat nur geringe Aussagekraft, wenn auf dem späteren Target-System ein komplett anderer Compiler mit z.B. schlechterer Codeoptimierung eingesetzt wird oder eventuell in bestimmten Situationen einen fehlerhaften Code erzeugt. Die Möglichkeit durch statische Analysen und Hardware-Monitoring zumindest eine Worst-Case Abschätzung des Zeitverhaltens von Software durchzuführen ist zwar eine Verbesserung der hier geschilderten Problematik, aber stellt keine Lösung dar [62].

Auch die Annahme, dass das Validieren ausschließlich in einer realen Umgebung Vorteile für die Entwicklung bringt, kann bei heutigen Systemen durchaus in Zweifel gezogen werden. Denn die Verwendung massiv verteilter eingebetteter Systeme und die damit ebenfalls steigende Einflussname der Umgebung auf die Kommunikation untereinander kann kaum noch bezüglich Grenzbelastungen und Störeinflüssen systematisch überprüft werden, ohne dass die Kosten für die Testaufbauten und der zum Testen notwendige Zeitbedarf untragbar werden. Dies kann beispielsweise anhand eines modernen Automobils vor Augen geführt werden, welches in einen Tunnel einfährt. Die Unterbrechung diverser Kommunikationskanäle mit der Umwelt (GPS, GSM, Radio, DVB-T, ...) führt zu einer hohen Belastung des internen Bussystems. Kommen dann noch ungewöhnliche interne Ereignisse dazu, kann es zu einem Kollaps der Kommunikation führen Derartige Situationen wären in einem Praxistest anhand einer realen Umgebung kaum systematisch überprüfbar.

Die Vorteile des Rapid Prototyping liegen vor allem in der frühen Analyse der Systemziele und der grundlegenden Überprüfung der Korrektheit einer Spezifikation. Dadurch werden teure Rückschritte durch Fehlentscheidungen vermieden. Um die Entwicklung realer Prototypen heutiger Komplexität zu unterstützen, werden weitere Techniken benötigt, die die oben genannten Einflüsse berücksichtigen können und ebenfalls das systematische Testen unterstützten. Diese Techniken sollen im nächsten Kapitel beschrieben werden.

#### 2.2.5 Virtual Prototyping

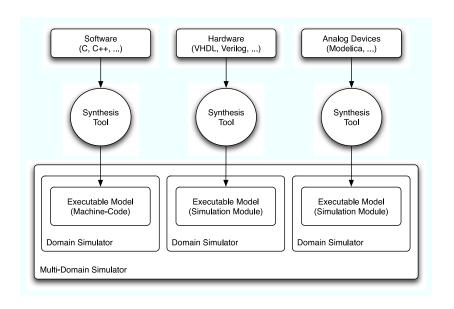

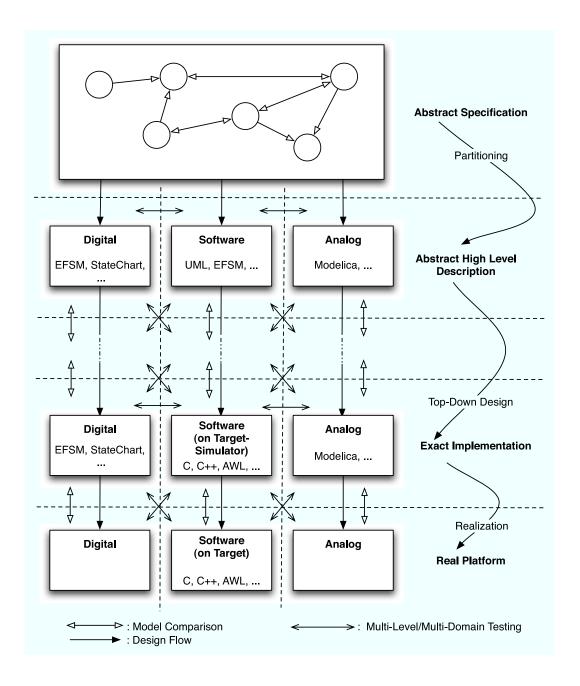

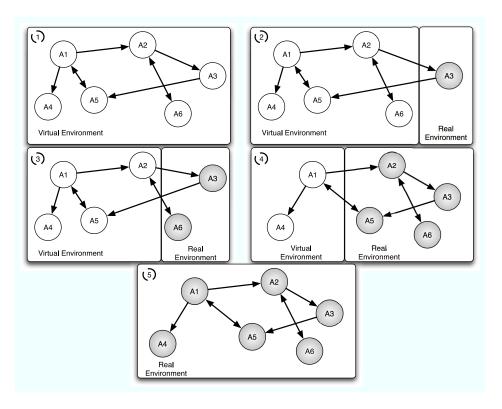

Dieses Konzept ist mit dem Bereich der so genannten *Virtual Reality* eng verbunden und erweitert die in diesem Zusammenhang entwickelten Technologien, um technische Abläufe, wie z.B. Produktionsabläufe, Anlagenautomatisierungen, bis hin zu eingebetteten Systemen mit Mikrocontrollern und Bussen, zu simulieren und zu visualisieren [34]. Im Gegensatz zum Rapid Prototyping wird beim Virtual Prototyping der Vorteil einer *vollständigen Simulation* eines Prototypen zusammen mit seiner Umwelt betont (siehe Abbildung 2.5). Besteht ein System auch aus nichtdigitalen Komponenten, so ist es nicht mehr sinnvoll, nur eine Sprache für die Spezifikation des Gesamtsystems zu verwenden (siehe Abbildung 2.6). Die Spezifikation wird somit in verschiedene Teilspezifikationen aufgebrochen, die jeweils entsprechend ihrer Domäne (Digital, Analog, Software, ...) mit einer jeweils optimalen Modellierungssprache abgebildet werden (siehe Kapitel 2.3).

Auch wenn die Modellierung – je nach Abstraktionsgrad der Modelle – teilweise viel Zeit in Anspruch nehmen kann, ist doch nur durch eine zusätzliche Modellierung einer kompletten Umgebung die Möglichkeit einer systematischen und reproduzierbaren Validierung des Prototypen gegeben. Auch die Vermeidung von Gefahren für Mensch oder Maschine sind in einer rein virtuellen Umgebung kostengünstiger zu realisieren. Bei der heutigen Komplexität von Systemen tritt ein weiterer

wichtiger Aspekt immer stärker im Vordergrund: Gerade im Falle einer sehr komplexen Interaktion mit der Umwelt ist das systematische Überprüfen von Störfaktoren durch die Umwelt nur durch das Virtual Prototyping praktisch realisierbar, da neben den hohen Kosten für komplexe Testaufbauten gerade der benötigte Zeitaufwand für die systematische Abarbeitung von Testsequenzen schnell zu einer Überschreitung der tolerierbaren Entwicklungszeit (time to market) führen kann.

Abbildung 2.5: Virtual Prototyping mit homogener Modellsimulation (Single-Language Ansatz)

Um den hier beschriebenen Anforderung wirklich gerecht werden zu können, müssen die Modelle ausreichend genau sein, um überhaupt verwertbare Aussagen gegenüber dem späteren echten Prototypen machen zu können. Weiterhin ist die zeitlich genaue Simulation der verwendeten Modelle wichtig, da die korrekte Berücksichtigung des Zeitverhaltens neben der Notwendigkeit der Durchführung von Performance-Analysen einen nicht zu vernachlässigbaren Einfluss auf das funktionale Verhalten eines Systems hat. Dies verlangt einen erhöhten Aufwand bei der Modellierung sowie die unbedingte Notwendigkeit der Validierung der Modelle gegenüber den originalen Komponenten,

Abbildung 2.6: Virtual Prototyping mit heterogener Modellsimulation (Multi-Language Ansatz)

wie z.B. den einzusetzenden Mikrocontrollern.

#### 2.2.5.1 Techniken zum Virtual Prototyping

ClearSim-MultiDomain: Der Schwerpunkt liegt bei diesem an der Universität Hannover entwickelten Simulationspaket in einer durchgängigen Unterstützung von zeitbasierten Modellen und der zeitlich korrekten Synchronisation dieser untereinander. Somit ist es nicht nur möglich, das funktionale, sondern auch das zeitliche Verhalten zu modellieren, da alle Modelle ein Zeitmodell besitzen müssen. Die Modellierung mittels EFSM (Extended Finite State Machines), SDL oder UML-StateCharts wurde um die Möglichkeit ergänzt, den Ubergang von Zuständen mit einer Inkrementation der virtuellen Zeit zu koppeln und somit den Ablauf von Zeit zu modellieren. Aber auch die Modellierung analoger Komponenten kann erfolgen und wird im Zeitverhalten ebenfalls berücksichtigt. Bei Modellen von interpretierenden Systemen, wie z.B. einem Mikrocontroller oder einer SPS, wird das Zeitverhalten entsprechend des realen Pendants auf Instruktionsebene durchgeführt und ist dadurch die Voraussetzung führ eine sehr genaue Simulation der Software bezüglich ihres funktionalen als auch zeitlichen Verhaltens [11]. Um compilerabhängige Einflüsse zu berücksichtigen, wird die Software im originalen Binärformat interpretiert und ausgeführt [60]. Eine weitere Spezialität stellt in diesem Zusammenhang die Möglichkeit dar, Testroutinen in der Software zu belassen, die selber keinen Einfluss auf das Zeitverhalten haben dürfen. Damit lassen sich schon im frühen Entwurfsstadium korrekte Zeit- und Performanceanalysen durchführen. Weiterhin können die Programme durch so genannte Assertions erweitert werden, welche die Einhaltung bestimmter spezifizierter abstrakter Randbedingungen überprüft, um bei Verletzung dieser angemessen zu reagieren [52].

Zusammen mit der Verfügbarkeit von Modellen zur Simulation von Buskommunikation (z.B. den CAN-Bus), wird die zeitgenaue Simulation eines aus modernen Komponenten bestehenden, virtuellen Prototypen mit seiner Umgebung realisierbar.

Ansoft (Simplorer): Der Simplorer ist ein Multi-Domain Simulations-Framework der Firma Ansoft. Ahnlich ClearSim-MultiDomain gehört dieser ebenfalls zu der Klasse der Multi-Language modellierten Systeme (siehe Kaptitel 2.3.2). Diese Klasse zeichnet sich durch die Möglichkeit der Modellierung durch verschiedene Modellierungssprachen aus, wie in diesem Fall VHDL-AMS, CIRCUITS (numerische Modellierung von Schaltungen), Block Diagrammen (analoge, oder diskrete Signalfluss Modellierung) und State-Machines (Zustandmaschinen, FSM). Weiterhin besteht die Möglichkeit zur Einbindung anderer Simulationsumgebungen, wie Matlab/Simulink, MathCad, ADVISOR und anderen selbstgeschriebenen C/C++ Modellen. Hardware-in-the-loop oder ähnliches ist nicht möglich. Alle Modelle besitzen ebenfalls ein Zeitmodell und bilden somit eine zeitgenaue Simulationsumgebung, wobei aber bezüglich der Modellierung von komplexen Prozessoren oder sogar Mikrocontrollern keine Informationen vorliegen. Soll die Software für einen Mikrocontroller in die Simulation integriert werden, so wird diese als Shared-Library (DLL) gekapselt und in den Simulator eingefügt. Somit wird die Software ausschließlich funktional ausgeführt und nicht entsprechend eines späteren Target-Systems simuliert. Die Existenz von Modellen zur Simulation des Verhaltens von Bussen ist ebenfalls nicht dokumentiert. Der Datenaustausch zwischen den Simulations-Modellen findet auf niedriger Abstraktionsebene (Spannungen, Ströme) statt und hat seinen Schwerpunkt in der Simulation analoger Abläufe.

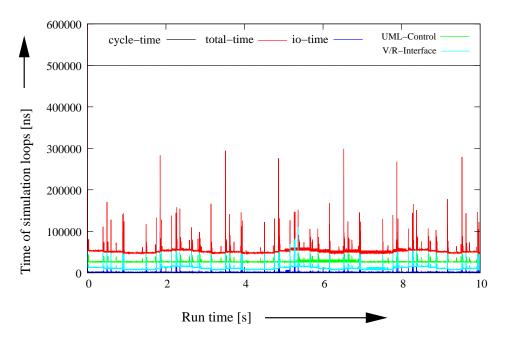

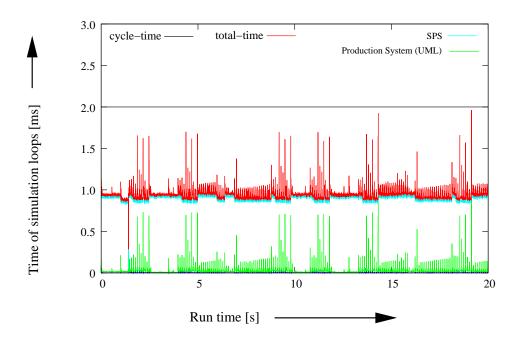

Ptolemy: Das Ptolemy Framework wurde von der Universität Berkeley ins Leben gerufen und wird inzwischen in der zweiten Version als Ptolemy II als komplett redesignte Java-Version zur Verfügung gestellt. Bei dieser Multi-Domain-Simulationsumgebung wird ebenfalls das Aktor- zusammen mit dem Multi-Language Konzept verwirklicht, wobei im Gegensatz zu z.B. ClearSim-MultiDomain eine objektorientierte Umsetzung existiert, die auch Vererbung und hierarchische Strukturen mit Aktoren erlaubt. Die Datentypen für die Kommunikation und das Zeitmanagement werden im Gegensatz zu ClearSim-MultiDomain nicht vom Simulations-Framework definiert, sondern durch die Domänenbeschreibung festgelegt, was einerseits zu einer höheren Flexibilität führt, aber andererseits eine Einschränkung bezüglich der prinzipiellen Kombinationsmöglichkeit untereinander zur Folge hat. Somit ist die Verbindung prinzipiell nur zwischen kompatiblen Domänen und Aktoren möglich. Als kompatibel sind hier Domänen zu bezeichnen, die bezüglich ihrer Vererbung den gleichen Ursprung haben und somit zwangsläufig gleichartig sind, also über die gleichen Datentypen verfügen und mit einem kompatiblen Zeitmodell arbeiten. Um ein Maximum an Variabilität zu erhalten, ist der Entwickler von Aktoren angehalten, seine Modelle domain-polymorphic und sogar data-polymorphic zu gestalten. Dadurch können die Aktoren in verschiedenen Domänen eingesetzt werden [14, 13]. Die Kommunikation zwischen den Aktoren erfolgt nachrichtenbasiert.