A Coprocessor for Fast Searching in Large Databases: Associative Computing Engine

## **DISSERTATION**

submitted in partial fulfillment of the requirements for the degree of

## Doktor-Ingenieur (Dr.-Ing.)

to the Faculty of Engineering Science and Informatics of the University of Ulm

by

## Christophe Layer

from Dijon

First Examiner: Prof. Dr.-Ing. H.-J. Pfleiderer

Second Examiner: Prof. Dr.-Ing. T. G. Noll

Acting Dean: Prof. Dr. rer. nat. H. Partsch

Examination Date: June 12, 2007

## Abstract

As a matter of fact, information retrieval has changed considerably in recent years with the expansion of the Internet and the advent of always more modern and inexpensive mass storage devices. Due to the enormous increase in stored digital contents, multimedia devices must provide effective and intelligent search functionalities. However, in order to retrieve a few relevant kilobytes from a large digital store, one moves up to hundreds of gigabytes of data between memory and processor over a bandwidth-restricted bus. The only long-term solution is to delegate this task to the storage medium itself.

For that purpose, this thesis describes the development and prototyping of an associative search coprocessor called ACE: an Associative Computing Engine dedicated to the retrieval of digital information by means of approximate matching procedures. In this work, the two most important features are the overall scalability of the design allowing the support of different bit widths and module depths along the data path, as well as the obtainment of the minimum hardware area while ensuring the maximum throughput of the global architecture.

After simulation, the correctness of the results delivered by the FPGA prototyping board could be verified using a text encoding scheme based on hashing theory. The performance of the hardware platform has been compared with the same application running in software on a general purpose processor. Accordingly, a speed-up of three to four orders of magnitude is achieved for the FPGA system versus many recent personal computers with different internal hardware configurations.

## Acknowledgments

First and foremost, I express my gratitude to Prof. H.-J. Pfleiderer for his constant support, motivation and encouragements. Thank you for welcoming me in the Institute of Microelectronics at the University of Ulm and giving me the opportunity to pursue my research interests.

Furthermore, I am very grateful to Prof. T. G. Noll of the RWTH Aachen for his interest in my work and his agreement to report about it. Thank you for the extremely helpful feedback, for the suggestions about the completion of the manuscript and for advising on this dissertation.

I would also like to thank Prof. P. Ruján for his continuous encouragements and for pursuing my work over further international projects. Dr. G. Lapir is gratefully acknowledged for the discussions at an earlier stage of this project and for providing information and materials about the associative search method.

I would like to thank my colleagues from the Institute of Microelectronics, especially M. Bschorr, C. Günter, O. Pfänder, J. Rauscher, W. Schlecker, K. Schmidt, R. Schreier and E. Schubert for all the constructive discussions and comments, as well as for the very comfortable atmosphere at work. Nonetheless, I am indebted to G. Kirilov for his expertise and contribution to the synthesis of the memory controller.

Finally, special thanks go to Mrs. Höfer for her kindness, help and support.

Ulm, October 18, 2007

Christophe Layer

# Table of Contents

| Cha | apter I $\diamond$ Introduction                   |

|-----|---------------------------------------------------|

| 1   | Information Retrieval Systems                     |

| 2   | The Problem with Storage Devices                  |

|     | 2.1 Running into the Memory Wall                  |

|     | 2.2 Need for Hardware Support                     |

| 3   | Organization of the Thesis                        |

| Ch  | apter II $\diamond$ Background                    |

| 1   |                                                   |

| 1   | 1.1 Integrated Circuits Implementation Strategies |

|     | -                                                 |

|     |                                                   |

|     | 1.3 Field Programmable Gate Arrays                |

| 0   | 1.4 Semiconductor Memory Devices                  |

| 2   | - *************************************           |

|     | 2.1 Classical Algorithms                          |

|     | 2.2 Flexible Pattern Matching                     |

|     | 2.3 Dynamic Programming                           |

|     | 2.4 Hash Functions and Text Signatures            |

| 3   | 0 1 0                                             |

|     | 3.1 Sequential Sorting                            |

|     | 3.2 Bit-Level Structures                          |

|     | 3.3 Sorting Networks                              |

|     | 3.4 Summarization                                 |

| Cha | apter III $\diamond$ Related Work                 |

| 1   |                                                   |

|     | 1.1 Web Search Engines                            |

|     | 1.2 Software Functionalities for Computers        |

| 2   |                                                   |

| _   | 2.1 Associative and Parallel Processors Systems   |

|     | 2.2 Merging Logic and Memory                      |

|     | 2.3 Special Purpose Coprocessors                  |

|     | 2.4 Summarization                                 |

| 3   |                                                   |

| 0   | 3.1 Building the Signature File                   |

|     | 3.2 The Retrieval Process                         |

|     | 5.2 The Retrieval Process                         |

| Cha | apter IV $\diamond$ System Level Analysis         |

| 1   | Motivation and Expectations                       |

|     | 1.1 Problem Statement                             |

|     | 1.2 Proposed Research                             |

| 2   |                                                   |

|     | 2.1 Exploration of the Software Model             |

VIII Table of Contents

| 3    | 2.2 Sequential Algorithm Analysis                     | 54<br>58   |

|------|-------------------------------------------------------|------------|

|      | 3.1 Parallelization of the Algorithm                  | 58<br>62   |

| Cha  | $\mathbf{v} + \mathbf{v} + \mathbf{v}$                | 65         |

| 1    | System Management and Peripherals                     | 65         |

|      | 1.1 Operation Scheduling                              | 65         |

|      | 1.2 Designing the Memory Interface                    | 66         |

| 2    | Building the Computational Data Path                  | 71         |

|      | 2.1 Penalty Calculating Unit                          | 71         |

| 0    | 2.2 Score Calculating Unit                            | 74         |

| 3    | Hardware Sorting and Merging                          | 80         |

|      | 3.1 Parallel Sorting with Bitonic Networks            | 80<br>83   |

|      | 3.3 Hardware Merging Solutions                        | 85         |

|      | o.o Hardware Merging Boldwons                         | 00         |

| Cha  | apter VI $\diamond$ Results and Evaluation            | 91         |

| 1    | Hardware Implementation                               | 91         |

|      | 1.1 Adaptation to the Development Platform            | 91         |

|      | 1.2 Synchronizing the Processing Units                | 94         |

| 2    | 1.3 Synthesis Results                                 | 98         |

| 2    | Evaluation of the Hardware Model                      | 100        |

|      | 2.1 Benchmarking Environment                          | 100<br>103 |

|      | <ul><li>2.2 Scaling the Design</li></ul>              | 103 $104$  |

|      | 2.5 Terrormance Appraisar                             | 104        |

| Cha  | apter VII   Conclusion and Outlook                    | 109        |

|      | On the Associative Computing Engine                   | 109        |

| 2    | Future Work                                           | 111        |

| A    | andin A A On the Declination of Legentham             | 110        |

|      | pendix $A \diamond On$ the Realization of Logarithms  | 113<br>113 |

| 2    | Error Analysis                                        | 116        |

| _    | Exponential Function                                  | 118        |

| 9    | Expononour i unouon                                   | 110        |

| App  | pendix B $\diamond$ High Throughput Memory Controller | 119        |

| 1    |                                                       | 119        |

| 2    | SDRAM Timings                                         | 120        |

| List | of Abbreviations                                      | 123        |

|      |                                                       |            |

| Bib  | liography and References                              | 125        |

# List of Figures

| 1.1  | The process of retrieving information                           | 2  |

|------|-----------------------------------------------------------------|----|

| 1.2  | Storage system trends                                           | 4  |

| 1.3  | Hardware performance trends and memory wall                     | 4  |

| 1.4  | Hierarchical organization of the thesis                         | 6  |

| 2.1  | Flexibility, performance and power consumption trade-off        | 10 |

| 2.2  | Increasing the throughput using pipelining                      | 11 |

| 2.3  | Accumulator design using the cut-set technique                  | 12 |

| 2.4  | Retiming an architecture with feedback                          | 13 |

| 2.5  | Representation of an island-style FPGA                          | 16 |

| 2.6  | FPGA density and performance trends vs. CPU                     | 17 |

| 2.7  | Semiconductor memory devices classification                     | 19 |

| 2.8  | Example of pattern matching with the BM algorithm               | 21 |

| 2.9  | Deterministic automaton for pattern matching                    | 22 |

| 2.10 | Edit distance examples using dynamic programming                | 23 |

| 2.11 | Progression of the data in the insertion-sort algorithm         | 26 |

|      | Progression of the data in the selection-sort algorithm         | 27 |

|      | Progression of the data in the bubble-sort algorithm            | 28 |

|      | Progression of the data in the radix-sort algorithm             | 29 |

|      | Elementary sorting networks in a Knuth diagram                  | 30 |

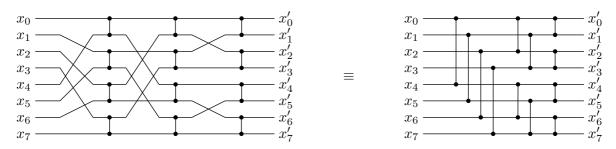

|      | Progression of the data in the bitonic sorting algorithm        | 31 |

| 2.17 | Bitonic merging network in a Knuth diagram                      | 31 |

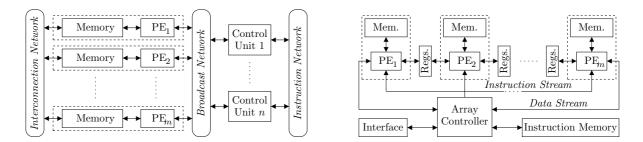

| 3.1  | Different associative processor designs                         | 36 |

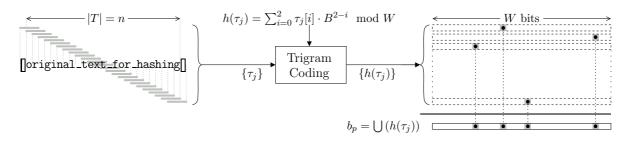

| 3.2  | Trigram based signature of a character string                   | 41 |

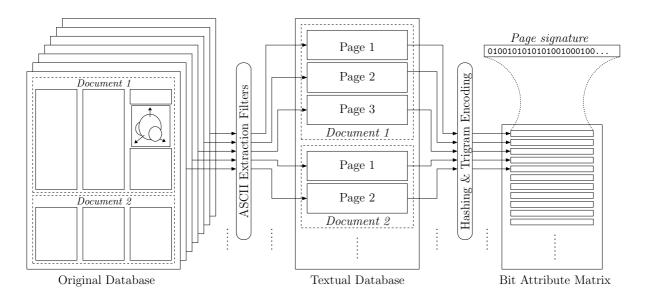

| 3.3  | Textual filtering and compilation of the BAM                    | 42 |

| 3.4  | A two phases search algorithm                                   | 44 |

| 3.5  | Possible distributions of the results after the filtering phase | 44 |

| 3.6  | Coding a long query string using trigrams                       | 46 |

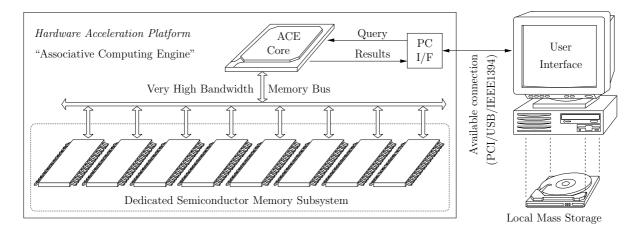

| 4.1  | Prospective hardware accelerator system                         | 52 |

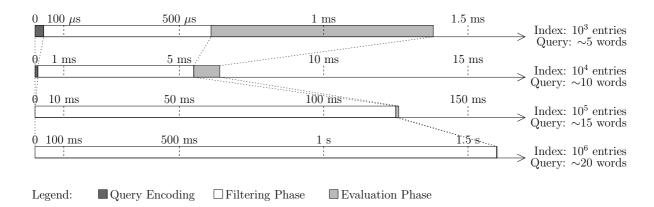

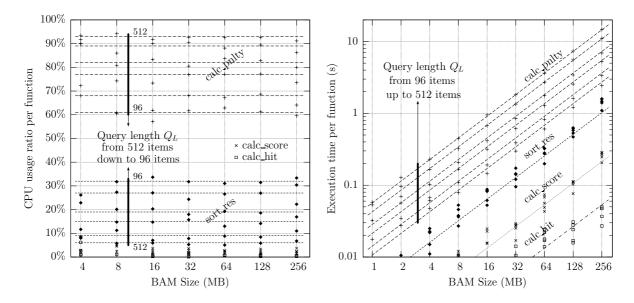

| 4.2  | Software profiling of the entire retrieval algorithm            | 54 |

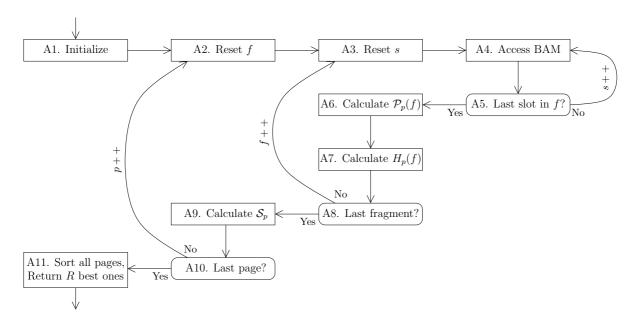

| 4.3  | Flow chart of the AAF algorithm                                 | 56 |

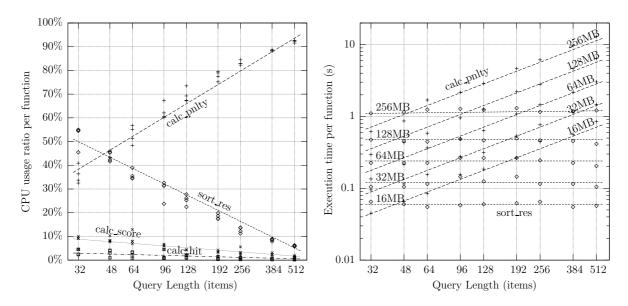

| 4.4  | Profiling measurements against query length                     | 57 |

| 4.5  | Profiling measurements against BAM size                         | 57 |

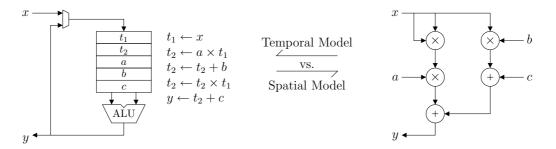

| 4.6  | Temporal versus spatial locality                                | 59 |

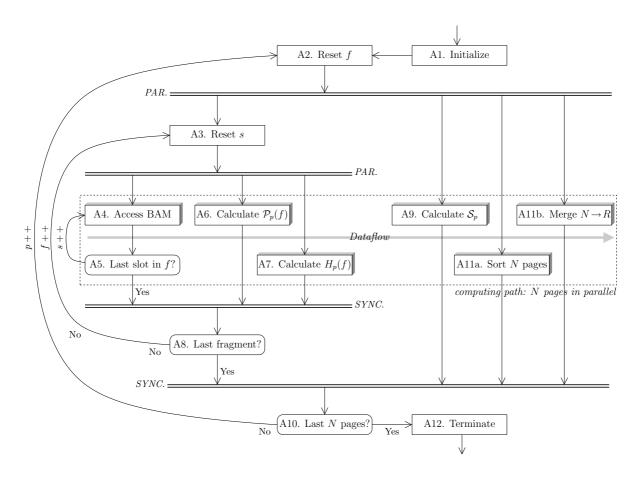

| 4.7  | Parallelization of the AAF algorithm                            | 61 |

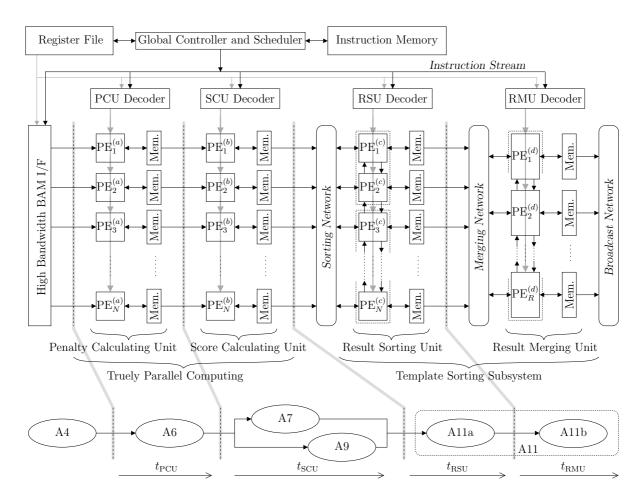

| 4.8  | Modular system architecture                                     | 63 |

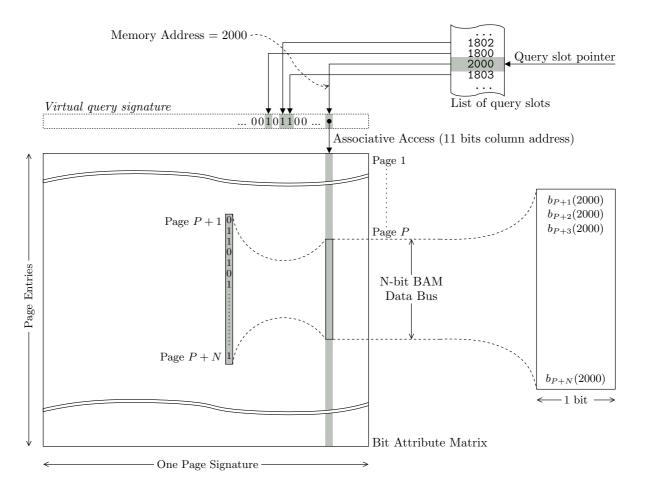

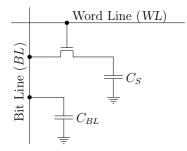

| 5.1  | Vertical accesses to the BAM                                    | 67 |

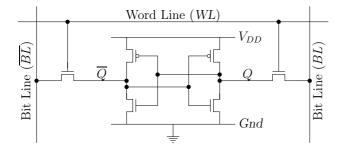

| 5.2  | Transistor level representation of a DRAM and an SRAM cell      | 68 |

| 5.3  | BAM mapping onto standard SDRAM memory devices                  | 70 |

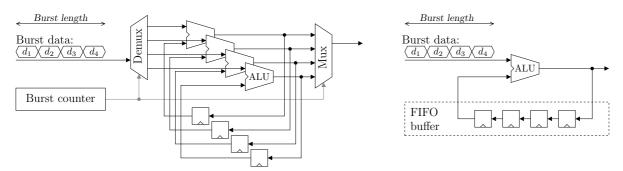

| 5.4  | Two possibilities to handle the burst accesses                  | 72 |

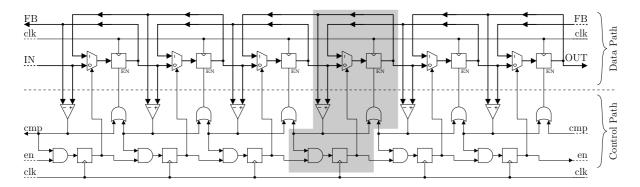

| 5.5  | Bit-level signal processing in the PCU                          | 73 |

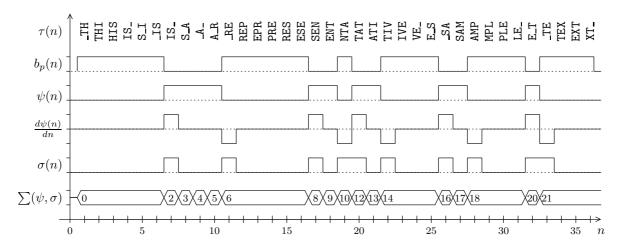

X List of Figures

| 5.6  | Calculation of the penalty using a state-machine.                | 73  |

|------|------------------------------------------------------------------|-----|

| 5.7  | RTL design of the Penalty Calculating Unit                       | 74  |

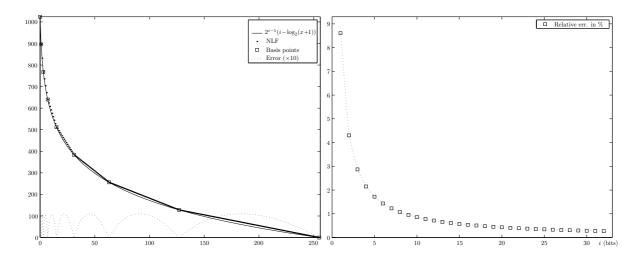

| 5.8  | Linear approximation of the binary logarithm                     | 76  |

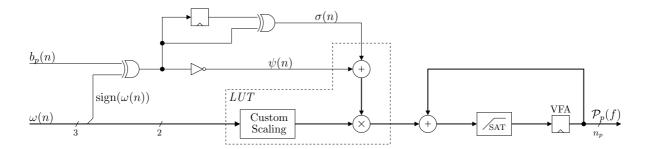

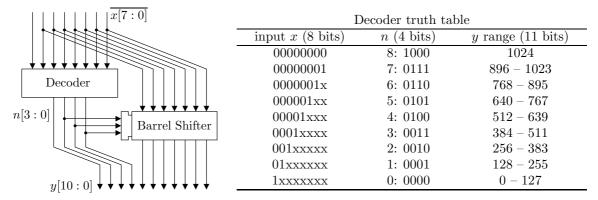

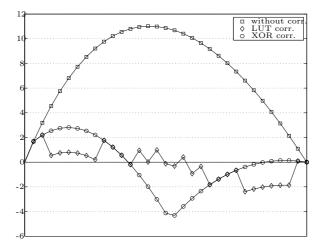

| 5.9  | Realization of the NLF using a Barrel shifter                    | 78  |

| 5.10 | Recurrent realization of the NLF module                          | 78  |

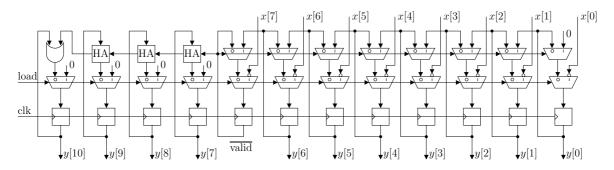

| 5.11 | RTL design of the Score Calculating Unit                         | 79  |

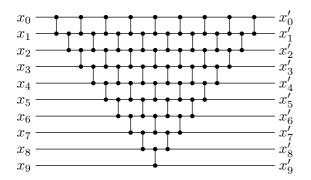

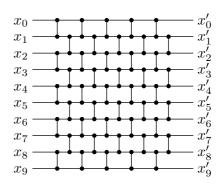

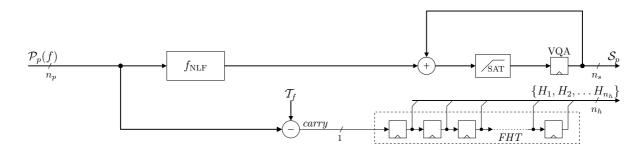

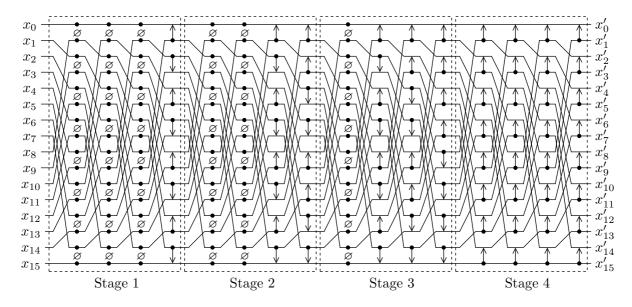

| 5.12 | Batcher's bitonic sorting network in a Knuth diagram             | 80  |

| 5.13 | Stone's regular structure pattern of the bitonic sorting network | 81  |

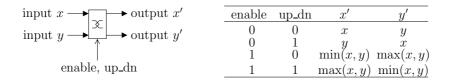

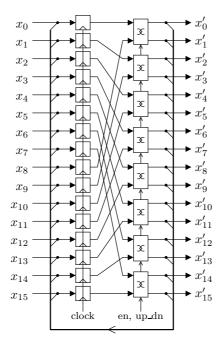

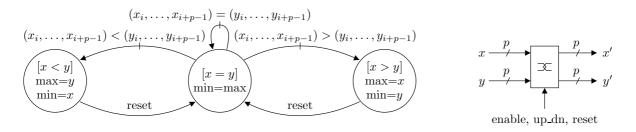

| 5.14 | Comparator set for sorting networks                              | 82  |

| 5.15 | Controlled switch comparators                                    | 82  |

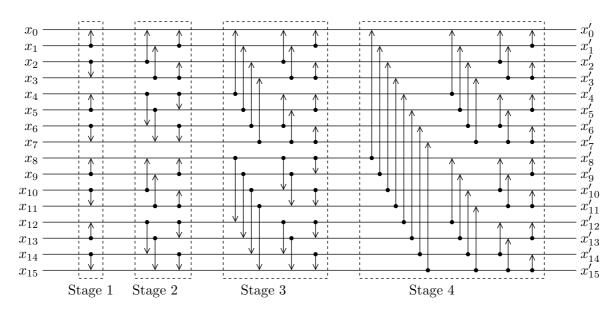

| 5.16 | A 16 keys recurrent bitonic sorting network                      | 83  |

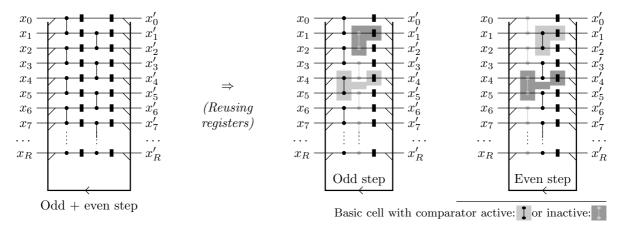

| 5.17 | Retiming switch comparator modules                               | 84  |

| 5.18 | Recombination of recurrent bitonic sorters                       | 85  |

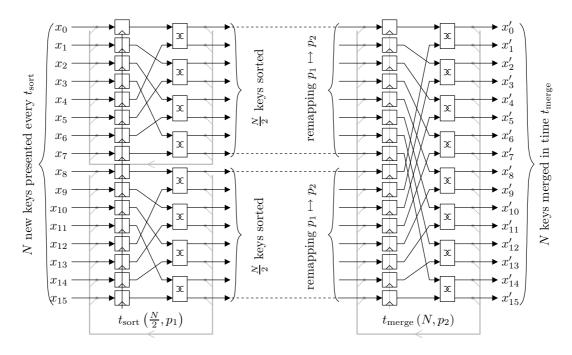

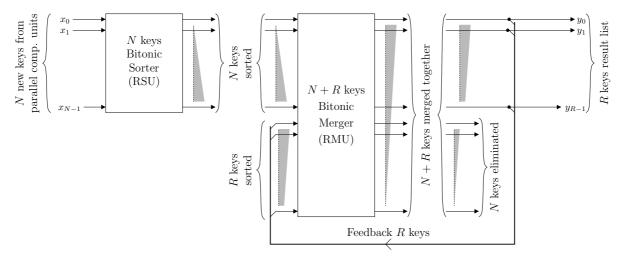

| 5.19 | Merging proposal based on bitonic sort algorithm                 | 86  |

| 5.20 | Merging proposal based on insertion sort algorithm               | 87  |

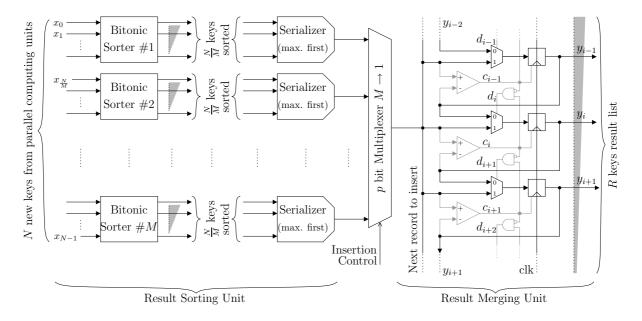

| 5.21 | Recurrent sorting network based on the odd-even transposition    | 88  |

|      | Sorting structure based on the parallel bubble sort algorithm    | 89  |

| 5.23 | Extremities of the bubble sorting structure                      | 89  |

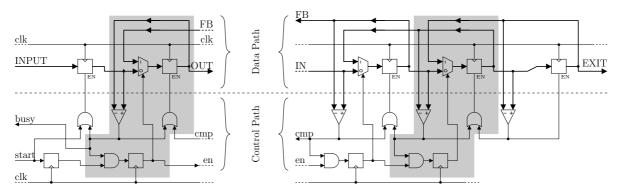

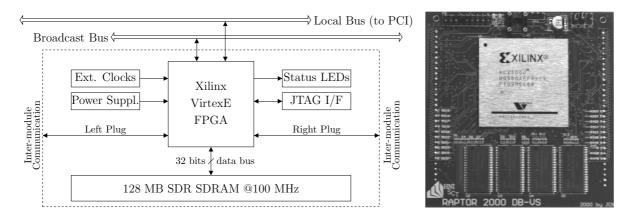

| 6.1  | Hardware prototyping module with FPGA                            | 92  |

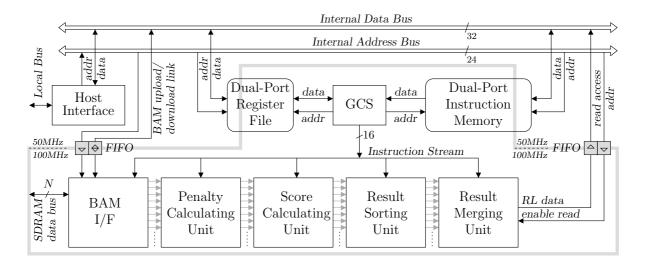

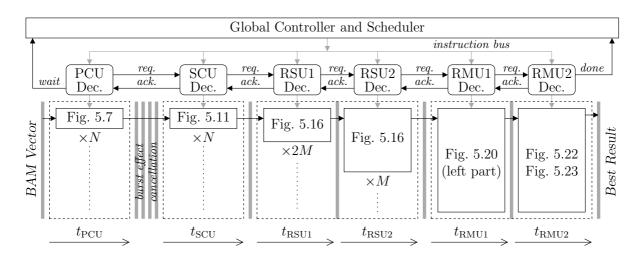

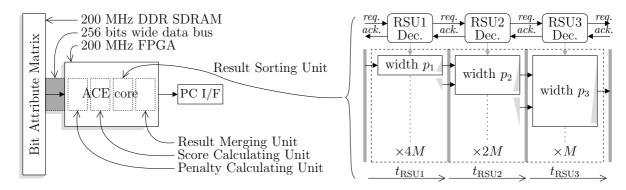

| 6.2  | System on chip architecture of the ACE                           | 93  |

| 6.3  | Dimensioning the data path of the ACE                            | 94  |

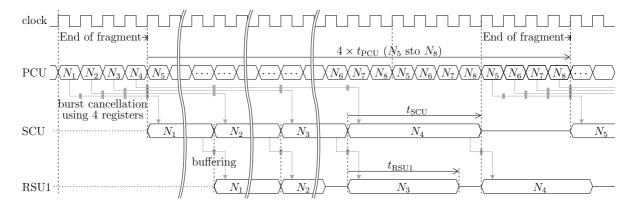

| 6.4  | Timing diagrams for PCU to RSU1                                  | 96  |

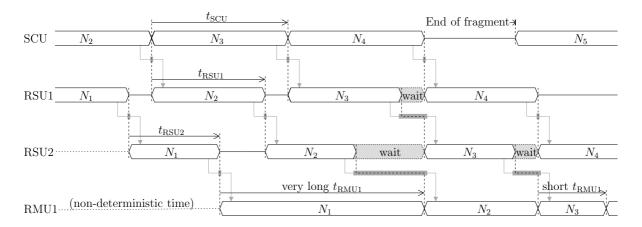

| 6.5  | Timing diagrams for SCU to RMU1                                  | 97  |

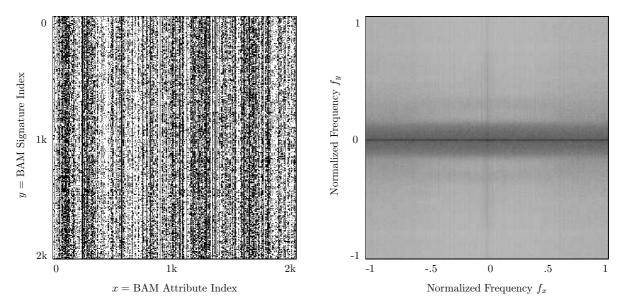

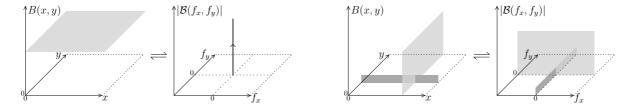

| 6.6  | Two dimensional Fourier transform of the BAM                     | 102 |

| 6.7  | Spatial frequency analysis: expectations and unwished results    | 102 |

| 6.8  | Using a three level sorting unit in the RSU                      | 103 |

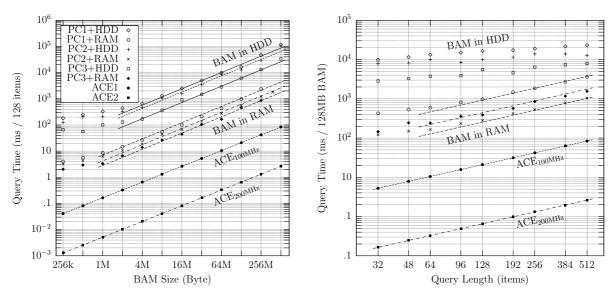

| 6.9  | Performance measurements of the AAF with different architectures | 106 |

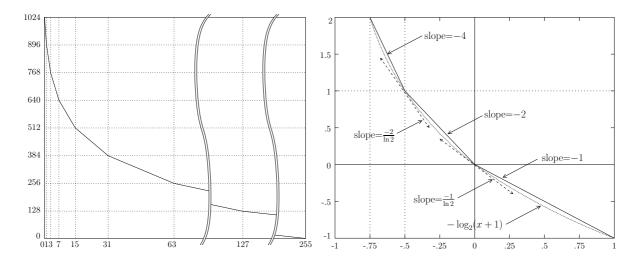

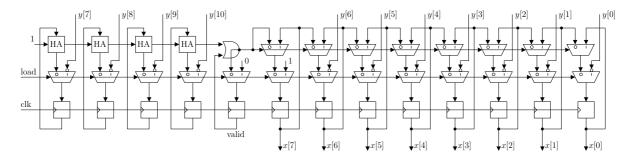

| A.1  | NLF for different input widths                                   | 114 |

|      | Absolute and relative error in the NLF                           | 115 |

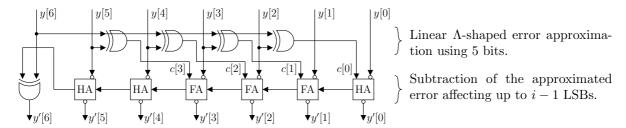

|      | Correction of the NLF using XOR gates                            | 116 |

|      | Correction of the NLF using a LUT                                | 117 |

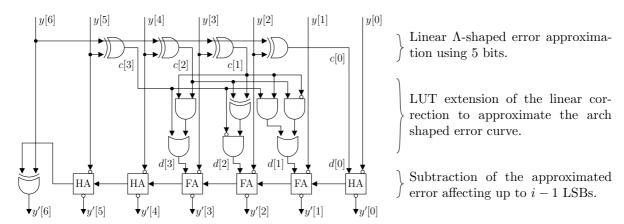

|      | Comparison of the absolute error in the NLF                      | 117 |

|      | Reverse NLF function with an 8-bit input                         | 118 |

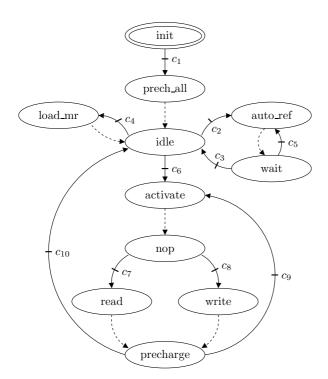

| B.1  | State machine of the memory controller                           | 120 |

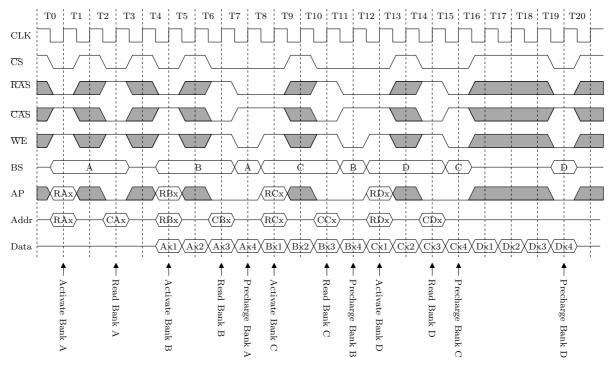

| B.2  | Timings diagram for the memory controller                        | 121 |

# List of Tables

| 4.1 | Function composition of the software model                       | 56  |

|-----|------------------------------------------------------------------|-----|

| 4.2 | Interface description in the modular design                      | 64  |

| 5.1 | Limited set of instructions of the ACE                           | 66  |

| 6.1 | Dimensioning the Result Sorting Unit for $N=32$                  | 98  |

| 6.2 | Bit widths used in the design                                    | 99  |

| 6.3 | Hardware resources listing on FPGA                               | 100 |

| 6.4 | Dimensioning the Result Sorting Unit for $N = 512 \dots \dots$   | 104 |

| 6.5 | Parameter listing of the software environments                   | 105 |

| 6.6 | Performance results of the test platforms                        | 106 |

| B.1 | Typical timing characteristics for standard SDRAM devices        | 121 |

|     | Description of the most relevant signal pins in standard devices |     |

## Introduction

ITHIN the scope of this work, we aim to demonstrate how a complex problem, e.g., retrieving information rapidly, can be efficiently solved using various well-established techniques as well as modern design methodologies. Our research has focused on the improvement of different algorithms and new computing methods that yielded highly significant results, as it will be presented in this document. But first of all, this chapter is dedicated to a global introduction to the concept of information retrieval, targeting the implementation of a generic text database system. Motivated by the noticeably long searching time needed by software applications even on the most recent computers, we foresee the necessity to move to hardware implementation and expose the envisioned development. Hence the detailed description of the organization of this thesis is depicted in the last section, where we give an overview of the completed research work.

## 1 Information Retrieval Systems

Fundamentally, Information Retrieval (IR) deals with the storage, the organization of and the access to some items, providing users an easy way to the information they are interested in. As a part of an IR system, data retrieval consists mainly in determining which documents of a collection contain the keywords of a query which is in this context a quite complex process based on a trade-off between speed and accuracy. As the algorithmic complexity is mastered by always more intelligent software programs, speed is basically the problem we want to address at the electronic hardware level in this thesis: How can we accelerate the process of retrieving information in a huge database system?

According to Baeza-Yates and Ribeiro-Neto [Bae99], three fundamental changes have occurred due to the advances in modern computer technology and the boom of the Internet. First it became a lot cheaper to have access to various sources of information,

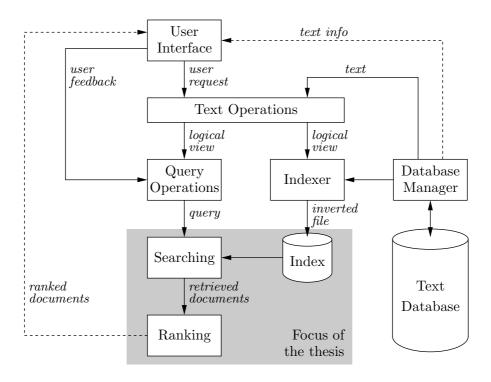

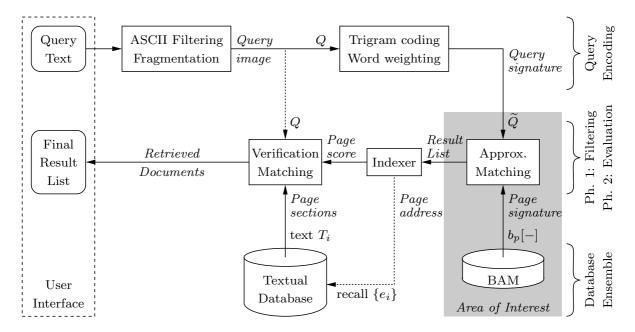

**Fig. 1.1.** A generic representation of the process of retrieving information from [Bae99] interpreted in terms of functional components. Our work in the current thesis focuses on the highlighted zone including the search within an index and the ranking of the retrieved documents.

reaching a wider audience than ever. Second, the advances in all kinds of digital communication provided greater access to various networks, implying that information sources are available and rapidly accessed even if distantly located. Third, the freedom to post and publish any kind of information to be shared has greatly contributed to the popularity of the World Wide Web (WWW).

Fig. 1.1 shows a generic architecture of an information retrieval system in terms of component subprocesses from [Bae99]. The system is divided into two parts sharing the same text operations, i.e., the user interface for the queries and the system part that provides text resources to be indexed for the search. The text operations transform the original documents and generate a logical view of them by specifying the structure of the elements that can be retrieved. Once the logical view of the documents has been performed, an index is built in order to allow fast searching over the large volume of data. In most of the cases, the index owns the structure of an inverted file for which each entry gives a word and a list of texts, possibly with locations within the text where the word occurs. Once the document database has been indexed, the user initiates the retrieval process by specifying a query which is parsed and transformed by the same operations applied to the text from the database. The retrieved documents obtained after processing of the query during the searching phase have to be sorted according to their order of relevance in the ranking phase before being sent to the user.

Hence, the explanatory model of an IR system must be considered as an introduction to the real problem of using hardware resources efficiently in order to accelerate the search process. There exist many algorithms which can be used for textual search. However, we intend hereby to analyze promising computing strategies which can handle long queries of misspelled words. Even the biggest search engines have a limited input string length in their inquiry process, e.g., Google with a maximum of ten words per query in 2005. Since query requests are inherently vague, retrieved documents might not be the expected answer and must be ranked according to their relevance to the query. As depicted in Fig. 1.1, sorting constitutes one of the three main areas related to IR systems that we address in this work, as well as searching and the use of a huge index file stored in dedicated memory devices. These domains are glued together through the realization of a efficient hardware platform for the acceleration of the whole retrieval process.

## 2 The Problem with Storage Devices

This section exposes briefly the problem of today's computerized systems to face an always more active user community greedy for information. Hence we aim to justify the need of a hardware support through scientific historical observations reported in various publications and through the evolution of the hereby concerned technologies.

### 2.1 Running into the Memory Wall

Undoubtedly, Moore's law keeps stressing processor technologies [Moo03, Olu05]. As we will see in Chapter II, the von Neumann paradigm which consists in improving fairly straightforward single processor architecture by increasing the clock frequency, already shifts towards Single Instruction Multiple Data (SIMD) or directly parallel processing technologies. However, while microprocessors follow an explosive growth in performance, DRAM-based memory systems fall behind creating the so-called memory wall [Bur96, McK04, Wul95]. In the beginning of the 90s, it has been estimated that the Central Processing Unit (CPU) speed of the fastest available microprocessors is increasing at approximately eighty percent per year [Bas91], while the speed of memory devices is growing at only about seven percent per year [Hen90]. Regarding our target application, it becomes clear that the most important hardware components dedicated to the storage of information within computer systems are the main memory and the Hard Disk Drive (HDD).

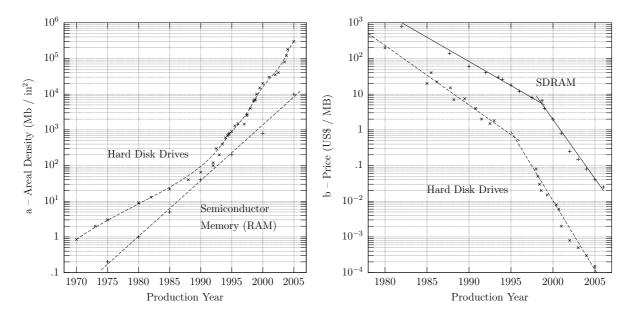

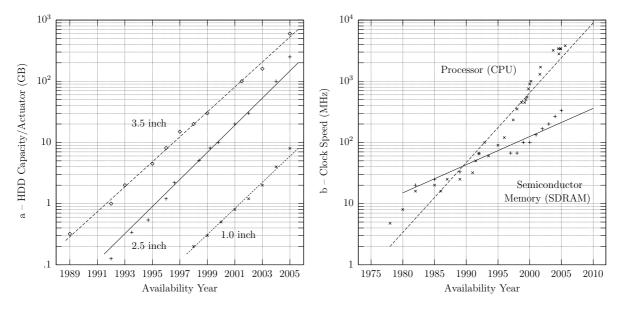

As seen in Fig. 1.2, the physical areal densities for both semiconductor memories and magnetic discs are exponentially growing while their price is continuously falling. According to Grochowski *et.al.* [Gro03], a significant evolution in disk drive form factor has occured over the past twenty years, as reported in Fig. 1.3-a, leading to an always smaller size with nonetheless higher capacity. Lesk's report [Les97] made estimates of disk sales and predicted necessary media sizes for storing multimedia information.

Fig. 1.2. Trends in a) areal density and b) price for storage systems including magnetic hard disk drives and semiconductor memory devices from [Bur96, Gro03].

**Fig. 1.3.** Evolution of **a)** the capacity of hard disk drives according to [Gro03] and **b)** of the clock frequency for semiconductor memory devices from [Ito01, Itr06, Rab03] and processors from [Bur96, Rab03] creates the memory wall [McK04, Wul95].

According to Lyman *et.al.* [Lym03], the world was producing more than one exabyte  $(1EB=10^{18}B)$  of unique information per year in 2000 and five in 2002. Furthermore in 2004, over fifty million web pages were new or changed everyday [Cas04].

Finally, Fig. 1.3-b plots the integration density of both processors and memory as a function of time. The memory wall [Bur96, McK04, Wul95], i.e., the growing gap between the curves on Fig. 1.3-b, is being an always more important problem in digital systems, as RAMs are not able to feed CPUs with data as fast as those can process

them. Due to increases in storage capacities, soon it will be technologically possible for an average person to access virtually all information ever recorded. However, even though we are able to store millions of electronic documents on magnetic media, the problem of retrieving information is more linked to active devices such as memory and processors than to HDDs.

### 2.2 Need for Hardware Support

The development of larger and larger Random Access Memories (RAMs) during the last fifty years has made the problem of searching a very interesting and well investigated realm. On the one hand, large databases tend to make the retrieval process more complex and more intricate, since having more data available means a bigger probability of matching and thus a longer list of possible responses to a stated query. On the other hand, large databases stimulate people to ask arbitrarily any complicated question about anything. Composing a very precise enquiry may regroup words with an explicit order of appearance and eventually exclude some other terms, as we know from our use of Internet search engines. More importantly, people might also be incited to perform big block searches, like entire paragraphs of text, with the ability to locate items when only a part of the key information is specified, hoping that the matching will be significant enough for the most relevant addresses to be returned. As we found out yet that there is no really efficient generic solution to this problem, we dedicate this thesis to the development of a hardware search engine for large databases.

Intelligent data manipulation, storage, retrieval, and interpretation are some of the most ubiquitous functionalities any IT device must provide. Regarding the problem of searching information, from a logical point of view, it is very inefficient to move in and out several hundreds of gigabytes (GBs) between memory and processor over a restricted size bus in order to retrieve the few relevant kilobytes (KBs). From a financial point of view, hardware manufacturers have to constantly add features to their devices in order to stay ahead of the competition. Besides data integrity and corruption control, a very relevant example of in-device tools a disk drive could be a low-level search functionality [Hug02]. However in today's systems, storage intelligence still resides on the computer side of the drive interface. In our opinion, the solution is to delegate this task where it belongs, i.e., to the storage medium itself or as close to it as possible. While this is practicable only by redesigning the memory chips or the HDD controllers themselves, there are simple ways of short-cutting the path between storage and CPU by using dedicated search coprocessors.

## 3 Organization of the Thesis

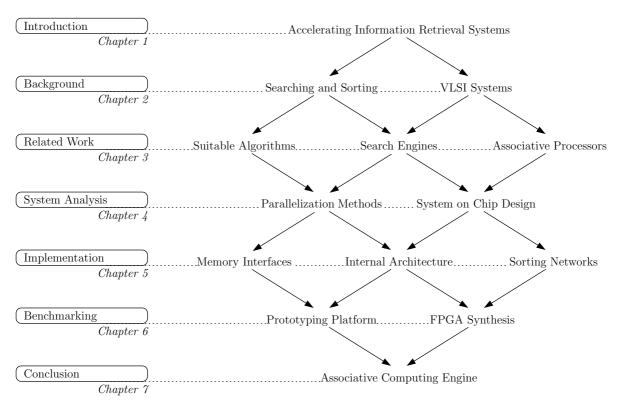

The organization of this thesis is essentially oriented towards the development of a hardware search engine based on an associative computing paradigm for textual queries. Figure 1.4 shows the relationship between all the subjects treated in this document, starting from the global concept of information retrieval down to the finalization of our Associative Computing Engine (ACE) on a hardware platform that provides a high speed-up potential for textual query applications.

**Fig. 1.4.** Hierarchical organization of the thesis: as the chapters follow the different steps in the development of the ACE, a logical flow relates the main ideas treated in this dissertation.

For that matter, after an introduction to IR systems in general and the necessity of making searches faster as given in chapter one, the second chapter sets the basis of this work by presenting state-of-the-art techniques for searching and sorting, as well as an overview on Very Large Scale Integration (VLSI) system design. These background principles provide the fundamental ideas from which the mainstream of the thesis is derived. Past and current research performed in related fields is reviewed in the third chapter. Not only does it confirm the importance of our contribution, but it also raises the expectations regarding the final result. A method relying on associative memory accesses [Lap92] is also presented in more detail, since we think it is the one with the biggest potential for being efficiently implemented as our database-searching accelerator.

With an emphasis on hardware design, chapter four is dedicated to the profiling of the selected algorithm and to the application of different methods which make the implementation extremely promising, using primarily parallelization techniques and large bus widths. The profiling of the software model based on the method described in the previous chapter permits an ideal partitioning of the operations between hardware and software and guides us through the parallelization of the algorithm. Moreover, a study on System on Chip (SoC) designs and associative processors must allow us to develop the best suited architecture for the porting of the previously chosen algorithm onto hardware. However, in the development of such a complex system, it is ineluctable to consider every single interface and data transfer at the lowest level of abstraction particularly for the memory subsystem. The choice of the storage media for data retention directly influences the overall performance of our database system. In chapter five, the selection of a given memory device class and the high data throughput necessary for obtaining the requested short searching durations brings hard area and time constraints into the system, especially in the second half which deals with the arrangement of the best matching candidates. We show how this problem can be solved in hardware using different design techniques and a well-advised mix of sorting algorithms, as introduced in chapter two.

Chapter six is porting the complete design of the ACE onto an FPGA-based prototyping platform in order to benchmark the system. A proof-of-work as well as a performance analysis is obtained through the comparison with software models running on different computers and other simulated hardware platforms. Finally, an overview of the achieved work is given in chapter seven, concluding on the performance of the ACE. Future work and further potential improvement directions for the developed system are proposed afterwards considering more up-to-date technological advancements.

## Background

AVING provided a rather large contextual description of the environment in which this thesis has been realized, we dedicate this second chapter to an overview of the state of the art in Very Large Scale Integration (VLSI) design as well as sorting and searching methods. The presented algorithms constitute the background knowledge which illustrates the theories related to information retrieval and allows a better appreciation of the work in progress. For the concrete realization of an Information Retrieval (IR) hardware accelerator, it is necessary to start with digital electronic system design. Secondly, the best known searching algorithms shall be reviewed in order to depict classical techniques used in IR based on text data. Finally, as sorting and searching are relatively close to each other, various algorithms shall be presented in order to provide a large overview of the different techniques that could be used for the realization of the final system.

## 1 Designing Digital Systems

Hardware accelerators are separate units close to Central Processing Units (CPUs) that perform some functions faster than a software program running on general purpose processors. They are usually made out of Integrated Circuits (ICs) communicating together over dedicated interfaces. The design of an acceleration platform requires not only a good knowledge about all the different kinds of chips that can be used to build a complete system, but also about how they can and must be combined in order to achieve top performance with a maximum efficiency.

### 1.1 Integrated Circuits Implementation Strategies

According to the literature [DeM94, Kun88, Rab03, Smi97, Wes93, Wol02], digital ICs are typically classified into three main categories. These include programmable standard architectures such as common microprocessors, programmable logic architectures such as Complex Programmable Logic Devices (CPLDs) or Field Programmable Gate Arrays (FPGAs) and application specific logic architectures highly optimized in terms of functionality, performance, power and cost.

#### 1.1.1 The Choice of an Architecture

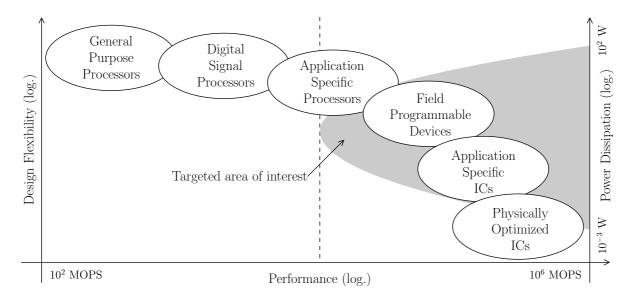

Fig. 2.1 represents the computational efficiency of different classified groups of ICs versus their flexibility, i.e., the inverse of the time required to implement a design, and power dissipation, according to [Syd03]. On the one side of the IC spectrum, programmable standard architectures emphasize General Purpose Processors (GPPs) as well as Digital Signal Processors (DSPs) or super-scalar processors. These are highly flexible generic devices, the functionality of which is determined by loaded software code. However, since this code is executed sequentially, the processing time of a function can be quite long. Such devices are therefore typically used in applications which allow a longer response time. As we are building a specific acceleration unit, we might want to trade flexibility for performance.

On the other side of the IC spectrum, application-specific logic architectures emphasize many kinds of Application Specific Integrated Circuits (ASICs) which differ mostly from the way they were designed. The highest degree of optimization is obtained with full custom implementation, while semi-custom devices offer quicker design processes.

**Fig. 2.1.** More flexibility has to be paid off by a larger power dissipation from [Syd03]. As we strive for performance, our area of interest includes FPGA and ASIC devices allowing an averaged power consumption for a respectable design flexibility.

Located in the middle of the spectrum, as a compromise between flexibility and performance, field programmable devices are gate arrays which provide highly standardized means to implement digital integrated circuit designs. They are manufactured as regular arrays of patterned blocks of transistors which can be interconnected to form logic elements such as gates, flip-flops and multiplexers [Bet99].

#### 1.1.2 Pipelining Techniques

Digital systems are usually controlled by one or a set of clock signals, which ease the design as well as the development and the verification of complex architectures through a synchronous operation mode. Dividing a system into many smaller sub-circuits, hence separated by registers placed on their respective outputs, permits a global synchronization of the data flow with respect to the system clock triggering these registers. However in a synchronous work process, the highest possible system clock frequency and thus the maximum data throughput is conditioned by the operating time of the slowest sub-circuit of the system. Propagation delay compensation between slower and faster parts of the system is not possible within one clock domain.

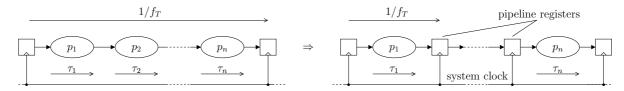

Fig. 2.2. Pipelining consists in inserting registers between the different parts of a computational path. This method increases the system frequency  $f_T$  and the data throughput as well.

There exist different methods to increase the throughput of digital synchronous systems. Pipelining consists in inserting levels of registers within a series of logic blocks in order to break the critical path, i.e., the longest signal path of the design created by the logic gates between two registers. As seen in the left part of Fig. 2.2, for n chained asynchronous logic elements with a respective processing time  $\tau_1, \tau_2, \ldots, \tau_n$  where registers controlled by a system clock of frequency  $f_T$  are located at the extremities of the chain,  $f_T$  should respect the condition

$$f_T \le \frac{1}{\tau_1 + \tau_2 + \ldots + \tau_n} \tag{2.1}$$

so that the correct propagation of the logic levels is assured. The intrinsic delay caused by the typical setup and hold time of the registers is hereby neglected. The insertion of additional registers, as seen in the right part of Fig. 2.2, permits a pipelined processing of the data, that is to say the result of a part  $p_i$  of the system can be safely processed by the following part  $p_{i+1}$  while the next dataset from  $p_{i-1}$  is input to  $p_i$ . Hence, the resulting system clock frequency  $f_T$  depends on the longest propagation delay of all the parts of the system only, such that

$$f_T \le \frac{1}{\max\left(\tau_1, \tau_2, \dots, \tau_n\right)}.\tag{2.2}$$

Theoretically, if all the logic blocks between the pipeline registers have approximately the same propagation delay, the pipelined circuit outperforms the original one by a factor equal to the number of pipeline register levels. However, the overall latency of the complete circuit grows with the depth of the pipelining. This latency, expressed in terms of clock cycles, is defined through the processing time of a pipelined system between the reading of the input dataset and the presence of the result at the output register.

In this work, we make large use of the pipelining technique in order to be able to handle the data fetched from the memory rapidly enough. Not only are we able to process the data faster through an increased system clock frequency, but also work on a huge amount of data concurrently and make a very efficient use of the hardware resources.

#### 1.1.3 Cut-Set Technique

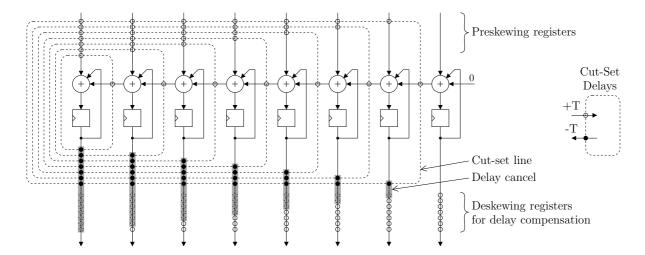

Pipelining is very practical for signal processing algorithms since these are typically applied to a continuous data flow, in comparison to data-processing algorithms in which conditional branches depend on the information currently treated. Widening the principle of pipelining, the cut-set technique [Kun88] is a method permitting the redistribution of propagation delay within an electronic circuit without having to change the actual implementation of the algorithm. Practically, it consists in grouping a set of different processing elements of an architecture together in a virtual box where every incoming signal will be delayed by one clock period (T) and every outgoing signal will be given the opposite negative delay (-T). In Fig. 2.3 showing a synchronous accumulator subjected to pipelining, these delays are respectively represented by an empty circle and a full colored circle.

As negatively delaying register cannot exist physically, a supplementary block of registers must be inserted for the synchronization of the output signals. Moreover, if

**Fig. 2.3.** Design of an accumulator using the cut-set technique in order to increase the clock frequency. The critical path composed by the carry signal of the full-adders is intersected by each cut-set line, the number of which equals the final latency in clock cycles.

the output of the accumulator has to be processed word-wise, these deskewing registers are necessary for data consistency. They permit canceling the negative delay  $n \times (-T)$  earned through n cut-set lines and hence allow a physical realization of the architecture. Applying the cut-set technique consequently ensures a functional equivalence of the thus pipelined processing network. As an example, Fig. 2.3 assumes that the effect of the registers with the negative delay (-T) has been compensated by the dotted deskewing registers in the grey area. By showing how the method works at the bit level, we can easily extend the idea to the system level, i.e., when a bit line becomes a bus. Moreover, when cut-set lines interface directly inputs or outputs, negative delays can be ignored if the timings are reconsidered, i.e., the input word must be presented earlier or the output has to be read later accordingly to the number of delays neglected.

#### 1.1.4 Retiming Recurrent Architectures

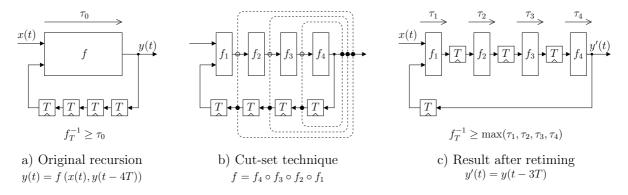

Pipelining increases the internal processing clock frequency  $f_T$  of a system through the insertion of intermediate registers on the data path. As a direct consequence, the latency of the processing part strongly influences the pipelining of recurrent structures in which data is fed from the output back to the input. The solution remains in the compensation of the resulting latency of the data path through the functional delay of the feedback loop. In this case, an architectural retiming based on the cut-set technique can provide an increase of the throughput.

**Fig. 2.4.** Retiming a recurrent architecture is possible when the latency of the data path after pipelining can be compensated by the functional delay of the feedback loop.

Fig 2.4 shows the example of a system f with a propagation delay  $\tau_0$  which includes a feedback loop for a computation y(t) based on an input value x(t) and a previous result y(t-4T) with  $T = f_T^{-1}$ . When a recursive function f owns a loop delay of  $n \times T$ , it becomes possible to part the system in maximally n sub-functions  $f_1, \ldots, f_n$  with a respective propagation delay  $\tau_1, \ldots, \tau_n$  and increase the system clock frequency  $f_T$  in relation to (2.2). With the condition that the loop delay stays larger than T, it can be minimized while the throughput gets maximized.

### 1.2 Microprocessor Design Techniques

The original goal of a processor is to perform mathematical calculations in a very fast, flexible and reliable manner. With the advances of technology, they reach always higher performance levels in terms of speed, while the power consumption has continuously been reduced. If greater connectivity helps build larger and more parallel systems, more architectural specialization is required for specific markets such as multimedia processing or pattern matching. In this section, we aim to give an evolutionary overview on processors in general, because we make wide use of these design concepts in our work. For further reading, we would like to refer to Hennessy and Patterson text books [Hen90, Pat97a] which provide a broad framework for computer architectures.

#### 1.2.1 Instruction Set Architecture

Considered as a generic term, a microprocessor is a digital semiconductor IC which typically serves as a Central Processing Unit (CPU) in a computer system and generally includes different components with specific functions such as the data path, the control path, some memory units, a clock distribution network and transceiver circuitry. The history of GPPs began more than fifty years ago, where CPUs were simply programmed using machine code. As industrial applications became more complex, the concept of portability permits to move up to larger computers and stay compatible at program and data level. In order to make an entire family of computers run the same software, the adopted solution was to produce a quite complete and capable reference instruction set. The Complex Instruction Set Computer (CISC) was able to fetch fewer instructions from the main memory that could remain slow and less expensive. The evolution led to the development of better and more efficient compilers to bridge the semantic gap between the high-level language of the algorithm and the machine code.

However, most compilers use only a small subset of the available instructions. Redesigning the processor for supporting a simpler instruction set, with less addressing modes but with more internal registers, made it faster and less expensive at the same time. Hence the resulting Reduced Instruction Set Computers (RISCs) yield in a very simple core CPU running at very high speed, supporting the exact same sorts of operations the compilers were using on a register basis [Hen90].

#### 1.2.2 Parallelization of the Operations

There exist mainly two different standard architectures in processor design, both with advantages and drawbacks. For the Von Neumann machines, programs and data are mixed in a single memory device, requiring sequential accessing which produces a bottleneck. For the Harvard machine, they occupy separate memory devices and can be accessed simultaneously. These design variations remain a trade-off between internal complexity of the CPU and throughput to the program memory.

A very important break-through began with the use of instruction pipelining, in which the processor works on multiple instructions in different stages of completion.

With this technique, processors can be clocked almost as many times faster as there are pipelining stages. However, in the typical case of a conditional branch command, the processor must know the result of the previous operation and hence has to wait for the pipeline to be empty.

Another improvement of the structure of the processor came with the introduction of additional Arithmetic Logic Units (ALUs) within the data path in order to execute multiple instructions in parallel, implying that these are not dependent on each other. The resulting architecture is qualified as super-scalar processor and provides a well-suited and efficient platform to applications with a high level of instruction parallelism. Following this idea, the parallelization of the core of the processor resulted in a new conceptual idea which consists in combining different kinds of instructions into an internal single Very Long Instruction Word (VLIW). Provided with a diversity of specialized execution units, the CPU is capable of executing all of the instructions contained in the instruction word, in parallel.

#### 1.2.3 Parallelization of the Data

A vector processor is a CPU designed with a Single Instruction Multiple Data (SIMD) architecture that is able to operate on multiple data elements simultaneously, taken into account the possibility to pipeline the instructions and the data as well [Pat97a]. Computing architectures where many functional units perform different operations on different data simultaneously are qualified of Multiple Instruction Multiple Data (MIMD). A recent industrial example that shows an extensive use of this concept presented with the Cell processor in [Dho05, Moo06] was designed to bridge the gap between conventional desktop processors and more specialized high-performance processors such as graphics chips. Its architecture includes a main multi-threaded processor core, eight fully functional coprocessors and a specialized high-bandwidth circular connecting data bus. The main processor is not intended to perform all primary processing for the system, but rather to act as a controller for the other eight coprocessors which handle most of the computational workload.

Nonetheless, from the commercial point of view, the cost of multi-processor devices must be justified by the applications that run on it. When designed for high-performance markets, these devices require customization of each internal element to achieve frequency, power dissipation and chip area goals. As power consumption essentially has made progress stop in conventional processor core development, manufacturers try to find new ways to utilize the ever-increasing transistor budget more effectively. Olukotun et.al. [Olu05] describe the advent of Chip Multi-Processors (CMPs) and depict the next system development steps through the necessity to port latency-critical software into multiple parallel threads of execution.

### 1.3 Field Programmable Gate Arrays

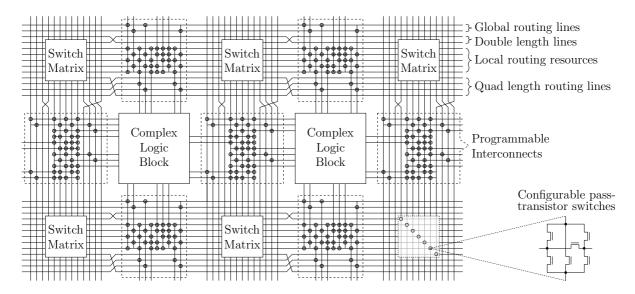

Since their introduction in the mid 80s, Field Programmable Gate Arrays (FPGAs) have become one of the most popular implementation media for digital circuits. Similarly to Complex Programmable Logic Devices (CPLDs), FPGAs are digital devices based on configurable logical cells and configurable interconnect structures. They have the ability to implement any circuit by being appropriately programmed [Bet99, Wol04]. As depicted in Fig. 2.5, FPGAs typically include Complex Logic Blocks (CLBs), routing lines of different lengths for global and local communication interconnected through switch matrices, line buffers and programmable interconnects that incorporate the logic into the routing network and thus form larger circuits. Grouped in clusters, CLBs are used to implement various logic functions of a larger number of inputs by means of Look-Up Tables (LUTs) or multiplexers. They include registers which permits the design of synchronous circuits and the implementation of local memory blocks. Programming bits configure the output response of the CLBs as well as the pass transistor switches for the routing.

As they are manufactured using the latest technologies, they provide a very high-capacity in equivalent ASIC gates which makes them a good alternative for large designs. Following Moore's law, the number of gates and features inside FPGAs has increased so dramatically that they have progressed to a point where System-on-Chip (SoC) [Wol02] designs can be built on a single device. They compete with capabilities that have traditionally been supplied through ASIC devices only and offer a lot of advantages compared to DSPs or general-purpose processors. Not only do they give system designers the possibility to parallelize their architectures, but they provide an excellent density of hardware Intellectual Property (IP) and lower the price per Giga Operations Per Second (GOPS) rapidly. Moreover, it has been shown that they achieve greater performance per unit of silicon area than processors [DeH00b]. This gain however has to be paid

**Fig. 2.5.** Representation of a generic island-style FPGA which includes CLBs, switch matrices, programmable interconnects and routing lines of different lengths.

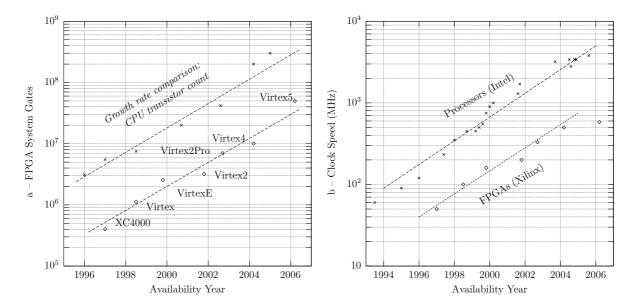

**Fig. 2.6.** General-purpose processors can be compared with programmable logic devices. In **a**) as for CPU [Int06], FPGA [Xil06] industry trend has an exponential growth in density and **b**) in clock frequency.

off by a relatively larger power consumption. Given for comparison in Fig. 2.6-a, the transistor count in processors grows with the same rate as the amount of system gates in the FPGA devices. Fig. 2.6-b reports that the technology behind FPGAs allows the realization of digital systems that can be clocked only four to five times slower than general purpose processors.

Often seen as their rivals although they are not meant to supersede them, FPGAs provide many advantages against ASICs. As a fast procedure for implementing hardware while allowing a rapid functional verification, they yield an improved time-to-market and a low NRE (Non-Recurring Engineering) costs [Bet99, Rab03] so that they are extremely adapted for small to medium volume productions. However, due to a high signal delay and power consumption, they cannot permit an optimal utilization of the silicon area and come at the expense of lower performance and integration density. In addition, routing problems can limit the flexibility and the implementability of rather complex or highly interconnected systems, as we have experienced in this work, e.g., with the sorting networks. Moreover, physical constraints such as potential clock-skew may appear in late design phases, especially through the communication with peripheral units or in systems with multiple local or global clock domains, e.g., with the use of external synchronous memory chips.

In most of the applications, the ultimate goal is to reach the maximum performance of a system in terms of speed and throughput. On the one hand, the flexibility offered by microprocessor or DSP clusters through their high-level programmability is very attractive, but multi-processor programming is extremely hard, especially for real-time applications. Compared to FPGAs, they dispose of limited I/O capabilities, a high power consumption for a low computational density. On the other hand, with a lack of flexibility and long design cycles, ASICs are meant for large volume productions. As they

are not error-tolerant during system conception, they would not allow any application change or functional design improvement. Therefore, we estimated that FPGAs would be the most suitable choice for the implementation and the verification of our present research work.

### 1.4 Semiconductor Memory Devices

When it comes to memory devices, there are several different technologies available for use in modern integrated systems. However, not all of them are suitable for the implementation of a fast database search engine. The type of memory unit which is preferable for a given application is a function of the required memory size, the time it takes to access the stored data, the access pattern, the application itself and the system requirements [Rab03]. Depending on the level of abstraction in a design, the size of the memory needed in the system might be expressed in different manners. On the one hand, from the side of the application developers, the ACE platform deals with signature files of a given length, such that the total amount of memory needed would be expressed in terms of signatures or words, e.g., the database must be able to store up to one million signatures. On the other hand, hardware system architects are more likely to refer to this quantity using bytes or megabytes, e.g., the size of the database must be of at least ten gigabytes.

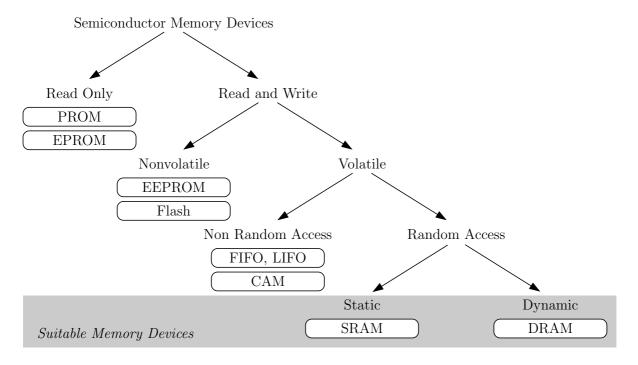

Basically related to the functionality implemented in a digital system with data storage, there exist different classes of memories, as shown in Fig. 2.7. First, a distinction is made between ROM (Read Only Memories) and RWM (Read & Write Memories) [Rab03]. Secondly, whether it belongs to the nonvolatile or volatile class, i.e., whether the contents are kept or lost when power is turned off, is also an early selection criterion. Then a distinction can be made for the volatile RWM devices between the ones with a restricted access resulting in either faster access times, smaller area or a special functionality such as FIFO, LIFO, shift registers and the ones with a random access (RAMs). The latter split into the static and the dynamic RAM categories. The primary difference between them is the lifetime of the data they store. SRAM retains its contents as long as electrical power is applied to the chip. If the power is turned off or lost temporarily, its contents will be lost for ever. By contrast DRAM has an extremely short data lifetime, typically about a few milliseconds, and they require a dedicated controller refreshing the data periodically before it expires. Flash memory combines the best features of the nonvolatile RWM devices described above. They are high density, low-cost, nonvolatile, fast in reading, and electrically reprogrammable. However, a high throughput to a huge database for the ACE platform would be reached at a much higher cost than with a RAM solution.

When deciding which type of RAM to use, a system designer must consider access time and cost. Timing parameters play an important role in the choice of a memory. In an electronic design, one has to consider the read access time, i.e., the delay between the read request and the moment the data is available at the output, the write access

time i.e., the delay between the write request and the final writing of the input data into the memory and the cycle time, i.e., the minimum time required between two successive read or write operations. Depending on the technology of the memory devices, these timings present huge variations [Rab03]. SRAM devices offer extremely fast access times but are much more expensive to produce. Generally, SRAM is used only where access speed is extremely important. A lower cost-per-byte makes DRAM attractive whenever large amounts of RAM are required. Many embedded systems include both types: A small block of SRAM, in the region of a few hundreds kilobytes, along a critical data path and a much larger block of DRAM, perhaps tens of megabytes, for general-purpose storage.

**Fig. 2.7.** Classification of semiconductor memories. Devices suitable for the realization of a search engine within a digital system using an external database are static and dynamic Random Access Memories (RAMs).

When massive amounts of storage are needed, semiconductor memories tend to become too expensive so that more cost-effective technologies such as magnetic and optical disks should be used instead. However, although they provide extensive storage capabilities at a low cost per bit, they tend to be quite slow, and they can definitely not be a part of a SoC design, which makes them unsuitable for the ACE platform. If both SRAM and DRAM are suitable for the realization of the ACE, it should be clear that the real challenge lies in the conception of a platform based on the much more complex DRAM devices compared to the relatively simple SRAM type.

## 2 Pattern Matching in Strings

Introduced in Chapter I, searching is a popular problem. In the last decades, many algorithms have been developed, studied, published, e.g., in [Bae99, Hyy02, Hyy04, Hyy05, Knu97, Nav02, Nav05, Sed88, Sun90], and still constitute an excellent reference in the field. As a matter of fact, texts remain today the main form of information exchange although data is stored in many advanced formats. Since our target is the retrieval of information hidden in texts, we concentrate in this section on the most relevant string matching algorithms.

### 2.1 Classical Algorithms

A text is basically any sequence of symbols or characters drawn from an alphabet  $\Sigma$ , such that when a query string Q of length m is to be found in a text T of length n from a collection, string matching requires to point out all the occurrences of Q in T [Bae99]. Classical string matching algorithms are based on character comparisons. First of all, the Brute-Force (BF) algorithm suggests itself naturally with an  $\Theta(mn)$  complexity<sup>1</sup>. It consists in comparing every single character of Q with one of T sequentially from the left to the right. If there is a match, then the next characters are respectively compared until there is a mismatch or a complete match. In either case, the pattern Q is shifted one position to the right and the sequence of comparisons starts from the beginning. The algorithm ends when the remaining number of characters in T is lower than m and returns the locations where Q was found in T if any. The odds are its simplicity and the absence of preprocessing.

By taking advantage of the pattern alignment knowledge obtained during previous comparisons, the Knuth-Morris-Pratt (KMP) algorithm [Knu77] reduces the time for searching Q in T to  $\Theta(n)$ . However, a preprocessing time in  $\Theta(m)$  is necessary to analyze the searched pattern Q in order to know after each mismatch the next possible beginning of Q in T. The algorithm makes its greatest gain over a naive string matching when it can skip the most characters at a time.

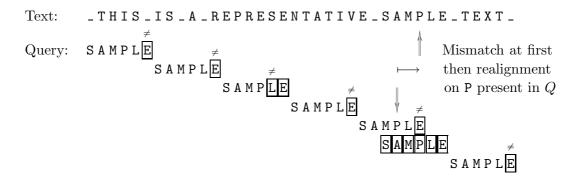

Similarly to KMP, the Boyer-Moore (BM) algorithm [Boy77] uses a backward comparison scheme for the search pattern Q while scanning the text T from left to right. The key of the method is that in case of a mismatch with a character that doesn't appear in the pattern at all, then it can be shifted of m positions to the right, as there is no chance that the pattern starts within the next m characters. The advantage is that in the best case, only one in m characters needs to be checked, so that it can run in  $O(\frac{n}{m})$  in average. Moreover, small amounts of iterations are reached when the alphabet  $\Sigma$  gets bigger and the length of the pattern m smaller [Sed88]. An example of pattern matching using the BM algorithm is illustrated in Fig. 2.8. There exist many improved variations of the method in the literature and we would like to point to the bibliographical references for more details.

<sup>&</sup>lt;sup>1</sup>According to Knuth's notations from [Knu76].

**Fig. 2.8.** Example of pattern matching using the Boyer-Moore algorithm. The query word "sample" is compared backwards character per character to the text from the left to the right. 13 comparisons marked  $\square$  were performed within 7 pattern positions, i.e., 6 shifts.

When large texts must be scanned for a search pattern, a sequential method is not a good option since its time complexity depends in the best case linearly on the size of the texts. An ordering relation such as a sorted table or a tree would reduce the time needed for retrieval to a logarithmic complexity. For frequent queries, the cost of the preprocessing, i.e., the sorting of the words of the text into a table, becomes negligible as it must only be performed once. In binary search trees for instance, every node's left subtree has keys less than the node's key, and every right subtree has keys greater than the node's key. Searching for a specific value consists in a recursive process that is performed beginning by examining the root, finding the median, determining whether the desired value comes before or after it, and then proceeding to the remaining half in the same manner, e.g., in the way of the divide-and-conquer algorithm and the dichotomic search [Knu97, Sed88]. Practically best suited for software solutions, trees are usually implemented with pointers in order to be flexibly extended but may yield a variety of constraints on how they are composed. However in this thesis, we are looking for a much more flexible and faster method for retrieving textual information in huge pools of texts, which shall turn out to be extremely well suited for a later hardware implementation.

### 2.2 Flexible Pattern Matching

Owning more flexibility means being able to find approximate matches to a pattern in a text string. Practically, an approximate matching algorithm must be given a variable that specifies the biggest number of misspelled characters in the query words. Compared to exact matching, it allows a certain number k of differences at the item level, e.g., characters in the case of texts. This measure of dissimilarity is known as edit distance and encompasses several popular measures such as Levenshtein or Hamming distance [Nav01]. In information theory, the Hamming distance between two strings is the number of positions for which the corresponding symbols are different with the restriction that these are of the same length. As an extension to this measure, the edit

distance is given by the minimum number of operations needed to transform one string into the other, where an operation is an insertion, deletion, or substitution of a single character.

Most approximate matchers used for text processing are based on regular expressions. Per definition, these are strings that describe a set of patterns without listing them all, according to certain syntax rules which provide a lot of flexibility in a search. They are commonly used in computer programs that deal with texts in order to manipulate strings efficiently. For instance, the expression "^(ex|s)amples?\$" matches the words "example" or "sample" in singular or plural, when these are not followed or preceded by any other character. However, writing regular expressions is a quite difficult task for unexperienced users and even though tools exists that simplify the work, the method loses efficiency when queries becomes too large or too fuzzy.

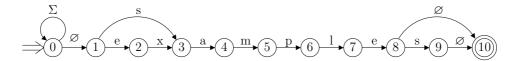

For the implementation of regular expressions, finite state automata can be designed to recognize patterns in strings. As seen in Fig. 2.9, a deterministic finite state automaton that matches the patterns "sample", "samples", "example", and "examples" includes eleven states with one input and one successful output state. Depending on the character read, a match causes a transition to the next state and a mismatch exits a global failure stopping the search process.

Fig. 2.9. A deterministic finite state automaton for the recognition of the expression "^(ex|s)amples?\$". Each arrow consumes one input and Ø stands for any spacing character.

With this method, we can dispose of a system for flexible retrieval that permits an approximate pattern matching in strings to the cost of a dynamically programmable state machine. However, the complexity linked to a hardware realization is hardly measurable as it depends on the way the reconfigurability is supported in the architecture. In this case, the degrees of freedom owned by the user to define a query impact the quantity of resources necessary for the implementation of the finite state automaton in terms of memory and computational power.

### 2.3 Dynamic Programming

As a technique to facilitate the solution to sequential problems, dynamic programming progressively builds a set of scores utilizing the decision made at a given stage of the algorithm as the conditions governing the succeeding stages [Cor01, Sed88]. Based on an algorithm presented by Wagner et.al. [Wag74], this principle can be used to calculate the edit distance between two strings, as depicted in Fig. 2.10. For this, it is necessary to define a cost function  $c_{i,j}$  at the position (i,j) in the matrix of results, where  $c_{i,j}$  depends on the previously calculated costs and on the local distance  $d(x_i, y_j)$ . An exemplary cost

| $M_1$        | Ø | m | a | $\mathbf{t}$ | $\mathbf{c}$ | h | i | n | g | $M_2$ | Ø | G | A | A | Τ | Τ | С | A | G | $\mathbf{T}$ |

|--------------|---|---|---|--------------|--------------|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|--------------|

| Ø            | 0 | 1 | 2 | 3            | 4            | 5 | 6 | 7 | 8 | Ø     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9            |

| $\mathbf{m}$ | 1 | 0 | 1 | 2            | 3            | 4 | 5 | 6 | 7 | G     | 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8            |

|              |   |   |   | 2            |              |   |   |   |   | G     | 2 | 1 | 1 | 2 | 3 | 4 | 5 | 6 | 6 | 7            |

| a            | 3 | 2 | 1 | 2            | 3            | 4 | 5 | 6 | 7 |       |   | 2 |   |   |   |   |   |   |   |              |

| n            | 4 | 3 | 2 | 2            | 3            | 4 | 5 | 5 | 6 | Τ     | 4 | 3 | 2 | 2 | 1 | 2 | 3 | 4 | 5 | 6            |

| i            | 5 | 4 | 3 | 3            | 3            | 4 | 4 | 5 | 6 |       |   | 4 |   |   |   |   |   |   |   |              |

| n            | 6 | 5 | 4 | 4            | 4            | 4 | 5 | 4 | 5 | G     | 6 | 5 | 4 | 4 | 3 | 3 | 3 | 3 | 3 | 4            |

| g            | 7 | 6 | 5 | 5            | 5            | 5 | 5 | 5 | 4 | A     | 7 | 6 | 5 | 5 | 4 | 4 | 4 | 3 | 4 | 4            |

Fig. 2.10. Examples of the calculation of the edit distance using the method of dynamic programming for textual string matching in the matrix  $M_1$  and DNA sequences in  $M_2$ .

function that computes the edit distance between two character strings  $x_{1...i}$  and  $y_{1...j}$  can be defined by

$$c_{i,j} = \min(c_{i-1,j-1} + d(x_i, y_j), c_{i-1,j} + 1, c_{i,j-1} + 1)$$

with  $c_{0,0} = 0$  (2.3)

where  $d(x_i, y_j) = 0$  if  $x_i = y_j$  else 1, according to [Nav02]. A parameterization of (2.3) is possible using weighted costs for the penalty of a substitution, an insertion and a deletion [Blü00a]. However, due to the symmetry of the problem, the insertion in one string is equivalent to the deletion in the other.

The path highlighted in the two examples of Fig. 2.10 that apply (2.3) is not exclusive since alternative solutions also result in a maximal global edit distance of four for both  $M_1$  and  $M_2$ . Depending on the implementation, the complexity of the method varies from O(n) time using O(m) processors up to O(mn) with one single processor. One advantage of the method resides in the absence of any preprocessing step. However, pattern matching based on dynamic programming has the major problem of being inapplicable for searching small or non-aligned patterns in large texts. Even though a string might be entirely included in another one, the length difference is directly estimated as a mismatch. Therefore this method is more appropriate for searching keys or items in a list of formatted words than for querying wildly in a pool of textual unsorted information.

### 2.4 Hash Functions and Text Signatures

Hashing is used as a table search method in which the position of a key within the data structure is computed directly from the value of the key using a hash function. Once addressed, data linked to a key can be directly accessed providing a constant time O(1) lookup on average, overcoming the  $O(\log n)$  time complexity yield by a retrieval in binary search trees. From the practical point of view, hashing techniques always imply a compromise between time complexity and area consumption. Formally, the retrieval method applies a function h to find an entry key x assumed in our case to be character

string, defined as

$$h(x) = (x[0] \cdot B^{m-1} + x[1] \cdot B^{m-2} + \dots + x[m-1]) \mod W$$

(2.4)

where m is the length of the key, B a number that serves as a polynomial basis and W the width of the hash table. Usually, W is an arbitrarily large prime number, the goal of which is to obtain a fairly uniform distribution of h(x) over W for any x. The computation of h(x) which gives the position of the entry key x in the table with  $0 \le h(x) < W$  can be performed in O(1) time complexity [Nav02]. A well known example is the Karp-Rabin (KR) algorithm [Kar87] which uses hashing to seek a pattern within a text. Its average and best case running time is O(n), but the worst case performance is O(nm), where m and n stand for the length of the query Q and the text T respectively. In any hardware or software implementation however, as the table needs to be stored in a physical memory with a fixed size, W is limited and h never remains an injective application. For this reason, the use of this method leads to collisions or false drops which need to be resolved further on. Many ways are found in the literature to deal with collisions, as for example resolution using chained lists, double hashing, open addressing, or in some cases even collision ignoring when applicable. For a more detailed analysis of various searching algorithms suitable for string matching in general, we refer to the published work of Baeza-Yates et.al. [Bae99], Cormen et.al. [Cor01], Knuth [Knu97], Navarro et.al. [Nav01, Nav02], Sedgewick [Sed88], Witten et.al. [Wit99] and many more [Col98, Die94, Lom83].

Based on such hashing techniques, signature files are index structures which use a hash function mapping text features, e.g., n-grams, to a bit mask of W bits. The encoding is applicable to a query string Q or a text T from a collection, and consists in regrouping all the hash values h(x) that were extracted from Q or T within one single signature. Hence the resulting file is formed by the sequence of bit masks of all texts  $T_i$  plus an entry pointer  $e_i$  to this text. The typical search operation can be carried out by comparing signatures  $s_Q$  and  $s_T$  of Q and T bitwise. The Hamming distance d(Q,T) between the masking  $(s_Q \& s_T)$  and the query signature  $s_Q$  corresponds to the degree of matching of Q in T and can be estimated using simple logical operations through

$$d(Q,T) = \operatorname{bitcount} \{ (s_Q \& s_T) \oplus s_Q \}$$

(2.5)

where & and  $\oplus$  symbols correspond to the bitwise AND and XOR respectively. The AND operation masks the positions in  $s_T$  which must match the ones in  $s_Q$ . The XOR operation isolates the bits in  $s_T$  after the previous bit-masking where zeroes were found instead of ones. Using simple boolean arithmetics, we can simplify (2.5) to

$$d(Q,T) = \operatorname{bitcount}\left\{s_Q \& \overline{s_T}\right\} = \sum_{i=0}^{W-1} \overline{s_T[i]} \quad \forall \ s_Q[i] \neq 0$$

(2.6)

where  $\overline{s_T}$  represents the bitwise negated signature of the text T and  $s_T[i]$  the bit at the position i in this signature with  $0 \le i < W$ . Even though a thus calculated zero-distance

cannot ensure an exact matching due to the probability of collision, this method is very fast. For inverted files, if the risk of false drop is accepted within a given application, the necessary traversal verification [Bae99] can be avoided.

# 3 Sorting Techniques and Algorithms

As they both fundamentally imply comparing operations, it is safe to say that sorting and searching are closely related to each other. In [Knu97], Knuth provides an excellent reference of classical computer techniques for sorting as a very comprehensive and detailed survey. We would like to refer to this resource explicitly as Knuth's seminal work has been widely used to build this section. Also thoroughly reviewed by Sedgewick [Sed88], Martin [Mar71] and Cormen et.al. [Cor01], sorting algorithms represent an important part of our work, therefore the most significant ones are reviewed in this section.

### 3.1 Sequential Sorting

Here we consider that records consist in a body of data plus a key which is used to control the sorting. Per definition, an algorithm for sorting is a procedure that rearranges a file of records so that these are in ascending or in descending order. Before presenting fast networks for sorting in the next section, we review the elementary procedures that will help understand the basic concepts and optimize other algorithms later within our work.

#### 3.1.1 Insertion Sort

Probably the most obvious method for ordering playing cards, insertion sort consists in a repetitive operation of inserting a record from an unsorted list at its final relative place in a new sorted list until no record is left in the old list. This algorithm constructs the final result sequentially, one element at a time.

**Algorithm I** (Insertion Sort). Records  $R_1$  to  $R_N$  are rearranged in place such that their keys  $K_1$  to  $K_N$  will be in order  $(K_1 \leq \cdots \leq K_N)$  after sorting is complete. Considering virtually that  $R_0 = -\infty$  and  $R_{N+1} = \infty$ , let i be the index pointing to the record currently processed.

- **I1.** [Loop on i.] Perform steps I2 through I5 for i = 2, ..., N.

- **12.** [Set up R.] Set temporary record  $R \leftarrow R_i$ .

- **I3.** [Find position j.] Select j such that  $K_j \leq K_i < K_{j+1}$ .

- **I4.** [Move records.] Shift one place  $\{R_{j+2}\cdots R_i\}\leftarrow \{R_{j+1}\cdots R_{i-1}\}$ .

- **I5.** [Insert record.] Set  $R_{j+1} \leftarrow R$ .

It should be noticed that algorithm I includes one macro-step I3 which consists in finding the position of the record to be inserted in the sorted list. Depending on how it is implemented, this operation may require many comparisons to find the position in the sorted list. Regarding step I4, it may be possible in hardware to move a part of the records in O(1) time using a dedicated shift register, whereas in software all the records which have to be displaced must be taken one by one.

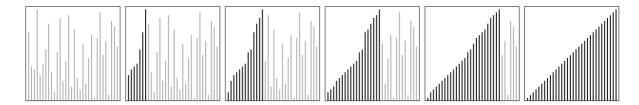

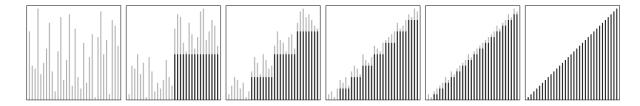

Fig. 2.11. Insertion sort algorithm: Items are selected successively from the left to the right and inserted at their relative final position in the sorted list situated left of the selection.

Fig. 2.11 shows the progression of the insertion sort algorithm at different intervals of time. In the worst case, each step i requires a shift of i-1 elements for the insertion so that the runtime complexity remains  $O(N^2)$ . However, with a given area and a high degree of parallelism, this algorithm could run in O(N) time, e.g., if we are able to find the position of j, i.e., step I3, in O(1) using O(N) comparators.

#### 3.1.2 Selection Sort

The selection method requires all of the input items to be present before sorting can proceed and generates the final output one by one in a sequence. There exist many versions of the selection sort algorithm [Knu97], however we propose one which is based on the selection of the smallest element of a list first, then the second smallest, etc., as illustrated in algorithm S.

**Algorithm S** (Selection Sort). Records  $R_1$  to  $R_N$  are rearranged in place such that their keys  $K_1$  to  $K_N$  will be in order  $(K_1 \leq \cdots \leq K_N)$  after sorting is complete. Let i be the index pointing to the last record currently in place.

- **S1.** [Loop on i.] Perform steps S2 and S3 for i = 1, ..., N-1.

- **S2.** [Find minimum.] Select  $R_m$  so that  $K_m = \min(K_i, \ldots, K_N)$ .

- **S3.** [Exchange.] Interchange  $R_i \leftrightarrow R_m$ .

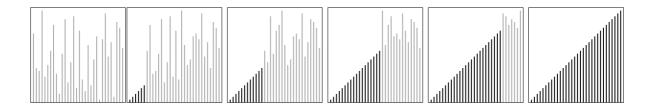

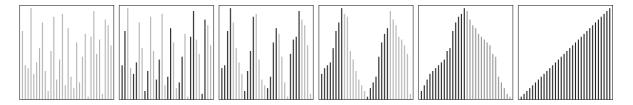

The selection sort algorithm is practically the opposite of Algorithm I whereas it requires fewer data movements than the insertion sort but more comparisons. It has the same runtime for any set of N elements independently of their values or order, since finding the minimum or the maximum element of a list of N elements requires N-1 comparisons. Its final runtime complexity remains  $O(N^2)$ . Fig. 2.12 shows this procedure in time, from the leftmost to the rightmost snapshot, where the items are placed from the smallest to the largest.

**Fig. 2.12.** Selection sort algorithm: Items are selected, from the smallest one to the biggest one, and placed progressively at their final position until no item remains unselected.

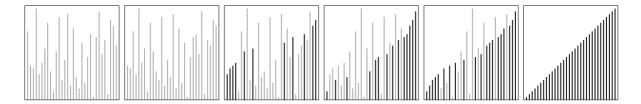

#### 3.1.3 Exchange Sort

Arranging a file of N records  $R_1$  to  $R_N$  according to the bubble sort method consists in repeating a sequence of exchange operations that interchange adjacent records  $R_i$  and  $R_{i+1}$  if their keys  $K_i$  and  $K_{i+1}$  are out of order, with  $1 \leq i < N$ . In this sequence, records with large keys move up and the record with the largest key will become  $R_N$ . Repetitions of the process will get appropriate records into positions  $R_{N-1}, R_{N-2}, \ldots$ , so that all records will ultimately be sorted [Knu97]. After each sequence, all records above and including the last one to be exchanged are in their final position and do not need to be examined on subsequent passes.