Abstract

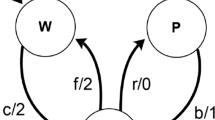

This article presents a test generation method for sequential circuits based on their synthesis specifications as finite state machines (FSM) and provides comparison with random test generation. The finite state machines are represented by their state transition graph (STG). The test generation method is performed in two phases. The first phase is functional. It generates a test sequence which is one of the shortest input sequences going through all the transitions of the state transition graph machine. This sequence provides a high fault coverage of stuck-at faults on the synthesized circuit compared to a randomly generated test sequence. This fault coverage is very close to the ones of other sequences derived by fault-oriented test generation approaches [9], [10], although these latter sequences are much longer.

The trend of the fault coverage curve for different test sequences including progressively the transitions of the test sequence defined in the first phase is similar to the one of the fault coverage curve of a random sequence but for same lengths the first curve gives larger fault coverage. Both curves grow rapidly until a given ratio of faults is detected then continue to grow very slowly exhibiting low efficiency.

The second phase of the test generation method is fault-oriented. It uses a fault simulation based approach in order to compute the test sequence for the remaining faults not detected by the first phase. At the end of this phase the test sequence for all the nonredundant faults is derived and, the combinationally redundant faults and the sequentially redundant faults are distinguished.

Similar content being viewed by others

References

D. Brahme and J.A. Abraham, “Functional testing of microprocessors”IEEE Trans. on Comp., vol. C-33, pp. 475–485, June 1984.

C. Robach and G. Saucier, “Dynamic testing of control units,”IEEE Trans. on Comp. vol. C-27, pp. 617–623, July 1978.

C. Jay, “Experience in functional-level test generation and fault coverage in a silicon compiler” Workshop on Defect and Fault Tolerance in VLSI Systems, New York: Plenum Press, pp. 135–148, 1989.

M. Karam, “Test generation based on functional modeling,” Ph.D. Dissertation, Institut National Polytechnique de Grenoble, 1991.

P. Kovijanic, “A new look at test generation and verification,”Proc. 14th Design Auto. Conf., pp. 58–63, June 1977.

K. Sabnani and A. Dahbura, “A new technique for generating protocol tests”9th Data Communications Symp., IEEE Comp. Soc. Press, pp. 36–43, September 1985.

M. Uyar and A. Dahbura, “Optimal test sequence generation for protocols: The Chinese postman algorithm applied to Q.931,”Proc. IEEE Global Telecommunications Conference, 1986.

A. Aho, A. Dahbura, D. Lee, and M. Uyar, “An optimization technique for protocol conformance test generation based on UIO sequences and rural Chinese postman tour,”Protocol Specification, Testing, and Verification VIII, New York: Elsevier Science Publishers B.V., pp. 75–86, June 1988.

K.-T. Cheng and J.-Y. Jou, “Functional test generation for finite state machines,”Proc. International Test Conference, pp. 162–168, Washington, D.C., 1990.

I. Pomeranz and S. Reddy, “On achieving a complete fault coverage for sequential machines using the transition fault model,”Proc. Design Auto. Conf., pp. 341–346, California, June 1991.

A. Gibbons,Algorithmic graph theory, Cambridge, MA: Cambridge University Press, 1985.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Karam, M., Saucier, G. Functional versus random test generation for sequential circuits. J Electron Test 4, 33–41 (1993). https://doi.org/10.1007/BF00971938

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF00971938