# Towards Intelligent Data Acquisition Systems with Embedded Deep Learning on MPSoC

Zur Erlangung des akademischen Grades eines DOKTOR-INGENIEURS (Dr.-Ing.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) angenommene

Dissertation

von

Weijia Wang

Tag der Mündlichen Prüfung:21.12.2020Hauptreferent:Prof. Dr. Marc WeberKorreferent:Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

21.12.2021 21.12.2021

I hereby declare that the work presented in this thesis is entirely my own and that I did not use any source or auxiliary means other than these referenced. This thesis was carried out in accordance with the Rules for Safeguarding Good Scientific Practice at Karlsruhe Institute of Technology (KIT).

Karlsruhe, June 24, 2021

### Abstract

Large-scale scientific experiments rely on dedicated high-performance data-acquisition systems to sample, readout, analyse, and store experimental data. However, with the rapid development in detector technology in various fields, the number of channels and the data rate are increasing. For trigger and control tasks data acquisition systems needs to satisfy real-time constraints, enable short-time latency and provide the possibility to integrate intelligent data processing. During recent years machine learning approaches have been used successfully in many applications. This dissertation will study how machine learning techniques can be integrated already in the data acquisition of large-scale experiments. A universal data acquisition platform for multiple data channels has been developed. Different machine learning implementation methods and application have been realized using this system.

On the hardware side, recent FPGAs do not only provide high-performance parallel logic but more and more additional features, like ultra-fast transceivers and embedded ARM processors. TSMC's 16nm FinFET Plus (16FF+) 3D transistor technology enables Xilinx in the Zynq UltraScale+ FPGA devices to increase the performance/watt ratio by 2 to 5 times compared to their previous generation. The selected main processor ZU11EG owns 32 GTH transceivers where each one could operate up to 16.3 Gb/s and 16 GTY transceivers where each of them could operate up to 32.75 Gb/s. These transceivers are routed to x16 lanes Gen 3/4 PCIe, 12 lanes full-duplex FireFly electrical/optical data link and VITA 57.4 FMC+ connector.

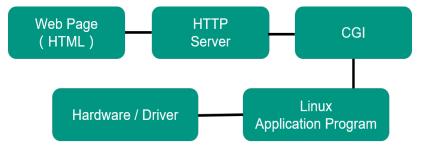

The new Zynq UltraScale+ device provides at least three major advantages for advanced data acquisition systems: First, the 16nm FinFET+ programmable logic (PL) provides high-speed readout capabilities by high-speed transceivers; second, built-in quad-core 64-bit ARM Cortex-A53 processor enable host embedded Linux system. Thus, webservers, slow control and monitoring application could be realized in a embedded processor environment; third, the Zynq Multiprocessor System-on-Chip technology connects programmable logic and microprocessors. In this thesis, the benefits of such architectures for the integration of machine learning algorithms in data acquisition systems and control application are demonstrated.

On the algorithm side, there have been many achievements in the field of machine learning over the last decades. Existing machine learning algorithms split into several categories depending on how the learning phase is organized: Supervised Learning, Unsupervised Learning, Semi-Supervised Learning and Reinforcement Learning. Most commonly used in scientific applications are supervised learning and reinforcement learning.

Supervised learning learns from the labelled input and output, and generates a function that could predict the future different input to the appropriate output. A common application instance is a classification. They have a wide difference in basic math theory, training, inference, and their implementation.

One of the natural solutions is Application Specific Integrated Circuit (ASIC) Artificial Intelligence (AI) chips. A typical example is the Google Tensor Processing Unit (TPU), it could cover the training and inference for both supervised learning and reinforcement learning. One of the major issues is that such chip could not provide high data transferring bandwidth

other than high compute power. As a comparison, the Xilinx UltraScale+ FPGA could also provide raw compute power and efficiency for all different data types down to a single bit.

From a deployment point of view, the training part of supervised learning is typically performed by CPU/GPU/TPU on a fixed dataset. For reinforcement learning, the training phase is more complex. The algorithm needs to periodically interact with the controlled system and execute a Markov Decision Process (MDP). There is no static training dataset, but it is obtained in real-time. The time slot between each step depends on the dynamics of the controlled system. The inference is also bound to this sampling time because the algorithm needs to interact with the environment and decide the appropriate action for a response, then a higher demand on time is proposed.

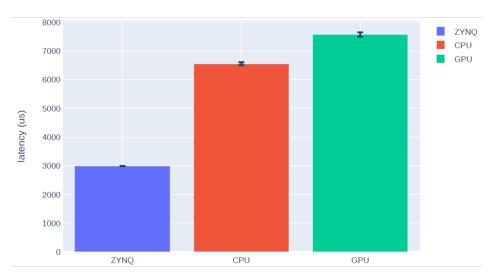

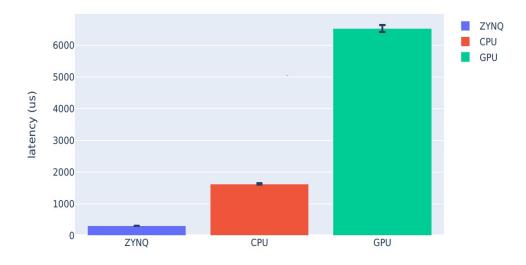

This thesis gives solutions for both training and inference of reinforcement learning. At first, the requirements are analyzed, then the algorithm is deduced from scratch, and training on the PS part of Zynq device is implemented, meanwhile the inference at FPGA side is proposed which is similar solution compared with supervised learning. The results for Policy Gradient show a lot of improvement over a CPU/GPU-based machine learning framework. The Deep Deterministic Policy Gradient also has improvement regarding both training latency and stability. This implementation method provides a low-latency approach for reinforcement learning on-field training process.

## Zusammenfassung

Große wissenschaftliche Experimente basieren auf dedizierten Hochleistungsdatenerfassungssystemen, um experimentelle Daten auszuprobieren, auszulesen, zu analysieren und zu speichern. Mit der rasanten Entwicklung der Detektortechnik in verschiedenen Bereichen steigen jedoch die Anzahl der Kanäle und die Datenrate. Für Trigger- und Steuerungsaufgaben müssen Datenerfassungssysteme Echtzeit-Einschränkungen erfüllen, Kurzzeitlatenz ermöglichen und die Möglichkeit bieten, intelligente Datenverarbeitung zu integrieren. In den letzten Jahren wurden Machine Learning-Ansätze in vielen Anwendungen erfolgreich eingesetzt. In dieser Dissertation wird untersucht, wie maschinelle Lerntechniken bereits in die Datenerfassungsplattform für mehrere Datenkanäle entwickelt. Mit diesem System wurden verschiedene Implementierungsmethoden und Anwendungen für maschinelles Lernen realisiert.

Auf der Hardwareseite bieten die jüngsten FPGAs nicht nur eine leistungsstarke parallele Logik, sondern immer mehr zusätzliche Funktionen wie ultraschnelle Transceiver und eingebettete ARM-Prozessoren. Die 16nm FinFET Plus (16FF+) 3D-Transistor-Technologie von TSMC ermöglicht es Xilinx in den Zynq UltraScale+ FPGA-Geräten, das Leistungs-Watt-Verhältnis im Vergleich zur vorherigen Generation um das 2- bis 5-fache zu erhöhen. Der ausgewählte Hauptprozessor ZU11EG besitzt 32 GTH-Transceiver, bei denen jeder von ihnen bis zu 16,3 GB/s und 16 GTY-Transceiver betreiben kann, bei denen jeder von ihnen bis zu 32,75 USD Gb/s betreiben kann. Diese Transceiver werden an x16-Lanes Gen 3/4- PCIe, 12-und -duplex-Vollduplex-Verbindung FireFly und VITA 57.4 FMC+-Anschluss geroutet.

Das neue Zynq UltraScale+ Gerät bietet mindestens drei wesentliche Vorteile für fortschrittliche Datenerfassungssysteme: Erstens bietet die 16nm FinFET+ programmierbare Logik (PL) Hochgeschwindigkeits-Auslesefunktionen durch Hochgeschwindigkeits-Transceiver; zweitens, integrierter Quad-Core 64-Bit ARM Cortex-A53 Prozessor ermöglichen Host Embedded Linux System. So konnten Webserver, langsame Steuerungs- und Überwachungsanwendungen in einer eingebetteten Prozessorumgebung realisiert werden. drittens verbindet die Zynq Multiprozessor System-on-Chip-Technologie programmierbare Logik und Mikroprozessoren. In dieser These werden die Vorteile solcher Architekturen für die Integration von Machine Learning-Algorithmen in Datenerfassungssysteme und Steuerungsanwendungen demonstriert.

Auf der Algorithmusseite gab es in den letzten Jahrzehnten viele Erfolge auf dem Gebiet des maschinellen Lernens. Bestehende Machine Learning-Algorithmen gliederten sich in mehrere Kategorien, je nachdem, wie die Lernphase organisiert ist: Supervised Learning, Unsupervised Learning, Semi-Supervised Learning und Reinforcement Learning. Am häufigsten in wissenschaftlichen Anwendungen verwendet werden, sind überwachtes Lernen und Verstärkung lernen.

Überwachtes Lernen lernt von der beschrifteten Eingabe und Ausgabe und generiert eine Funktion, die die zukünftigen unterschiedlichen Eingaben für die entsprechende Ausgabe vorhersagen könnte. Eine gemeinsame Anwendungsinstanz ist eine Klassifizierung. Sie haben einen großen Unterschied in der grundlegenden mathematischen Theorie, Ausbildung, Rückschlüsse, und ihre Umsetzung.

Eine der natürlichen Lösung ist Application Specific Integrated Circuit (ASIC) Artificial Intelligence (AI)-Chips. Ein typisches Beispiel ist die Google Tensor Processing Unit (TPU), die die Ausbildung und Rückschlüsse sowohl für das überwachte Lernen als auch für das Verstärkungslernen abdecken könnte. Eines der Hauptprobleme ist, dass ein solcher Chip keine hohe Datenübertragungsbandbreite bieten konnte, außer hoher Rechenleistung. Zum Vergleich: Der Xilinx UltraScale+ FPGA könnte auch eine rohe Rechenleistung und Effizienz für alle Datentypen bis auf ein einziges Bit bieten.

Aus Sicht der Bereitstellung wird der Trainingsteil des überwachten Lernens in der Regel von CPU/GPU/TPU für ein festes Dataset durchgeführt. Für das Verstärkungslernen ist die Trainingsphase komplexer. Der Algorithmus muss regelmäßig mit dem kontrollierten System interagieren und einen Markov Decision Process (MDP) ausführen. Es gibt kein statisches Trainings-Dataset, aber es wird in Echtzeit abgerufen. Das Zeitfenster zwischen den einzelnen Schritten hängt von der Dynamik des gesteuerten Systems ab. Die Schlussfolgerung ist auch an diese Samplingzeit gebunden, da der Algorithmus mit der Umgebung interagieren und die geeignete Aktion für eine Antwort entscheiden muss, dann wird eine höhere Zeitanforderung vorgeschlagen.

Diese These liefert Lösungen sowohl für die Ausbildung als auch für die Rückschlussung des Verstärkungslernens. Zuerst werden die Anforderungen analysiert, dann wird der Algorithmus von Grund auf neu abgeleitet, und die Ausbildung auf dem PS-Teil des Zynq-Geräts wird implementiert, während die Schlussfolgerung auf FPGA-Seite vorgeschlagen wird, die eine ähnliche Lösung im Vergleich zum überwachten Lernen ist. Die Ergebnisse für Richtliniengradient zeigen eine Menge Verbesserungen gegenüber einem CPU/GPU-basierten Machine Learning Framework. Der tiefer deterministischer Richtliniengradient hat auch Verbesserungen in Bezug auf Trainingslatenz und Stabilität. Diese Implementierungsmethode bietet einen Ansatz mit geringer Latenz für den Schulungsprozess für die Verstärkung des Lernens vor Ort.

## Acknowledgments

Upon the completion of this thesis, I am grateful to those who have offered me encouragement and support during the 4 years of my study and work. Firstly, the acknowledgement is given to Prof. Marc Weber, who offered me the opportunity to start the Ph.D. at IPE KIT, and gave me a lot of suggestions during Ph.D. working and thesis writing. I would like to give my heartfelt gratitude to my supervisor Dr. Michele Caselle. During the four years of study, he gave me incalculable valuable guidance, and helped me improve a lot in knowledge, engineering practice ability and working ability. Working with him and debugging hardware system is always a nice experience. I wish to show my gratitude to Dr. Andreas Kopmann, who gave me a lot of suggestion and help during all of my conference, paper and thesis writing. The quality of work has improved a lot under his help. I also like to give my appreciation to my colleagues: Timo Dritschler, Meghana Patil, Luis Eduardo Ardila Perez, Nick Karcher, Oliver Sander and many other IPE colleagues. I like the mutual help atmosphere here at IPE and working together for the same projects. I also thank my colleagues from IBPT and LAS: Tobias Boltz, Dr. Miram Brosi, Edmund Blomley, Andrea Santamaria Garcia. They gave me a lot of support during the Ph.D. stage. I am also greatly indebted to the professors and teachers at the Department of Electrical Engineering and Information Technology. I have learned a lot at KIT.

# Contents

| A  | ostrac | et                                     | iv   |

|----|--------|----------------------------------------|------|

| Zι | ısamr  | nenfassung                             | vi   |

| A  | cknow  | vledgments                             | viii |

| Co | onten  | ts                                     | 1    |

| 1  | Intr   | oduction                               | 4    |

|    | 1.1    | Advanced data acquisition system       | 5    |

|    | 1.2    | Machine Learning                       | 7    |

|    |        | 1.2.1 Supervised Learning              | 8    |

|    |        | 1.2.2 Reinforcement Learning           | 8    |

|    | 1.3    | Machine Learining applications         | 10   |

|    | 1.4    | Accelerating Machine Learning          | 10   |

|    | 1.5    | Hardware platform                      | 11   |

|    | 1.6    | Chapter arrangement                    | 13   |

| I  | Da     | ta Aquisition System Hardware Design   | 14   |

| 2  | Har    | dware design of the readout card       | 16   |

|    | 2.1    | FPGA resources allocation              | 19   |

|    | 2.2    | Clock distribution                     | 20   |

|    | 2.3    | PCI Express circuit design             | 21   |

|    | 2.4    | FireFly circuit design                 | 24   |

|    | 2.5    | DDR4 for programmable logic            | 29   |

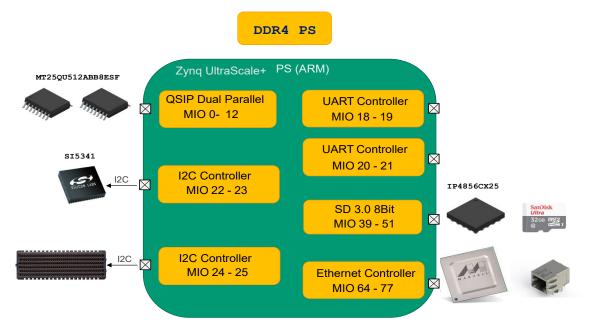

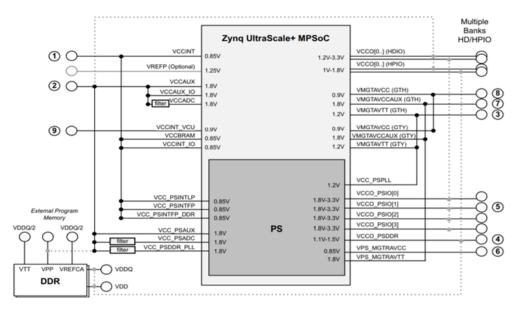

|    | 2.6    | PS peripherals design                  | 30   |

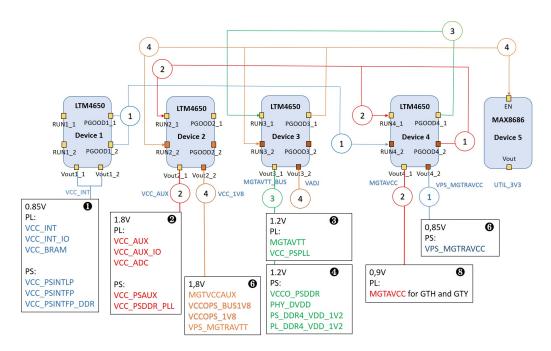

|    | 2.7    | Power supply design                    | 32   |

|    | 2.8    | Conclusion                             | 34   |

| 3  | Syst   | em-on-Chip on HighFlex2                | 35   |

|    | 3.1    | Next generation DAQ system integration | 35   |

|    | 3.2    | Hardware design of SoC                 | 36   |

|    | 3.3    | Yocto Project                          | 38   |

|    | 3.4    | EPICS                                  | 38   |

|    |        | 3.4.1 EPICS on hardware                | 38   |

|    |        | 3.4.2 EPICS control on HighFlex2       | 39   |

|    | 3.5    | Performance comparison                 | 41   |

|    | 3.6<br>3.7                             | Webserver application                                        |    |  |  |  |  |  |  |  |  |

|----|----------------------------------------|--------------------------------------------------------------|----|--|--|--|--|--|--|--|--|

|    |                                        |                                                              |    |  |  |  |  |  |  |  |  |

| II | Ar                                     | tificial Intelligence on Hardware                            | 45 |  |  |  |  |  |  |  |  |

| 4  |                                        | hine Learning preliminaries                                  | 47 |  |  |  |  |  |  |  |  |

|    | 4.1                                    | Introduction on Supervised Learning                          | 47 |  |  |  |  |  |  |  |  |

|    | 4.2                                    | Development of Reinforcement Learning                        | 48 |  |  |  |  |  |  |  |  |

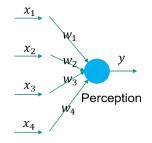

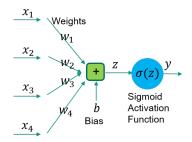

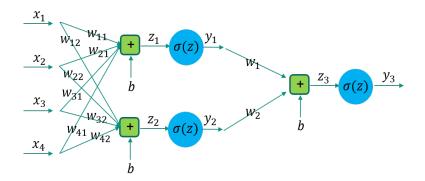

|    | 4.3                                    | Basic structure in Deep Learning                             |    |  |  |  |  |  |  |  |  |

|    |                                        | 4.3.1 Introduction of fully connected neural network         | 48 |  |  |  |  |  |  |  |  |

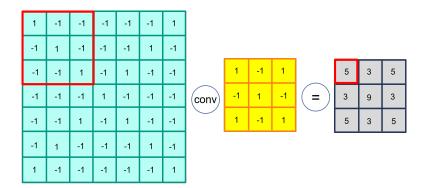

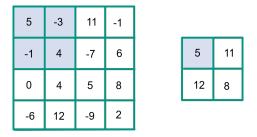

|    |                                        | 4.3.2 Introduction on convolutional neural network           | 49 |  |  |  |  |  |  |  |  |

|    | 4.4                                    | Implementation consideration of Supervised Learning          | 51 |  |  |  |  |  |  |  |  |

|    |                                        | 4.4.1 Implementation consideration of Reinforcement Learning |    |  |  |  |  |  |  |  |  |

|    |                                        | 4.4.2 CPU, GPU and FPGA acceleration                         | 53 |  |  |  |  |  |  |  |  |

| 5  | Supe                                   | ervised Learning on FPGA                                     | 55 |  |  |  |  |  |  |  |  |

|    | 5.1                                    | Optimazation methods targetting to FPGA                      | 55 |  |  |  |  |  |  |  |  |

|    |                                        | 5.1.1 Xilinx DPU configuration options                       | 56 |  |  |  |  |  |  |  |  |

|    | 5.2                                    | Demostration result                                          | 57 |  |  |  |  |  |  |  |  |

|    | 5.3                                    | Conclusion                                                   | 58 |  |  |  |  |  |  |  |  |

| 6  | Reinforcement Learning Introduction 60 |                                                              |    |  |  |  |  |  |  |  |  |

|    | 6.1                                    | Markov property                                              | 60 |  |  |  |  |  |  |  |  |

|    |                                        | 6.1.1 Return                                                 | 61 |  |  |  |  |  |  |  |  |

|    |                                        | 6.1.2 Value Function                                         | 62 |  |  |  |  |  |  |  |  |

|    |                                        | 6.1.3 Markov Decision Process                                | 62 |  |  |  |  |  |  |  |  |

|    |                                        | 6.1.4 Policies                                               | 63 |  |  |  |  |  |  |  |  |

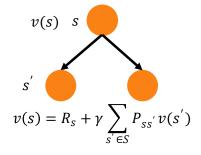

|    | 6.2                                    | State-Value Function                                         | 63 |  |  |  |  |  |  |  |  |

|    | 6.3                                    | Action-Value Function                                        | 63 |  |  |  |  |  |  |  |  |

|    | 6.4                                    | Temporal-Difference Prediction                               | 64 |  |  |  |  |  |  |  |  |

|    | 6.5                                    | Model-Free Control                                           | 64 |  |  |  |  |  |  |  |  |

|    |                                        | 6.5.1 $\epsilon$ -Greedy Exploration                         | 65 |  |  |  |  |  |  |  |  |

|    |                                        | 6.5.2 Q-learning: Off-Policy Temporal-Difference Control     | 65 |  |  |  |  |  |  |  |  |

|    | 6.6                                    | Function Approximation                                       | 65 |  |  |  |  |  |  |  |  |

|    | 6.7                                    | Deep Q-Learning                                              | 66 |  |  |  |  |  |  |  |  |

|    | 6.8                                    | Policy Gradient                                              | 67 |  |  |  |  |  |  |  |  |

|    | 6.9                                    | Monte-Carlo Policy Gradient (REINFORCE)                      | 69 |  |  |  |  |  |  |  |  |

|    | 6.10                                   | Conclusion                                                   | 70 |  |  |  |  |  |  |  |  |

| 7  | Polic                                  | y Gradient on embedded processor                             | 71 |  |  |  |  |  |  |  |  |

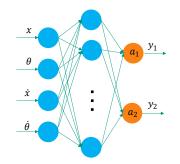

|    | 7.1                                    | Policy network                                               | 72 |  |  |  |  |  |  |  |  |

|    | 7.2                                    | One specific episode                                         | 73 |  |  |  |  |  |  |  |  |

|    |                                        | 7.2.1 Loss function of Policy Gradient                       | 74 |  |  |  |  |  |  |  |  |

|    |                                        | 7.2.2 Reward function of Policy Gradient                     | 74 |  |  |  |  |  |  |  |  |

|    |                                        | 7.2.3 Backpropagation for Policy Gradient                    | 76 |  |  |  |  |  |  |  |  |

|    | 7.3                                    | Policy Gradient training hardware design                     | 79 |  |  |  |  |  |  |  |  |

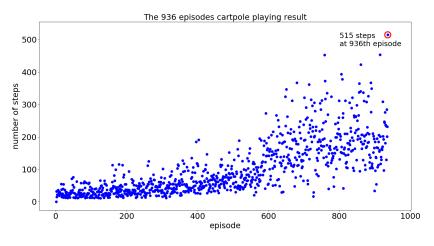

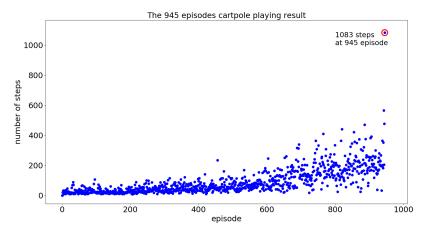

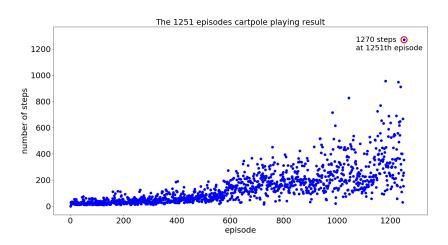

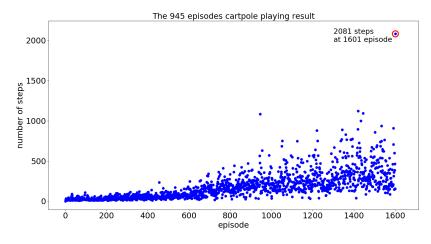

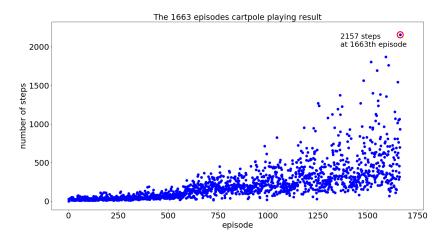

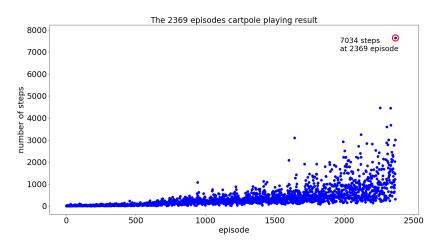

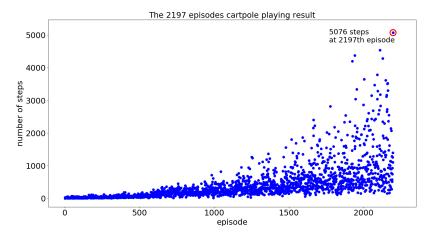

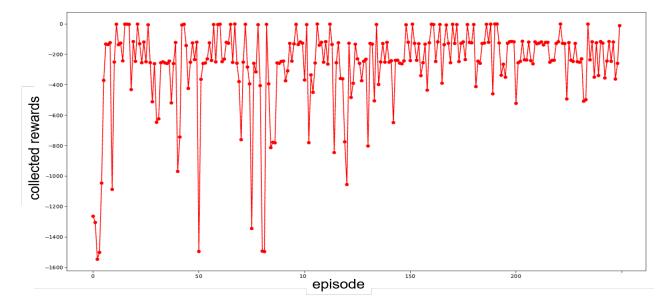

|    | 7.4                                    | Policy Gradient training curve                               | 80 |  |  |  |  |  |  |  |  |

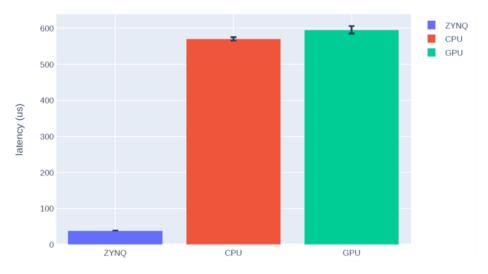

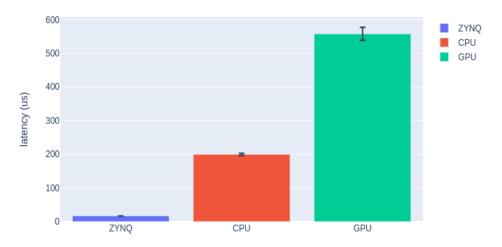

|    | 7.5                                    | Policy Gradient training performance                         | 84 |  |  |  |  |  |  |  |  |

|     | 7.6    | Conclusion                           | 87  |

|-----|--------|--------------------------------------|-----|

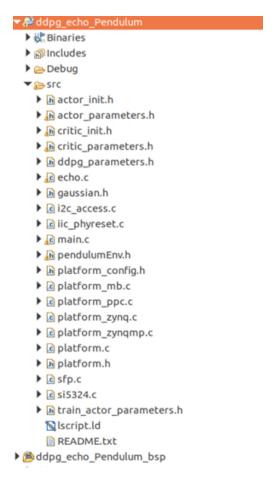

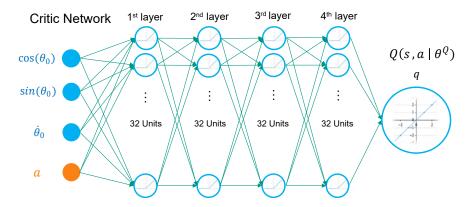

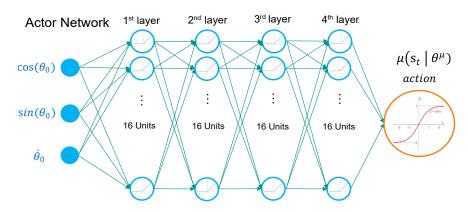

| 8   | DDP    | G on embedded processor              | 88  |

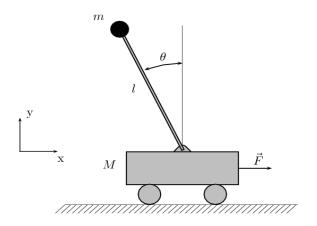

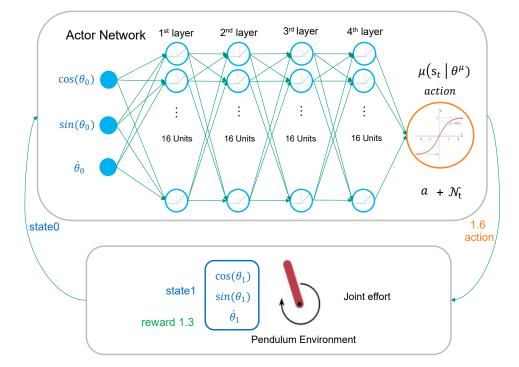

|     | 8.1    | Pendulum control                     | 89  |

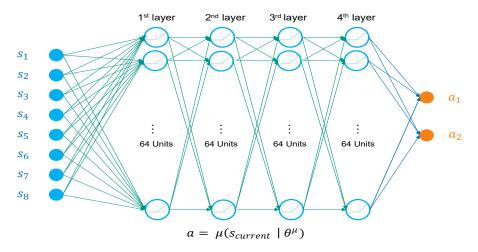

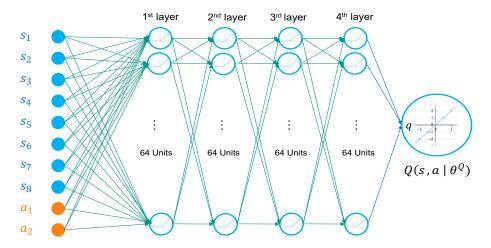

|     | 8.2    | Build DDPG networks                  | 89  |

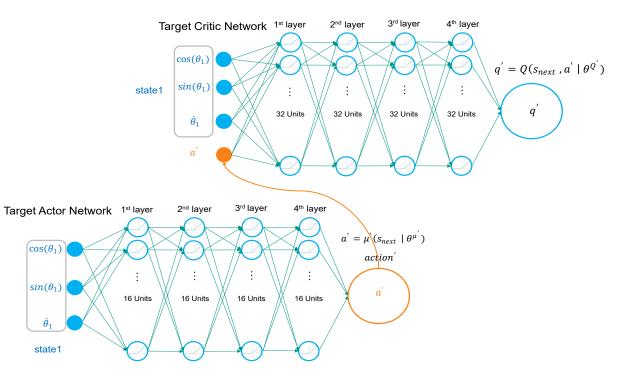

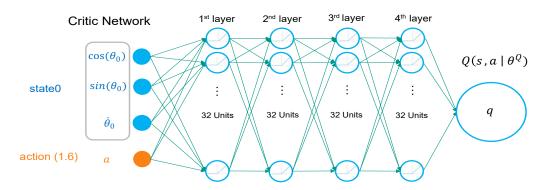

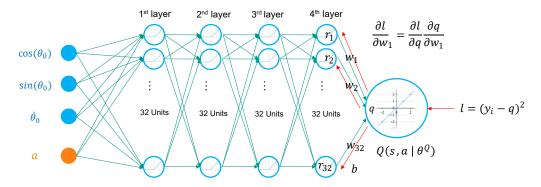

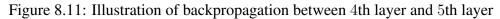

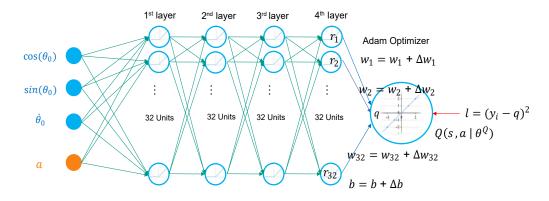

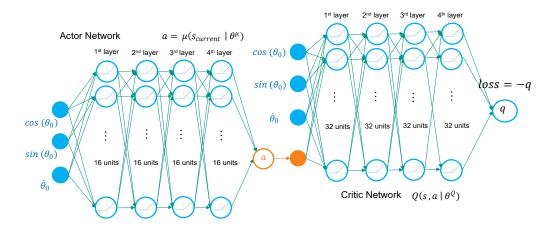

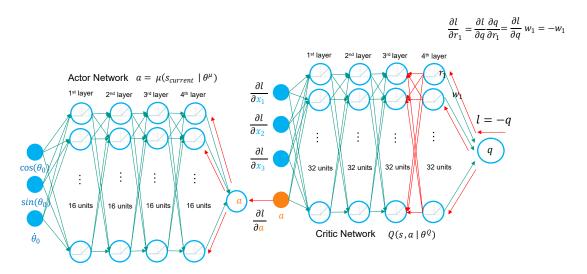

|     |        | 8.2.1 Critic network                 | 89  |

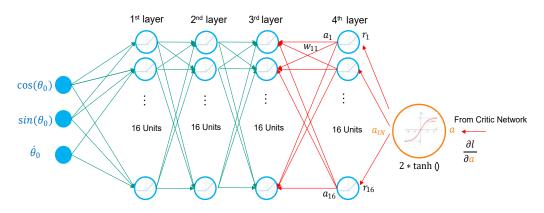

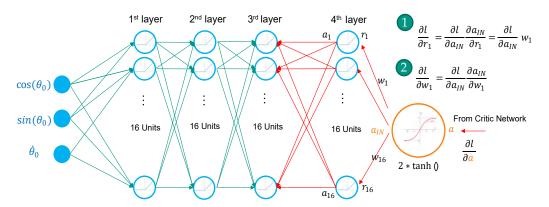

|     |        | 8.2.2 Actor network                  | 91  |

|     |        | 8.2.3 Memory buffer                  | 92  |

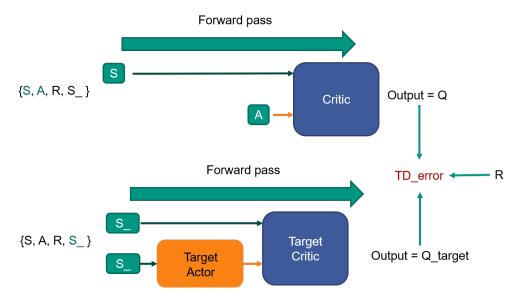

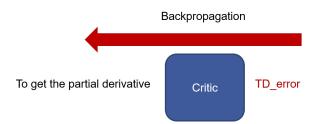

|     | 8.3    | Train critic network                 | 93  |

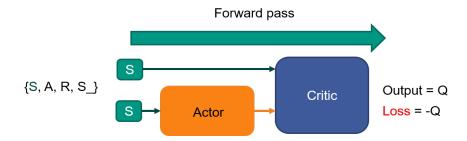

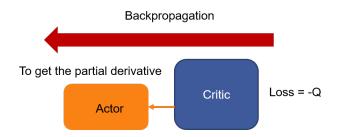

|     | 8.4    | Train actor network                  | 104 |

|     | 8.5    | Soft-replacement for target networks | 107 |

|     | 8.6    | Pendulum solution description        |     |

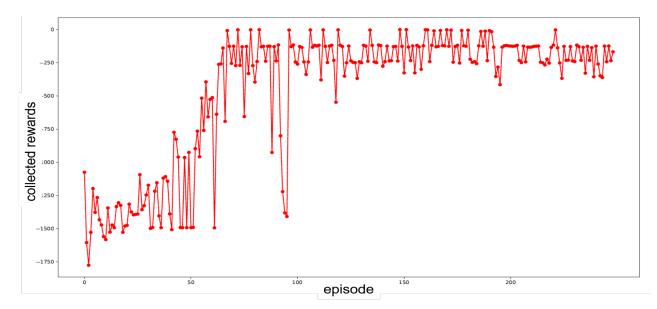

|     | 8.7    | Training curve of DDPG               | 109 |

|     | 8.8    | DDPG training performance            | 110 |

|     | 8.9    | Conclusion                           | 111 |

|     |        |                                      |     |

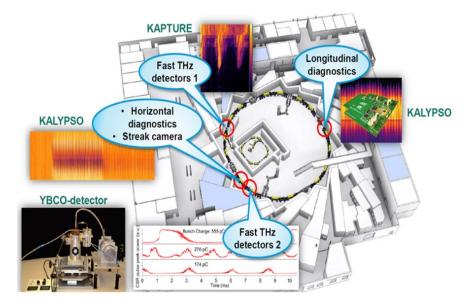

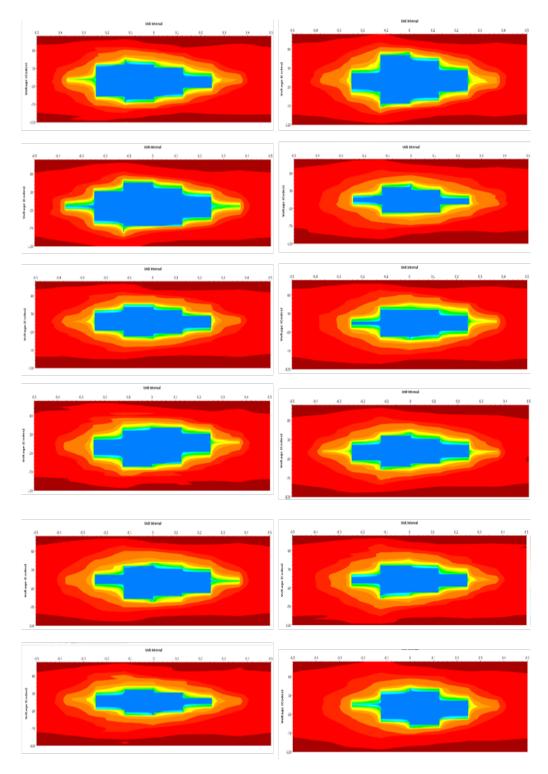

| 9   | Rein   | forcement Learning design at KARA    | 112 |

|     | 9.1    | Introduction                         |     |

|     | 9.2    | Karlsruhe Research Accelerator       | 112 |

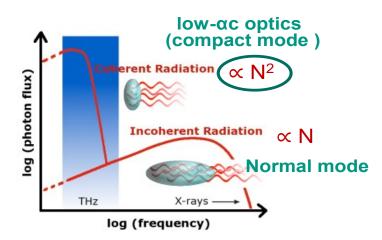

|     | 9.3    | Micro-bunching instability           |     |

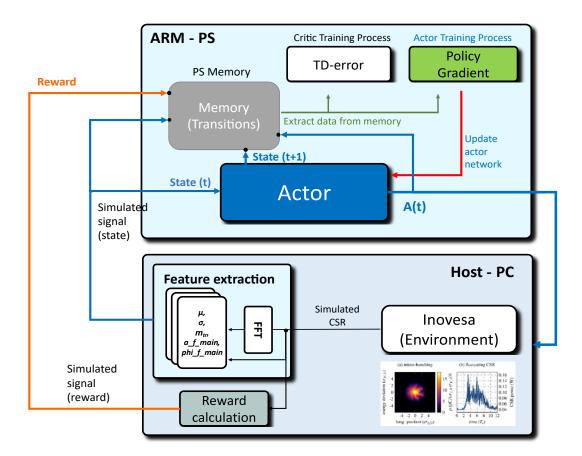

|     | 9.4    | Implementation of feedback loop      |     |

|     |        | 9.4.1 State signal                   | 116 |

|     |        | 9.4.2 Reward signal                  |     |

|     |        | 9.4.3 Action signal                  | 118 |

|     |        | 9.4.4 Algorithm choosen              |     |

|     | 9.5    | Hardware feedback loop               | 119 |

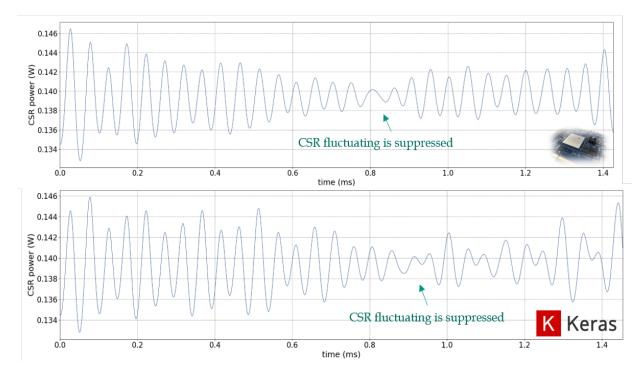

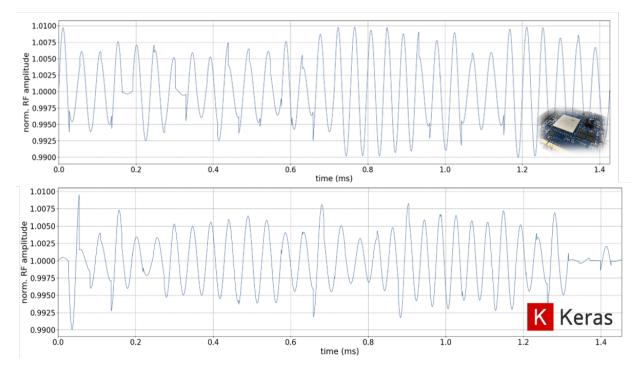

|     | 9.6    | Simulation result of training        | 120 |

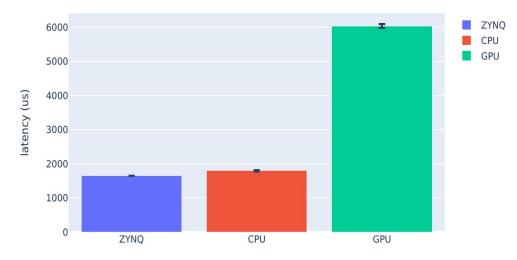

|     | 9.7    | Hardware training performance        |     |

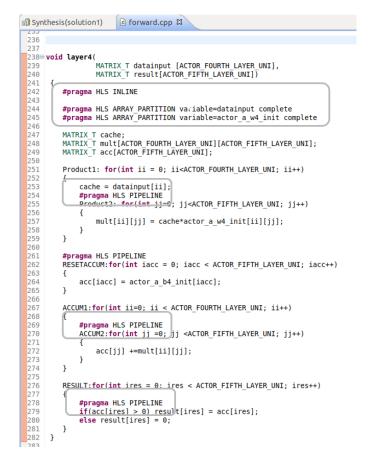

|     | 9.8    | DDPG inference at PL                 | 123 |

|     | 9.9    | Conclusion                           | 126 |

| 4.0 | a      |                                      |     |

| 10  | Cone   | clusion                              | 127 |

| Bil | bliogr | aphy                                 | 129 |

| Ар  | pendi  | ix A                                 | 141 |

| An  | pendi  | ix B                                 | 149 |

| -   | -      |                                      |     |

| -   | pendi  |                                      | 151 |

| Ар  | pend   | ix D                                 | 154 |

| Ар  | pendi  | ix E                                 | 158 |

| Ар  | pendi  | ix F                                 | 161 |

| Ар  | pendi  | ix G                                 | 164 |

## Chapter 1

### Introduction

With the success of deep learning algorithms and the sharply increasing number of applications, the competition on the ideal processing architectures has been re-opened again. For many years, the x86 architecture[1] was the de-facto standard. Other architectures have been presented several times but have not been considered. The effort and cost to migrate existing code was considered too high. Especially the validation of approved implementations made researchers stick to architectures and their corresponding programming languages of the last millennium. Artificial intelligence seems to be a game-changer now which provides an novel processing method and more clearly, the novel algorithms. Meanwhile, dedicated AI processors are proposed and integrated nearly everywhere: from mobile embedded processors to FPGAs[2] and GPUs[3].

In parallel to the spread on artificial intelligence in science, industry and society, the ARM platform[4] has reached a performance level that can compete with the traditional x86 CPU architecture. ARM Holdings develops the architecture and licenses it to other companies. ARM processors have been used in Apples mobile phones and tablets for years and increased drastically in performance. From next year on, ARM architectures will also be used in Apple computers. As a proof, in year 2020, the Fujitsu A64FX, an Armv8.2-A+SVE based architecture is used as supercomputer architecture and shows a relatively low execution time and high performance compared with Marvell (Cavium) ThunderX2 processor and Intel Xeon Skylake processor in [5].

Today's power consumption demands alternatives to the x86 architecture. The energy consumption of computing centres worldwide in the year 2017 has reached 350 billions of kWh per year [6]. The ARM and FPGA both show the potential of low power consumption but the same performance by comparison with CPU and GPU. The ARM cluster is more efficient for a large dataset than GPU [7]. [8] illustrate that FPGAs overperform GPUs in energy efficiency measured in Multiply-accumulate operation.

Dedicated AI-based algorithms, accelerator units like ARM processors and FPGAs are able to reduce the aforementioned demand by at least an order of magnitude. This thesis will investigate the impact of these probably disruptive technologies on Data Acquisition (DAQ) Systems. A promising platform for DAQ applications is enabled by recent System on Chips (SoCs), where the programmable logic combines with embedded ARM processors. They seem to be ideal to evaluate the architectures for AI-enabled applications in science and evaluate the estimated performance increase. The thesis will demonstrate how to implement different AI application on DAQ, how to allocate the AI tasks on different computing architectures within one SoC, and the results will be illustrated.

#### **1.1** Advanced data acquisition system

The quality of data determines the quality of scientific results and thus the success of an experiment. Data acquisition (DAQ) systems are essential to realizing high-quality results. DAQ system span a wide bridge of technologies form front-end electronics to data processing and archival. The term "data acquisition" refers to many measurement applications, all of which require some form of characterization, monitoring, or control. Regardless of the specific application, the purpose of general data acquisition systems is to measure physical parameters or different kinds of signal (for example, optical, mechanical, thermal, electrical, magnetic, chemical, etc.), or to use actuators generate specific actions based on the data received. Two primary missions of the DAQ systems are *data transmission* and *data processing*. The competence of *data transmission* includes the DAQ system can receive the data and handle the data (e.g. high speed and high bandwidth data). The *data processing* means the DAQ systems are:

- 1) To support high data throughput acquisition and enable data processing with low-latencies;

- 2) To provide the flexibility to adopt to changing experimental phases and to cover the dynamical development process during the construction of large-scale experiments;

- 3) To realize complex data processing algorithms to make DAQ systems intelligent.

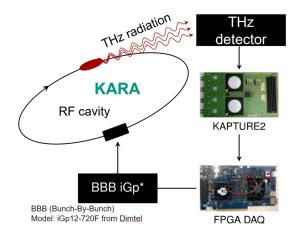

These three challenges will then be discussed in the following and solutions will be presented. First, the large scale physical experiment detectors have ever-increasing time, spatial, and energy resolution, and produce the data volume that previous generation sensors and DAQ system could not match. This requires that the DAQ systems in used need to support high-throughput data in the real-time range from front-end electronics to FPGAs, and also should include or connect to post-processing components (e.g. CPU/GPU clusters). The DAQ system could be configured as a transfer station, or process the data as an end-point. This requires the DAQ system to be configured to the different topology. Some physics experiment need feedback within a short time frame, for example, the beam control system at the Karlsruhe Research Accelerator (KARA) [9, 10, 11]. Thus the DAQ needs to react to the incoming data with low-latency shorter than the sampling time.

• Which devices are able to provide high throughput and low latencies? How to optimize the latency?

Normally, the answer will be the Field Programmable Gate Array (FPGA). The leading edge FPGA [12] could provide dozens of high bandwidth configurable transceivers for different high-speed data bus protocols. The execution model at FPGA is free for construction: parallel, pipeline, and data flow, which is different from the instruction model on CPU/GPU. This enables FPGA a possibility to build low latency data processing.

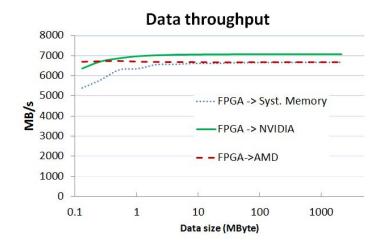

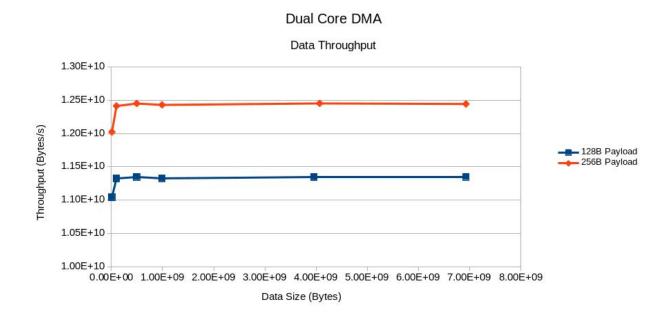

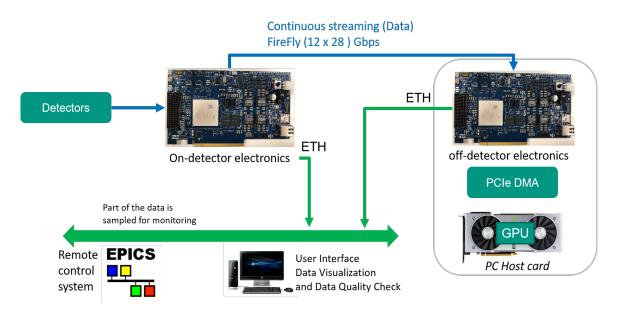

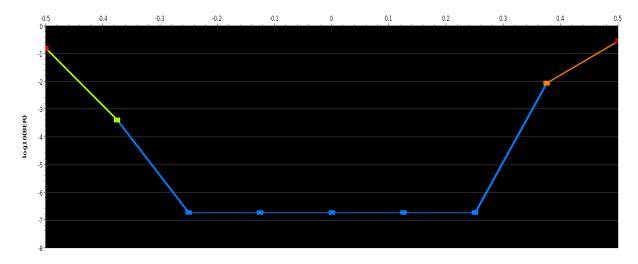

For the beam diagnostics systems, the FPGA-GPU heterogeneous [13, 14] system developed at the Institute for Data Processing and Electronics (IPE) plays an important role, providing a multi-Gigabyte per second real-time data transmission. In this heterogeneous system, one of the key components is a Direct Memory Access (DMA) engine [15], so-called "KIT DMA". That is fully compatible with Xilinx FPGA families 6 and 7, UltraScale+ device. The DMA is PCIe Generation 2, 3, 4 compatible. The Xilinx Virtex-7 based PCIe FPGA board ("Hi-Flex") used in [14, 15]. Fig (1.1) demonstrated the data throughput measurement by KIT DMA and it has a throughput larger than 6.5 GB/s in these 3 different transfer modes. This also provides very low latency transmission between FPGA and GPU. By "GPUDirect (NVIDIA)", the average transfer latency is lower than 2  $\mu$ s. By "DirectGMA" from AMD, the latency between Hi-Flex and AMD FirePro W9100 is lower than 1.3  $\mu$ s.

Figure 1.1: Data throughput measurements by KIT DMA to system memory, NVIDIA Tesla K40 and AMD FirePro W9100. [13]

Secondly, the demanded flexibility of DAQ systems means they could serve as a *general-purpose* tool, with dedicated processing units according to the problem to be solved. Because FPGA has the capacity for various hardware implementation structure, it could dynamically be reprogrammed with a data path that matches a dedicated processing/specific workload. Thus FPGA performs better for specific applications than general-purpose application processors like CPU/GPU. On the other hand, for general purpose applications, for example, a general calculation or task without strict time tolerance could be implemented on such an application processor. Some general embedded processors are also able to support a flexible control over front-end analogue-to-digital converter (ADC) or other peripherals. The state and data inside FPGA also demand a conveniently and flexibly control. Several questions could ask as follows for these additional functionalities:

- Which device could provide such flexibility and support embedded operating system?

- Is there another chip is required in the hardware design? Is there a solution to reduce the layout of the printed circuit board (PCB) if two chips on one board?

- Which tools are available to simplify the design effort and help to realize efficient communication between FPGA and it's embedded processor?

The third and also most demanding requirement is to realize complex tasks within DAQ systems. The first and second requirement serves as a prerequisite for the third requirement: complex task accomplishment. With the deepening of the research and the improvement of the front-end data volume, the new detector/accelerator may have different and more complex task than before. For some of these tasks, it is very hard to write the program or implement it on the hardware. For example, a problem like recognizing a multi-dimensional object in a cluttered scene. Such a problem could be the track finding through hundreds of hits at one event [16] at collider experiments to construct a program to recognize the track is difficult

because one doesn't know how physics experts recognize the track in their brain. Or even there was already one solution but a *sophisticated algorithm* is required. One simple method may perform well for one single event but the track form and style are changing frequently per event, a generalized approach for recognization is required. Besides the recognization problem, it is a similar situation for the control problem. At KIT's research synchrotron KARA, a microbunching control loop is under development [17]. A formation of microstructures and CSR fluctuations caused by self-interaction is *tremendously complex*, and even **no** proper solution or traditional control methods to generate a longitudinal RF feedback to the RF cavity.

- Which device is suitable to cover many different kinds of machine learning approaches?

- Is there some general tool to transfer the Machine Learning (ML) model from ML experts to engineers?

- How to allocate the different machine learning tasks on DAQ?

Machine learning (ML) will not replace the traditional approach in every case. But in some applications, take the two above mentioned applications as examples, due to the complexity of the problem, it may be the only solution to the problem. In the field of High Energy Physics (HEP), machine learning becomes a novel data analysis approach and many applications have been reported by white paper [18].

For other situations, machine learning algorithms also could be regarded as a good alternative. The traditional data processing methods may need sophisticated professional knowledge of the application field, and a complex parameter adjustment process. Moreover, each method is targeting a dedicated application, therefore it has poor generalization ability and robustness. Deep learning is mainly based on data-driven feature extraction. Training on a large number of samples, deep and specific feature representation of the data set can be obtained, which makes the expression of the data set more efficient and accurate. That has lowered barriers to entry in some industries.

### **1.2 Machine Learning**

As Deep Learning (DL) is a branch of Machine Learning (ML), this thesis, will only use the term *Machine Learning* because some of the method mentioned do not belong to deep learning.

Machine learning methods could be divided into three major paradigms: *Supervised Learning*, *Unsupervised Learning Semi-supervised Learning* and *Reinforcement Learning*. These algorithms are addressing different problems.

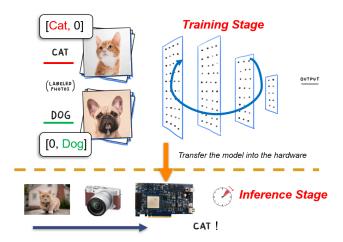

This thesis will focus on *Supervised Learning* and *Reinforcement Learning*, which is the most prevalently used approaches. The *Supervised Learning* (SL) is learning a model from the training dataset of labelled examples by machine learning engineer, and use the model for inference. Some of the typical tasks could be a classification or regression problem. On the other side, *Reinforcement Learning* (RL) is designed to maximize long-term future rewards. The algorithm aims to find an optimal control under the finite Markov Decision Processes (MDPs). Both SL and RL have *training* stage and *inference* stage. The *training stage* is how the model or algorithm becomes clever, no matter which approach it is to use. The *inference* is to use the **trained** model/algorithm to solve the reality problem.

Figure 1.2: The training and inference stage in supervised learning are normally independent. The training stage is realized often on GPUs/CPUs due to a floating-point calculation and machine learning framework availability, while inference can be implemented also on hardware accelerators.

#### 1.2.1 Supervised Learning

As shown in Fig (1.2), the label cat or dog needs to be prepared before the training stage. The model will try to extract the pattern hidden behind the training data set with its corresponding label. Once the training stage is finished and the model is verified, the parameters (e.g. the weights and biases in Neural Network, Convolutional Network or Recurrent Neural Network) is keep fixed. Then it validated in an inference stage, for instance, an image recognization task, only the forward pass of the network is required to implement on the hardware. After the verification, if the model satisfies the requirement, the model will be transferred to the hardware for the inference. The inference hardware could be FPGA/GPU/CPU/ARM and/or any other hardware devices. For realization in DAQ systems, several questions need to be answered:

- Which device is more suitable for the inference stage of SL?

- Is it obliged to deploy also the training process on the hardware for supervised learning applications?

- Are there any tools to help to decrease the developing time to transfer the model from the machine learning environment to the hardware platform?

- Is there a suitable device or platform that could cover as much supervised learning as possible?

#### 1.2.2 Reinforcement Learning

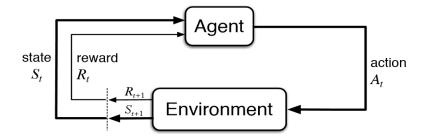

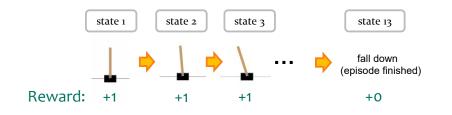

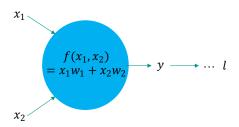

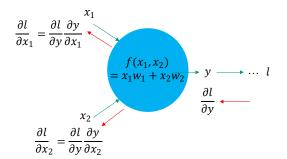

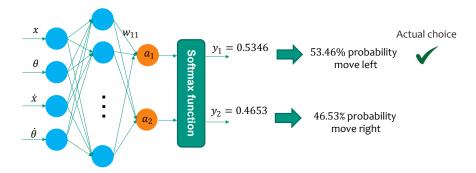

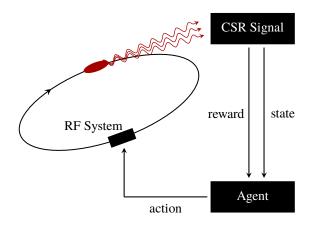

As to Reinforcement Learning, the model is established through interaction with the system that needs to be controlled. Thus, in this case, there is no training data like supervised learning required. The training data is generated online by interaction with the system to be modelled. There are three basic components in RL: agent, action, and environment (normally a state signal representing the environment). An agent is a decision-maker, and that means generate proper action at each step. Then the agent action will be sent to the environment. The environment

reacts to the actions and presents a new state to the agent shown in Fig (1.3). After this step, the agent will collect the interaction information and use such information to learn.

The rules of *Go-playing* are simple and elegant, but the ways of playing vary largely. It takes a lot of practice and studies to master its connotation. Go is considered to be one of the most complex board games in the world. Writing a program that possesses the capability of strategy, memory, observation, judgement and counting is extremely difficult. Therefore to set up the reinforcement learning framework and to let the agent learning directly from the interaction with the game is an attractive alternative. The immediate or long-term wining or failure indication will lead the machine learning to become more "clever". The agent AlphaGo defeated the human European Go champion by 5 games to 0 with reinforcement learning together with a tree search algorithm [19]. As mentioned earlier, reinforcement learning is acquiring training data during the interaction stage. This implies that the inference and training process needs to be considered as one unit. Several questions need to be answered:

- Which device is suitable to implement reinforcement learning with both the inference stage and training stage?

- Is it necessary to deploy the training process also on the hardware?

- If required, are there tools to help decrease the developing time that transferring the training process from reinforcement learning engineering to electronic engineering?

- Is there a suitable device or platform that is able to cover most of the advanced reinforcement learning algorithms?

Figure 1.3: Go is an abstract strategy board game for two players [20]. Under the definition of reinforcement learning concept [19], one player act as an agent, the other one is its opponent, acting as the environment. The Go play continues in a way that agent and opponent give their movements one after each. Once the opponent settles the stone, then the state (the location of each stone on the board) is changed. After the agent receives the state signal, it will generate the action for itself. The environment will change according to such movement. During each step, the reward signal also generates from the environment, that guide the agent to learn from each step.

### **1.3** Machine Learning applications

Machine learning (ML) is the most common method in Artificial Intelligence (AI). In the field of High Energy Physics (HEP), machine learning methods have been used for data analysis. Many tools have been presented since 2010. The following examples demonstrate the success of those applications in SL and RL.

In High-energy Physics after the collision of high eneretic particles, beams of secondaries are generated. Jets denotes high-energetic, directed beams of particles. The main task of Jet Physics is to identity the various particles after collision. For jet multiclass classification problems at the Large Hadron Collider (LHC) at Conseil Européen pour la Recherche Nucléaire CERN [21]. Convolutional Neural Network (CNN) are used to discriminate quark and gluon jets The Compact Muon Solenoid (CMS) [22] collaboration at LHC considers using convolutional layers and Recurrent Neural Network (RNN). The Graphic Neural Network (GNN) are also used for the analysis of jet substructures [23].

The heavy-ion experiments follows the theory of Quantum Chromodynamics (QCD). The QCD have two different transition: a crossover [24] or first order [25]. The CNN is used to identify two different equation of state (EoS) [26]. The PANDA detector (antiProton ANnihilation at DArmstadt) [27] is a multi-purpose detector system. The task of track finding aims to identify particles belonging to the same track. The neural network is used for hit aggregation in [16], and a improved GNN method in [28].

The emission of Coherent Synchrotron Radiation (CSR) depends on the shortness of the electron bunches. The self-interaction of the bunch causes micro-bunching instability. The Karlsruhe Institute of Technology (KIT) storage ring Karlsruhe Research Accelerator (KARA) aims at the stabilization of the emitted THz radiation to tackle the problem of micro-bunching instability. A reinforcement learning (RL) based method is planned to be implemented through an RF feedback system located at storage [17].

### **1.4 Accelerating Machine Learning**

To use machine learning in DAQ systems, often real-time requirements need to be fulfilled. Accelerated Machine Learning is a topic that reached out beyond scientific applications, including industrial use-cases. How the algorithm is been accelerated firstly depends on the algorithm itself, and its corresponding problem set to be solved. Secondly, the precision, power, throughput, latency and cost required by application [29].

If one combines two different stages (training and inference) with two different methods (reinforcement learning and supervised learning), there will be four components that have the possible requirement for implementation and acceleration:

- 1. supervised learning training process

- 2. supervised learning inference process

- 3. reinforcement learning training process

- 4. reinforcement learning inference process

Not always all four implementations are required. Each algorithm results in a different implementation strategy. Normally, for both supervised learning and reinforcement learning, the training process is not needed any more during the inference procedure cause the model has already been verified by the test data set. Especially for supervised learning, because the training process always happens off-line, therefore a natively long preparation time for data collection, model fine-tuning happens in the supervised learning based engineering.

For reinforcement learning, however, the consideration will be slightly more complex. First, the inference process part must be included because it will be the final solution. Whether the learning process is needed is depends on the problem set. For example, in autonomous driving, the tasks in [30] are mainly divided into two different tasks, the test task and the training task. During the test task, the episode is running with a fixed optimal policy, and that is a pure inference stage. But in the training task, it chooses a task with a noisy policy that will randomly choose some other non-optimal policy to explore the action space. Because the learning stage is required happening in the field, thus, for a hardware implementation, needs to deploy both the inference stage and the training stage. The training stage for supervised learning is already difficult, moreover, because some of the prevalent RL algorithm frameworks is more complex than supervised learning, the reinforcement learning training process required the single/double precision Floating Point Unit (FPU) to guarantee the computational accuracy of the training process. This again requires a capable application processor on the DAQ system.

For accelerated machine learning the questions listed above need to be refined.

- 1. Which Algorithm will be accelerated? Supervised Learning (SL) or Reinforcement Learning(RL)?

- 2. Is there any difference between SL acceleration and RL acceleration?

- 3. The weights of the model(SL or RL) is fixed or need to be updated to adapt to the changing environment?

- 4. Which part should be put into the hardware, training process, inference part or both?

- 5. How to accelerate the SL inference part?

- 6. How to accelerate the RL inference part?

- 7. Is there any similarity between SL and RL inference?

- 8. How to process the RL training process on application processor?

- 9. Which main chip will be selected for SL and RL? FPGA, GPU, CPU, ARM or SoC?

#### **1.5 Hardware platform**

High-performance DAQ systems are today based on FPGAs. They provide a variety of highthroughput links and an enormous amount of logic cells. In recent years, embedded processors have been added to FPGA devices. The combination of both units makes FPGA-based DAQ boards an ideal platform for machine learning integrated with high bandwidth data acquisition and control. But only the latest FPGAs using the ARM architecture possess the potential to own adequate ability of application performance. There is a wealth of portable software, drivers and modules under the ARM-based embedded Linux system. Thus it provides both relatively powerful computing power and control capability. Especially for machine learning, FPGA could achieve low latency and high bandwidth for inference. For some of the small networks, the ARM could undertake the responsibility of training where will show in Chapter 7, 8, and 9. The first embedded processors have already presented in the early 2000 years. Among the first heterogeneous architecture are the Virtex-4 FX family [31], Virtex-5 FXT families [32]. The Virtex-5 FXT is a high-performance embedded system. The FPGA logic is one to two-speed grade improvement over Virtex-4 devices. It owns PowerPC 440 (PPC440) cores embedded with FPGA logic. One of the major drawbacks of this generation system-on-chip is it required a hardware engineer to program the FPGA part first. Then the peripherals, memory systems, including the data path across processor and logic, is required for the design. Finally, the processor could be programmed. Xilinx delivered the Zynq-7000 All Programmable SoC [33] in the winter of 2011. This enables the developer to jump directly to the hardware-software co-design, both hardware development and software development are independent and can happen simultaneously then they are combined by the system engineer.

It already improves the embedded processor from PPC440 to Coretex-A9 (Zynq-7000), thus resulting in a performance improvement from 1.0 to 2.5 DMIPS. Then comes the Zynq Ultra-Scale+ equipped with Cortex-A53 which increase this performance to 3.45 DMIPS, enabling a powerful application processor on the DAQ.

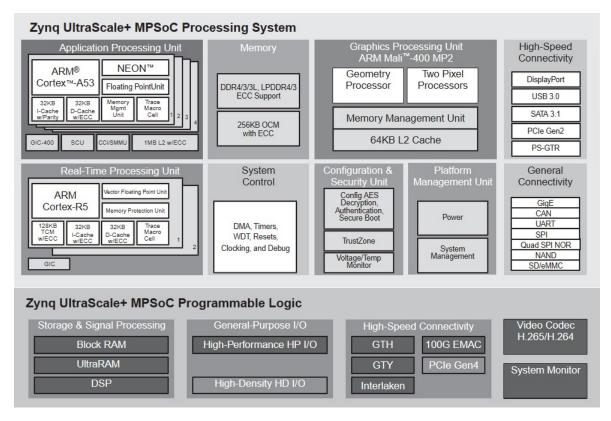

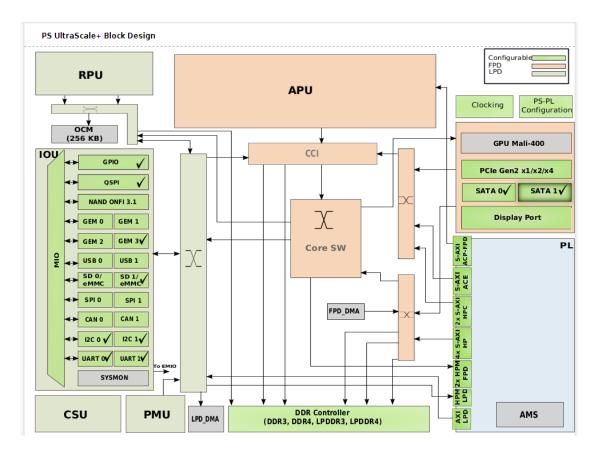

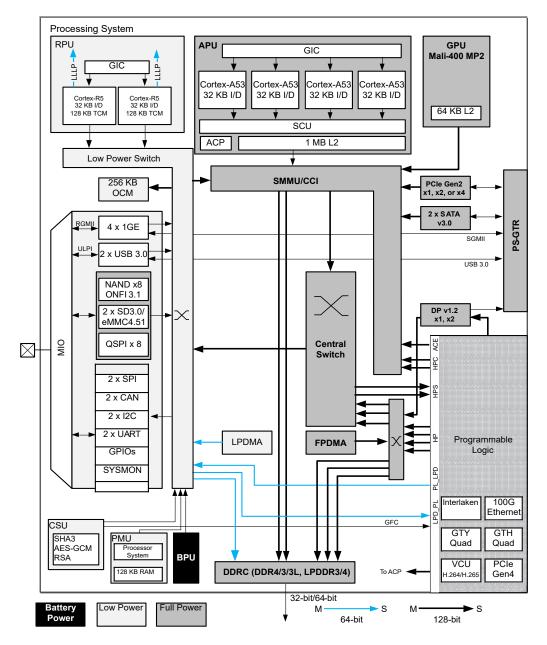

Figure 1.4: Zynq UltraScale+ MPSoC block design

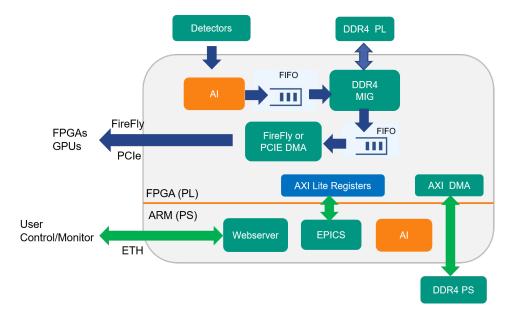

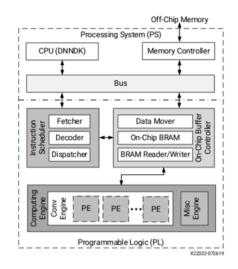

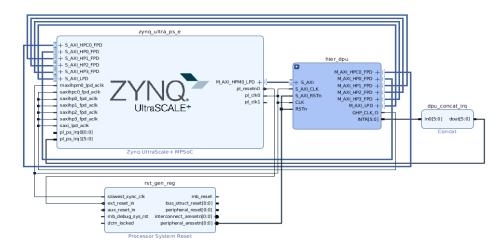

Xilinx UltraScale+ MPSoC architecture family of products [12] integrates a feature-rich 64-bit quad-core or dual-core Arm Cortex-A53, dual-core Arm Cortex-R5 based processing system (PS) and Xilinx programmable logic (PL) UltraScale architecture in a single device. At the PS part, the embedded Linux system could be built and for data acquisition, processing and general applications. On the other hand, at the PL part, the DMA could be integrated into the FPGA and can communicate with GPU directly with high data bandwidth. As shown in Fig (1.4), at the PS part of the Zynq UltraScale+ device, the ARM Cortex-A53 and real-time ARM Cortex-R5 could provide a powerful embedded Linux system and/or bare mental application. These processors have multiple access method to soft intellectual property (IP)

core located at PL side through rich internal buses. This heterogeneous MPSoC saves PCB wiring resources and DAQ system development time.

Demonstrated in Fig (1.4), the top part of the picture is the processing system of Zynq. It is consists of an application processing unit, real-time processing unit, graphics processing unit, memory controller, and connectivity for abundant peripherals. At PS part the Zynq Ultra-Scale+ device, the ARM Corex-A53 and real-time ARM Cortex-R5 could provides a powerful embedded Linux system and/or bare mental application. These processors have multiple access method to soft intellectual property (IP) core located at PL side through rich internal buses. This heterogeneous MPSoC save PCB wiring resources and DAQ development time.

The bottom side of the picture of block design is the programmable logic of Zynq. It contains system logic cells, look-up-table (LUTs), Digital Signal Processing (DSPs), block RAM, UltraRAM, general-purpose inputs/outputs and many high-speed connections.

#### **1.6 Chapter arrangement**

This dissertation has two parts. The first part is the hardware design. Within which Chapter 2 is the design and test of the novel multipurpose PCIe readout card (HighFlex2); Chapter 3 demonstrates the works around system-on-chip and embedded Linux system. The second part of the dissertation covers artificial intelligence implementation methods and its application based on HighFlex2. Chapter 4 will give an introduction to machine learning, basic mathematic theory in supervised learning, and its acceleration methods; In Chapter 5, the Xilinx DPU is implemented as a solution for supervised learning inference on HighFlex2; Chapter 6 introduce the major knowledge required in the dissertation; Chapter 7 demonstrate the efforts to develop the reinforcement learning (Policy Gradient) training process on HighFlex2 and its testbench; Chapter 8 shows the Deep Deterministic Policy Gradient implementation method on HighFlex2; Chapter 9 is the overall reinforcement learning design at KARA; Chapter 10 is the conclusion.

# Part I

# **Data Aquisition System Hardware Design**

## **Chapter 2**

### Hardware design of the readout card

This chapter focuses on the hardware design of a PCIe readout card based on the recent Zynq-MPSoC programmable family. For large-scale real-time data process, the FPGA-GPU combination is considered as one suitable solution [34]. For many years, the Institute for Data processing and Electronics (IPE) has been involved in the development of heterogeneous FPGA-GPU systems for the processing of the data in real-time. As an upgraded version of the existing readout card (so-called "HighFlex" [35]) to meet the needs of high-speed data processing and artificial intelligence, a major feature provided by HighFlex2 is its compatibility with the PCIe standard bus.

There are several commercial development platforms on the market, the HTG-930 [36] and HTG-Z920 [37] from HiTech Global, Xilinx ZCU102 [38], ZCU104 [39] and ZCU106 [40]. Unfortunately, none of the evaluation boards meets all the requirements required by the projects, such as electrical/optical interfacing, data throughput, flexibility, etc. Therefore, a custom readout card based on PCIe generation 3/4 with 16 lanes has been developed.

For example, the ZCU102 includes a PCIe Generation 2 with x4 lanes connected to the ARM Processor Subsystem (PS) by dedicated GTR transceivers which support data rate up to 6 Gb/s. While the custom readout card is based on PCIe generation 3/4 with 16 lanes, which allows managing a data throughput of over 200 Gb/s in continuous readout mode. The CPU/GPU platform is the data destination, therefore the readout card is a PCIe *Endpoint* device, the PCIe Gen3/4 also needs to connect with the PL part of the Zynq device where PCIe Integrated Block [41] is supported. The HTG-930 and HTG-Z920 support x8 PCIe Gen4 or x16 PCIe Gen3. However, the HTG-930 is mounted with Xilinx Virtex UltraScale+ [42] device, which is not an MPSoC. Therefore, it is not fully suitable to guest multiple machine learning implementations and an embedded operating system. The HTG-Z920 is based on a Xilinx MPSoC UltraScale+ PCIe platform but several important interfaces are not available, like the Serial Advanced Technology Attachment (SATA), Ethernet, and in terms of flexible high-speed data transmission, FireFly [43] connection.

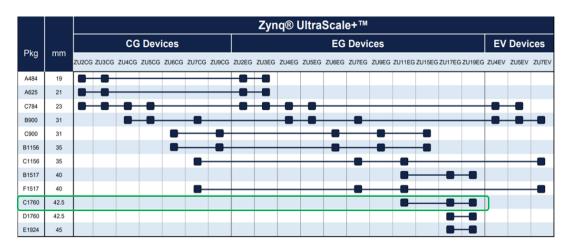

The comparison between the available evaluation boards and the HighFlex2 is shown in Fig (2.1). The last reason is scalability. The chip mounted on the ZCU102 is equipped with Zynq UltraScale+ XCZU9EG-2FFVB1156E MPSoC and both ZCU104 and ZCU106 have Zynq UltraScale+ XCZU7EV-2FFVC1156 MPSoC on top. But such devices do not integrate the PCIe hard-core and the necessary number of DSP slides that are required for the corrected implementation of the ML network on FPGA. The selected Zynq is UltraScale+ XCZU11EG-1FFVC1760 MPSoC. As shown in Fig (2.3), the direct comparison between the ZU7EG and the ZU9EG, mounted on the evaluation boards, and the selected Zynq device ZU11EG shows as the selected device integrates up to 4 PCIe hard-core logics, a large number of DSP slices

| Property  | ZCU102              | HTG-930               | HTG-Z920            | HighFlex2           |

|-----------|---------------------|-----------------------|---------------------|---------------------|

| Main Chip | Zynq<br>Ultrascale+ | Virtex<br>Ultrascale+ | Zynq<br>Ultrascale+ | Zynq<br>Ultrascale+ |

| PCle      | No                  | Yes                   | Yes                 | Yes                 |

| FireFly   | No                  | No                    | No                  | Yes                 |

| FMC+      | No                  | Yes                   | Yes                 | Yes                 |

| PL DDR4   | Yes                 | Yes                   | Yes                 | Yes                 |

| PS DDR4   | Yes                 | No                    | Yes                 | Yes                 |

| Ethernet  | Yes                 | No                    | No                  | Yes                 |

| SD Card   | Yes                 | No                    | Yes                 | Yes                 |

| SATA      | Yes                 | No                    | No                  | Yes                 |

Figure 2.1: Comparison between HighFlex2 readout card and the available commercial boards.

(up to 3000), which are necessary for ML implementation, and a large number of both GTY and GTH serial high-speed transceivers, which are necessary for the implementation of the fast optical and electrical interfaces (e.g. PCIe x16). Moreover, the selected FPGA package FFVC1760 allows the migration that enables the re-mounting of the other high-end ZU17EG and ZU19EG devices on the HighFlex2 card.

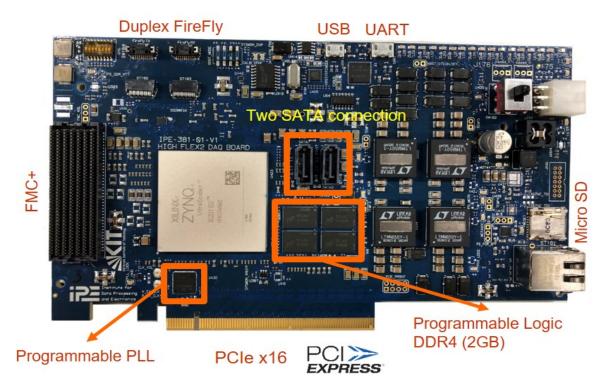

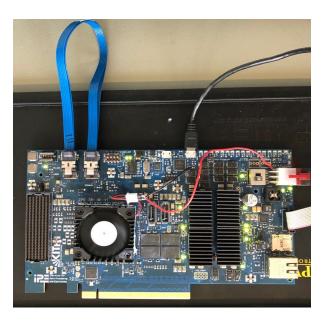

Figure 2.2: Top side of HighFlex2 DAQ card

In Fig (2.2), the fully assembled HighFlex2 DAQ card is shown. All components on the board are tested and verified. The main processor on the centre to the left of the board is Zynq UltraScale+ XCZU11EG-1FFVC1760 MPSoC. Located on the left side is the FMC+, which is a VITA 57.4 standard connector. On the top left side are two FireFly connectors. The top side is

a USB and a UART connector for the PS part. On the right-bottom side are the Micro SD card and Ethernet connector. The bottom side is the PCIe x16 lanes slot. Also on the bottom left of the board is the Phase Locked Loop (PLL) chip, which has 10 programmable clock outputs. The middle part of the board has two SATA connectors where one could plug in an external storage device like SSD. Below the SATA connectors are four DDR4 chips, which contain 2 GB size in total. On the backside of the board, there is a 72 bits data width SODIMM which provides processing system with different DDR sizes compatibility(4GB, 8GB, and 16GB).

| (1)                               |                                                                                      |                     |           |           |           | (          |            |           |           |          |        |

|-----------------------------------|--------------------------------------------------------------------------------------|---------------------|-----------|-----------|-----------|------------|------------|-----------|-----------|----------|--------|

| Device Name <sup>(1)</sup>        | ZU2EG                                                                                | ZU3EG               |           |           |           |            |            |           |           | ZU17EG   | ZU19EG |

| Processor Core                    | Quad-core ARM <sup>®</sup> Cortex <sup>™</sup> -A53 MPCore <sup>™</sup> up to 1.5GHz |                     |           |           |           |            |            |           |           |          |        |

| Memory w/ECC                      | L1 Cache 32KB I / D per core, L2 Cache 1MB, on-chip Memory 256KB                     |                     |           |           |           |            |            |           |           |          |        |

| Processor Core                    | Dual-core ARM Cortex-R5 MPCore™ up to 600MHz                                         |                     |           |           |           |            |            |           |           |          |        |

| Memory w/ECC                      |                                                                                      | L1 (                | Cache 32  | KBI/Dp    |           | • •        | •          |           | 8KB per   | core     |        |

| Graphics Processing Unit          |                                                                                      |                     |           | Μ         |           |            | to 667MI   | Ηz        |           |          |        |

| Memory                            |                                                                                      |                     |           |           |           | Cache 64   |            |           |           |          |        |

| Dynamic Memory Interface          |                                                                                      |                     | x32/x     | 64: DDR4  | , LPDDR4  | , DDR3, [  | DDR3L, LP  | DDR3 wi   | th ECC    |          |        |

| Static Memory Interfaces          |                                                                                      |                     |           |           | NAN       | D, 2x Qua  | id-SPI     |           |           |          |        |

| High-Speed Connectivity           |                                                                                      | PCIe <sup>®</sup> G | en2 x4, 2 | x USB3.0  | , SATA 3. | 1, Display | Port, 4x   | Tri-mode  | Gigabit   | Ethernet |        |

| General Connectivity              |                                                                                      | 2xUSB               | 2.0, 2x S | D/SDIO,   | 2x UART,  | 2x CAN     | 2.0B, 2x I | 2C, 2x SI | PI, 4x 32 | b GPIO   |        |

| Power Management                  |                                                                                      |                     |           | Full / L  | ow / PL / | Battery    | Power Do   | omains    |           |          |        |

| Security                          |                                                                                      |                     |           |           | RSA,      | AES, and   | I SHA      |           |           |          |        |

| AMS - System Monitor              |                                                                                      |                     | 10        | -bit, 1MS | PS – Tem  | perature   | and Volta  | age Moni  | tor       |          |        |

|                                   |                                                                                      |                     |           |           | 12 x 32/  | 64/128b    | AXI Ports  |           |           |          |        |

| System Logic Cells (K)            | 103                                                                                  | 154                 | 192       | 256       | 469       | 504        | 600        | 653       | 747       | 926      | 1,143  |

| CLB Flip-Flops (K)                | 94                                                                                   | 141                 | 176       | 234       | 429       | 461        | 548        | 597       | 682       | 847      | 1,045  |

| CLB LUTs (K)                      | 47                                                                                   | 71                  | 88        | 117       | 215       | 230        | 274        | 299       | 341       | 423      | 523    |

| Max. Distributed RAM (Mb)         | 1.2                                                                                  | 1.8                 | 2.6       | 3.5       | 6.9       | 6.2        | 8.8        | 9.1       | 11.3      | 8.0      | 9.8    |

| Total Block RAM (Mb)              | 5.3                                                                                  | 7.6                 | 4.5       | 5.1       | 25.1      | 11.0       | 32.1       | 21.1      | 26.2      | 28.0     | 34.6   |

| UltraRAM (Mb)                     | -                                                                                    | -                   | 13.5      | 18.0      | -         | 27.0       | -          | 22.5      | 31.5      | 28.7     | 36.0   |

| Clock Management Tiles (CMTs)     | 3                                                                                    | 3                   | 4         | 4         | 4         | 8          | 4          | 8         | 4         | 11       | 11     |

| DSP Slices                        | 240                                                                                  | 360                 | 728       | 1,248     | 1,973     | 1,728      | 2,520      | 2,928     | 3,528     | 1,590    | 1,968  |

| PCI Express <sup>®</sup> Gen 3x16 | -                                                                                    |                     | 2         | 2         | -         | 2          | -          | 4         | -         | 4        | 5      |

| 150G Interlaken                   | -                                                                                    | -                   | -         | -         | -         | -          | -          | 1         | -         | 2        | 4      |

| 100G Ethernet MAC/PCS w/RS-FEC    | -                                                                                    | -                   | -         | -         | -         | -          | -          | 2         | -         | 2        | 4      |

| AMS - System Monitor              | 1                                                                                    | 1                   | 1         | 1         | 1         | 1          | 1          | 1         | 1         | 1        | 1      |

| GTH 16.3Gb/s Transceivers         | -                                                                                    | -                   | 16        | 16        | 24        | 24         | 24         | 32        | 24        | 44       | 44     |

| GTY 32.75Gb/s Transceivers        | -                                                                                    | -                   | -         | -         | -         | <u> </u>   | - )        | 16        | ) -       | 28       | 28     |

| Extended <sup>(2)</sup>           | -1 -2                                                                                | 2 -2L               |           | -1 -2     | -2L -3    |            |            |           | 1 -2 -2L  | -3       |        |

| Industrial                        |                                                                                      |                     |           |           |           | -1 -1L -2  |            |           |           |          |        |

Figure 2.3: Zynq UltraScale+ EG devices [44]

Figure 2.4: MPSoC Device Migration Table [44]

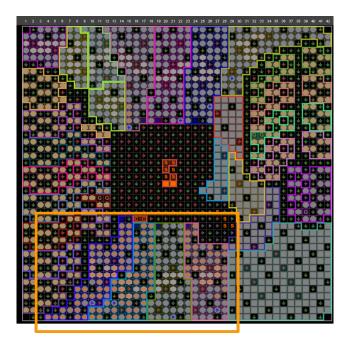

#### 2.1 FPGA resources allocation

Zynq UltraScale devices provide various I/O and offer: several Giga-bit transceivers, Highperformance, (HP), high-density (HD), and high-range (HR) I/O banks. The HP banks could support different voltage level of I/O standard, LVDS, and many other kind of chip-to-chip interfaces. The HD I/O banks are designed for low-speed purpose.

The Xilinx high-speed transceivers on FPGA are designed to cover many high-speed protocols that is available nowadays. The UltraScale+ device integrates two different types of high-speed transceivers: the GTH and GTY [45]. GTH has a 32.75 Gbps speed and GTY owns 16.3 Gbps respectively. XCZU11EG-1FFVC1760 have 32 number of GTH transceivers and 16 GTY transceivers.

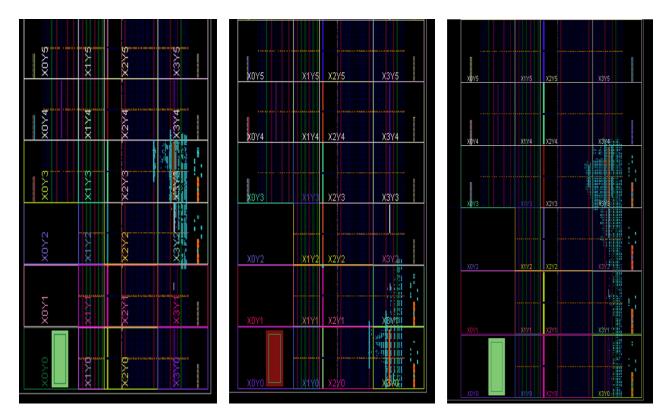

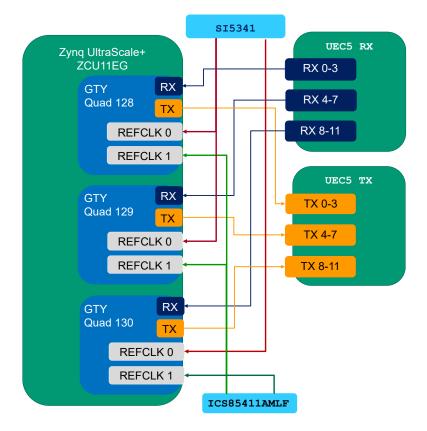

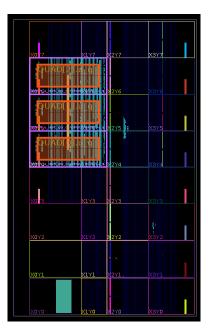

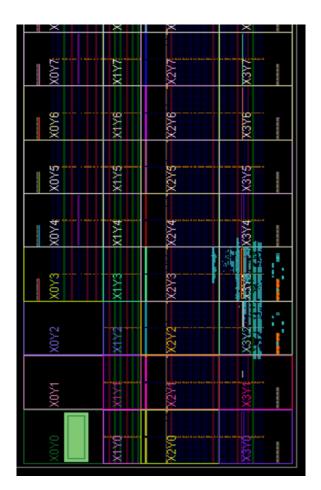

To optimize the performance of the optical data link, 12 full-duplex lanes of the FireFly are routed on 12 GTY transceivers. Therefore, the left 4 GTY resources are routed to FMC+ gigabit transceiver data pairs (DP). PCIe connection requires x16 transceivers, thus 16 lanes of GTH are employed for this purpose. The left 16 GTH are routed to FMC+ DP. Therefore, FMC+ contains 4 GTY and 16 GTH, providing a total 391.8 Gbps connection from/to a FMC+ mezzanine card. In Fig (2.5), the resources allocation plan map are shown.

| GTY Quad 131<br>X0Y16-X0Y19                | PCIE4<br>X0Y4 | HP I/O Bank 71<br>R                        | HD I/O Bank 91<br>Q | GTH Quad 231<br>X0Y28-X0Y31<br>H [RN]               |

|--------------------------------------------|---------------|--------------------------------------------|---------------------|-----------------------------------------------------|

| GTY Quad 130<br>X0Y12-X0Y15<br>L [L]       | CMAC<br>X0Y1  | HP I/O Bank 70<br>S                        | HD I/O Bank 90<br>P | GTH Quad 230<br>X0Y24-X0Y27<br>G [RN]               |

| GTY Quad 129<br>X0Y8-X0Y11<br>K [L] (RCAL) | ILKN<br>X0Y0  | HP I/O Bank 69<br>T                        | HD I/O Bank 89<br>O | GTH Quad 229<br>X0Y20-X0Y23<br>F [RN]               |

| GTY Quad 128<br>X0Y4-X0Y7<br>J [L]         | PCIE4<br>X0Y2 | HP I/O Bank 68<br>U                        | HD I/O Bank 88<br>N | GTH Quad 228<br>X0Y16-X0Y19                         |

|                                            |               |                                            |                     |                                                     |

| GTY Quad 127<br>X0Y0-X0Y3                  | CMAC<br>X0Y0  | HP I/O Bank 67<br>F                        | PCIE4<br>X1Y1       | GTH Quad 227<br>X0Y12-X0Y15<br>D [RS]               |

|                                            |               | HP I/O Bank 67<br>F<br>HP I/O Bank 66<br>E |                     | X0Y12-X0Y15                                         |

| X0Y0-X0Y3                                  | X0Y0          | F<br>HP I/O Bank 66                        | X1Y1<br>SYSMON      | X0Y12-X0Y15<br>D [RS]<br>GTH Quad 226<br>X0Y8-X0Y11 |

Figure 2.5: The Zynq XCZU11EG-1FFVC1760 packaging diagram [46]

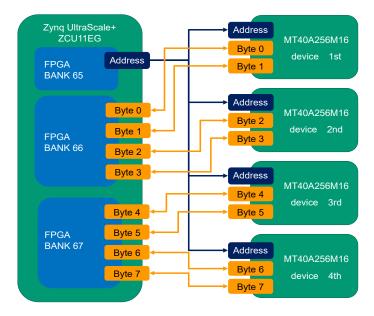

On the top-left side of the plan map, the *red* colour rectangular frames three GTY Quads (GTY Quad 128-130) for FireFly. In addition to these, one HD I/O Bank 90 has been routed to manage the I2C interface required from the FireFly optical connection. On the bottom-right side of the plan map, the GTH Quad (GTH Quad 224-227) (*green* colour) shows PCIe transceivers allocation. The *blue* colour part are the Quads and Banks that connected with FMC+. The *yellow* rectangular frames the Banks (HP I/O Bank 65-67) that employed to connect the FPGA to the DDR4 memory device integrated on the HighFlex2 card.

### 2.2 Clock distribution

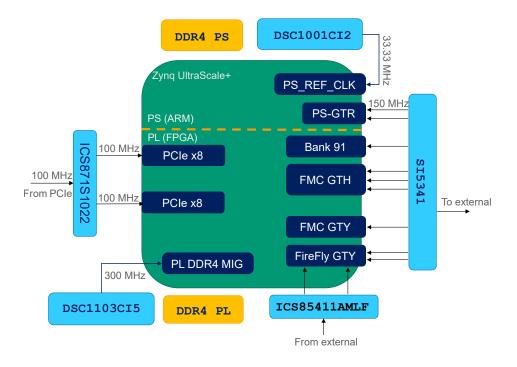

The clock distribution is fundamental to enable digital communication. The overall clock distribution on HighFlex2 is shown in Fig (2.6). The clocks which are provided to the Processing System are PS\_REF\_CLK and PS-GTR. The PS-GTR clock is employed for PS-GTR highspeed Transceivers. These transceivers are connected to 2 SATA connectors and operating in raid configuration. The GTR requires a clock of 150 MHz.

Figure 2.6: HighFlex2 clock overall distribution diagram

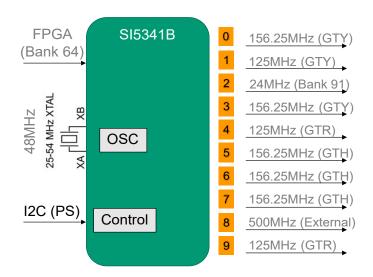

Figure 2.7: Clock chip SI5341 could generate up to 10 independent clocks.

For PCIe logic block, a PLL (ICS871S1022) jitter attenuator clock generator is employed to provide the reference clocks fully compliant to the PCIe hard-core Generation 4 Fig (2.6). The clocks are distributed in such a way to instantiate one single PCIe core generation 4 x8 lanes or two parallel PCIe cores that can support generation  $4 \times 16$  lanes. The mentioned clock

scheme will be discussed in the next paragraph. For PL (Programmable Logic) part memory, a 300 MHz clock is provided to the Memory Interface Generator (MIG) IP Core. The MIG is an IP Core that combines the controller and physical layer (PHY) for interfacing the FPGA user designs to the DDR4 memory device. For PS (Processing System) part memory, the DDR4 connected with the PS part have an internal clock provided directly from the DDR4 controller integrated on the PS. The FireFly have two options: one from on-board SI5341 clock chip, and the second option is from external clocks that defined by users. This provides a flexible operation mode.

Because the PS part and PL part is working independently, once the PS is powered up, the PS I2C could be used to configure the programmable low-jitter PLL SI5341 in Fig (2.6). This allows the clocks to be ready before the PL starts to work. This low-jitter 10-output programmable clock generator enables a flexible clock source configuration with the output which could be programmed to 100 Hz to 1028 MHz. The reference clock of each GTH and GTY Quad could have both *on-board* clock source and external clock source. The user could configure the clock source according to the specific application through I2C directly connected to the processing system. The configuration of the clock distribution could be programmed by SILICON LABS ClockBuilder Pro software [47]. All the settings will be stored in a C header file. The user could import that file into Xilinx Software Development Kit (SDK) and program the PLL by the I2C interface managed by the ARM easily.

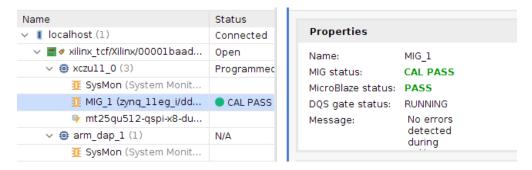

The Fig (1) in Appendix A shows the software structure in Xilinx SDK. Each channel can be configured to LVDS, LVPECL, LVCMOS, CML, and HCSL with different signal amplitude. Fig (2.7) shows the default clock configuration pre-programmed on the HighFlex2 card. The input reference clock of the PLL can be selected between a reference clock, programmable by the FPGA (Bank 64), or a reference clock provided by local quartz.

#### 2.3 PCI Express circuit design

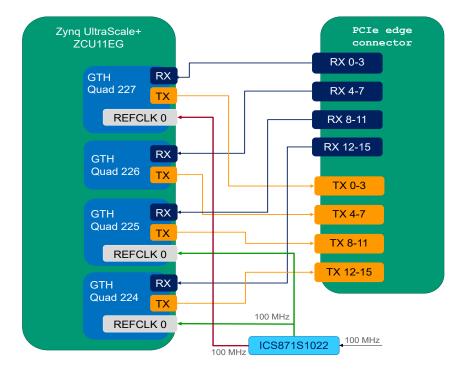

Fig (2.9) illustrated out the GTH transceivers and their connection to the PCIe giga-transfer serial lines. Four GTH quad are employed to connect the 16 full-duplex lines of the PCIe: GTH Quad 224, 225, 226 and 227. The GTH Quad 224 and 225 are connected to the lines from 8 to 15 of PCIe, which is connected to a PCIe hard-core with x8 lanes, generation 4. They use the 100 MHz clock source from ICS87S1022. The GTH Quad 226 and 227 together own the 0-7 RX/TX. The reference clock is shown in Fig (2.9).

The routed PCIe connection scheme, shown in Fig (2.9), allows higher flexibility on the PCIe implementation in the FPGA. Several solutions are possible in Fig (2.8).

Figure 2.8: Three different PCIe configuration implementation. The left one is Gen 3/4 x8 lanes (TOP); The middle is the Gen 3/4 x8 lanes (BOTTOM); The right is generation 3 x 16 lanes.

Figure 2.12: Performance of the dual-core KIT DMA engine for PCIe Gen 3 x16

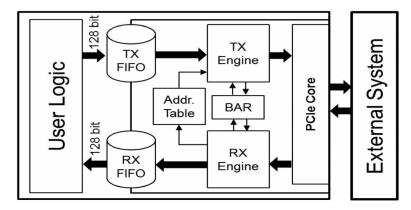

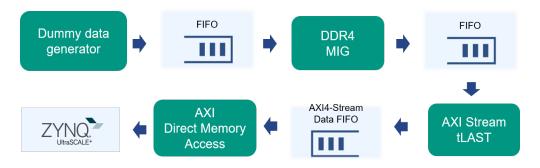

A preliminary test has been done to evaluate the corrected functionality of both PCIe interfaces. The FPGA architecture deployed in the HighFlex2 is based on a double-core KIT-DMA [15] operating with x16 lanes, PCIe generation 3. The architecture of the DMA engine is shown in Fig (2.10). The architecture consists of 4 parts: the TX engine, RX engine, address

Figure 2.9: Four GTH Quad are assigned to the PCIe  $\times 16$  edge connector directly.

Figure 2.10: Architecture of the KIT DMA engine for PCIe Gen 3 x8 [15]

table, and PCIe BAR. The TX/RX engine is used for transmitting/receiving data to/from an external system (e.g. CPU/GPU based server). The address table stores the descriptors defined by the driver and written from the Linux driver. Linux driver allocates the pages in the kernel memory and it writes their physical addresses inside this address table. This write operation only happens at the initialization stage. After which the FPGA could start to transfer the data from FPGA to the corresponding address that allocated before. A detail working principle is explained in [15].

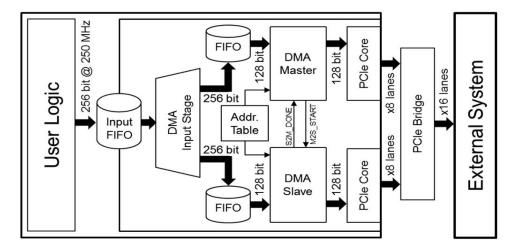

The double-core implementation is an extention of the single-core KIT-DMA shown in Fig (2.11). It consists in a Master-Slave architecture which is capable to work with two PCIe cores in parallel sharing the descriptor lists. The double-core architecture is shown in Fig (2.11).

To keep the architecture simple, a Master-Slave architecture was designed [15]. The principle is to have one DMA engine acting as a Master, and the second one as a Slave. Therefore, the Master initiates the DMA operation with the Linux driver. Once the DMA is started, the Master wakes the Slave up and both engines work together, shown in Fig (2.11). Both Mas-

Figure 2.11: Architecture of the dual-core KIT DMA engine for PCIe Gen 3 x16 [15]

ter and Slave core are working in parallel. This could double the throughput compared with single-core mode.

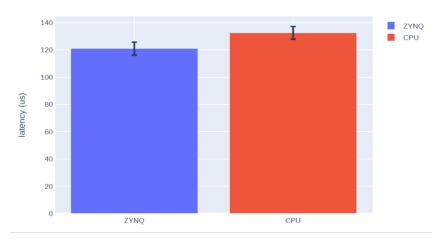

The result obtained through dual-core is presented in Fig (2.12), where each point is the mean values measured for several tests. With 256B payloads, it could reach 12.4 GB/s throughput with PCIe generation 3 and is expected to reach a throughput over 24 GB/s by means of two PCIe cores, generation 4.

### 2.4 FireFly circuit design

FireFly Micro Flyover System is the first interconnect system that gives a designer the flexibility of using micro footprint with high-performance optical and low-cost copper interconnects interchangeably with the same connector system. Samtec FireFly copper and optical cable systems provide the flexibility to achieve higher data rates to 28 Gbps for each lane and/or greater distances, simplifying board design and enhancing performance. Two FireFly connectors are present on the HighFlex2, offering the possibility to integrate up to 12 full-duplex lanes with each one operating up to 28 Gb/s. Each pair is consists of a 1 UEC5 series FireFly edge card socket connector for data transmission and a 1 UCC8 series FireFly connector for the configuration, control, and power of the optical link. The slow control is connected with HD I/O Bank 90 as shown in Fig (2.5).

Figure 2.13: Two UCC8 connectors for slow control not shown here. *Two* UEC5 data 12 lanes are allocated to *three* GTY Quads.

The circuit routing on HighFlex2 is demonstrated at Fig (2.13). The on-board PLL SI5341 (red arrow) and 85411 clock buffer for external user clock input (green arrow) provide the reference clock of the GTY Quads. The blue arrows are the RX lanes routing, and the yellow arrows show the TX routing. Through this simple principle, the HighFlex2 achieves the 12 lanes full-duplex FireFly.

Figure 2.14: UEC5 TX to UEC5 RX is connected directly to enable the FireFly 12 lanes loop-back test on HighFlex2.

Figure 2.15: The figure demonstrate the IBERT IP implementation and three GTY Quads FPGA implementation on HighFlex2.

Two UEC5 serves as TX and RX for a different direction. To exploit the potentiality offered by the FireFly technology, the FireFly data lines have been connected to the GTY transceivers of the FPGA. Each GTY transceiver provided by Zynq MPSoC could offer a data-link with speed up to 32.75 Gb/s. The Quad 128, 129 and 130 are adjacent allowing an excellent clock distribution that can be shared among all quads. The clock sources are fully configurable and can be provided by two sources: the programmable clock chip SI5341, or the external user clock. This configuration could provide the flexibility of different clock source and configurations.

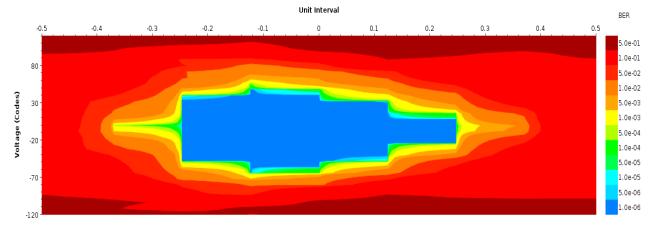

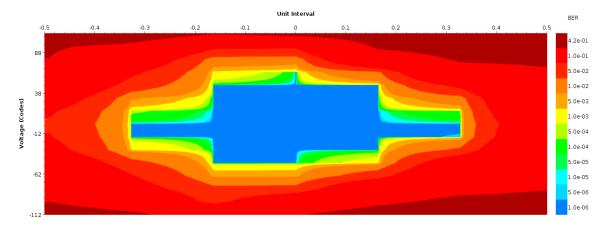

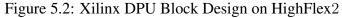

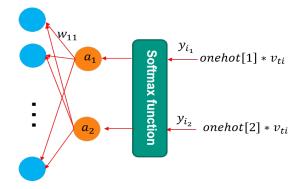

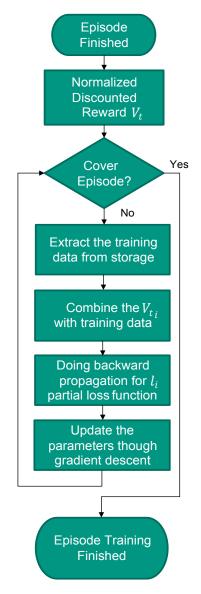

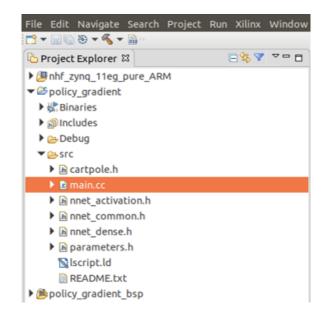

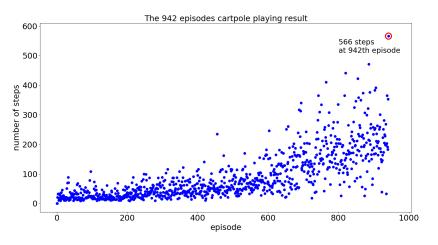

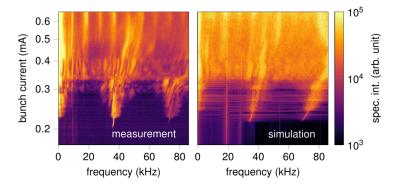

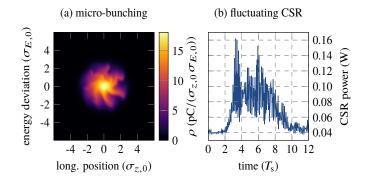

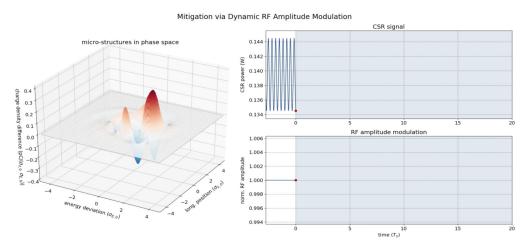

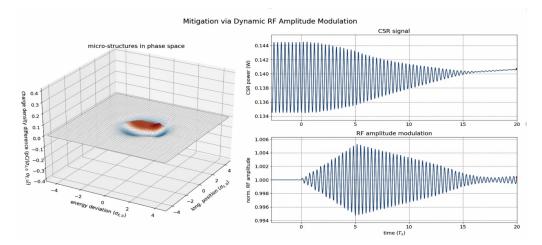

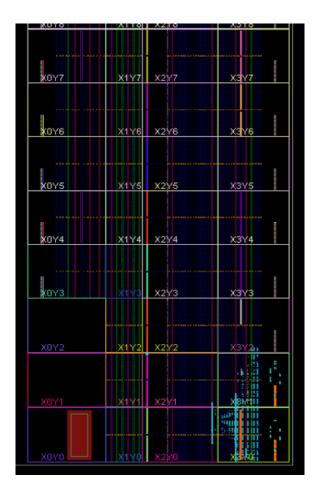

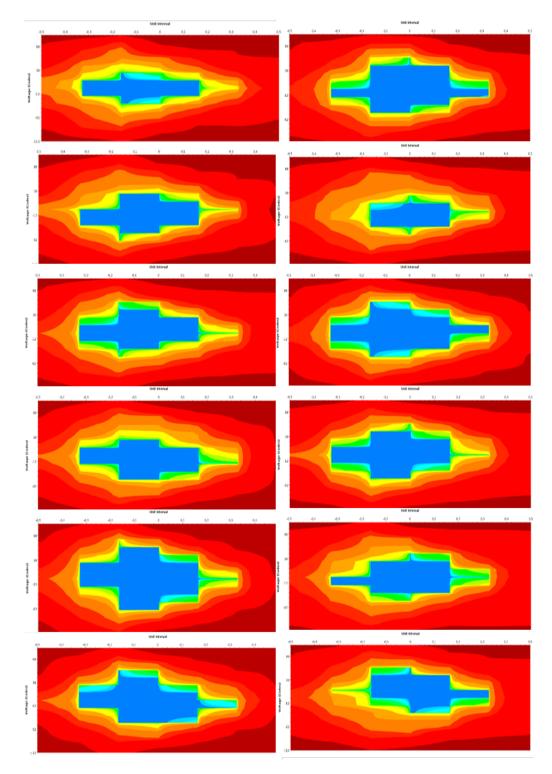

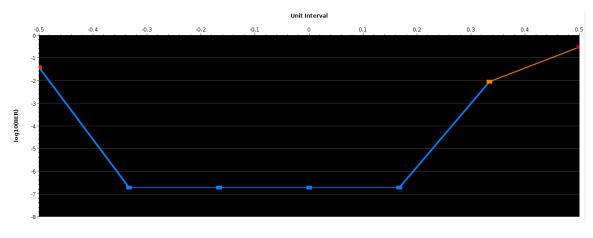

In order to test the performance of FireFly on HighFlex2, a FireFly copper cable is connected from UEC5 TX to UEC5 RX on HighFlex2 directly shown in Fig (2.14). This enables an on-board self loop-back test directly on HighFlex2 board. The Integrated Bit Error Ratio Tester (IBERT) is required. IBERT for UltraScale/UltrasScale+ GTY transceivers IP has been implemented and deployed in the FPGA. The FPGA placement of the FireFly GTY and the IBERT logic implementation location is shown in Fig (2.15). The IBERT test has been configured to test all 12 lanes in parallel at two different speeds, 20 and 25 GB/s. The test has been performed to test and verify the design of the fast differential transmission lines routed on the HighFlex2 board.