# Information Flow Analysis of Discrete Embedded Control System Models

vorgelegt von

Marcus Mikulcak, M.Sc. ORCID: 0000-0003-2900-2897

an der Fakultät IV – Elektrotechnik und Informatik

der Technischen Universität Berlin

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

– Dr.-Ing. –

genehmigte Dissertation

### Promotionsausschuss:

| Vorsitzender: | Prof. DrIng. Clemens Gühmann<br>Technische Universität Berlin       |

|---------------|---------------------------------------------------------------------|

| Gutachterin:  | Prof. Dr. rer. nat. Sabine Glesner<br>Technische Universität Berlin |

| Gutachter:    | Prof. DrIng. Christian Hammer<br>Universität Potsdam                |

| Gutachter:    | Prof. DrIng. Frank Slomka<br>Universität Ulm                        |

Tag der wissenschaftlichen Aussprache:

06. November 2019

#### Abstract

Embedded systems used in safety-critical domains have to uphold strict *safety* and *security* requirements. At the same time, their complexity has been strongly increasing across application domains. To manage this rise in complexity, manufacturers have shifted towards *model-driven development* methodologies. While successful in managing the complexity in the *development* of large, interconnected systems, *analysis* and *verification* techniques for model-driven development methods and languages still have to reach a similar level of maturity as those for text-based imperative programming languages traditionally used in the development of safety-critical embedded systems. In this thesis, we present *an information flow analysis* method for discrete embedded control system models, which has the potential to identify possible violations of both safety requirements and security policies by analyzing where and under which conditions information travels through a model. The main challenges such an information flow analysis faces are to (1) consider the specific semantics of the modeling languages, which heavily rely on concurrency and a complex notion of timing, and (2) relate the strongly different semantics of signal-flow-oriented and state-machine-based components, which comprise embedded control system models.

Our major contribution is twofold: First, we provide an information flow analysis for the signal-flow-oriented components of an embedded control system model. The main idea of this analysis is that we only extract that information from an existing model which is required to analyze information flow in respect to both its timing and functionality. To this end, our technique captures *timed path conditions*, i.e., the precise control, data and timing conditions under which information flow is enabled as well as when and how these conditions are triggered. Second, we relate the inherently different semantics of the signal-flow-oriented and the statemachine-based components. To this end, we first translate the state-machine-based controller into a formally verifiable representation and, second, combine this representation with *condition observer automata* which we generate from the timed path conditions extracted in the first step of our method. This enables us to use the well-established technique of model checking to identify precisely the behavior that leads to the execution of information flow paths under analysis.

To show the practical applicability of our approach, we have implemented it as a fully automatic and modular framework for MATLAB *Simulink/Stateflow* and Modelica, two widely used languages from the domain of embedded control systems, and applied our information flow analysis to two industrial case studies. In these case studies, we are able to verify *integrity* by checking that no information flow is possible from a non-critical to a critical component.

#### Zusammenfassung

Im sicherheitskritischen Bereich unterliegen eingebettete Systeme strengen Anforderungen an Ausfall- sowie Datensicherheit. Zugleich ist die Systemkomplexität in den vergangenen Jahren in allen Anwendungsbereichen stark gestiegen. Um diesem Anstieg zu begegnen, nutzen Hersteller modellgetriebene Entwicklungsansätze. Während Ansätze dieser Art bereits erfolgreich dazu genutzt werden, komplexe, miteinander verbundene Systeme zu *entwickeln*, haben Ansätze zur *Analyse* und *Verifikation* dieser Systeme noch nicht den Stand erreicht, den ähnliche Methoden für imperative Programmiersprachen aufweisen. In dieser Arbeit stellen wir eine Informationsflussanalyse für diskrete eingebettete Kontrollsystemmodelle vor, die es ermöglicht, Verletzungen von Ausfall- sowie Datensicherheitsanforderungen zu erkennen. Unsere Analyse verfolgt, wie und unter welchen Bedingungen Informationen durch ein Modell fließen. Die Herausforderungen in der Entwicklung einer solchen Analyse liegen in (1) der Berücksichtigung der spezifischen Semantik der Modellierungssprachen, welche auf komplexen zeitlichen Abhängigkeiten und Parallelität basieren, und (2) der Verbindung der stark heterogenen Semantiken der signalflussorientierten und jener auf Zustandsautomaten basierenden Komponenten, aus denen Kontrollsystemmodelle aufgebaut sind.

Die vorliegende Arbeit leistet in diesem Gebiet zwei Beiträge. Zum einen eine Informationsflussanalyse für die signalflussorientierten Komponenten eines Kontrollsystemmodells. Diese Analyse basiert auf der Idee, nur diejenigen Informationen eines Modells zu extrahieren, die für die Analyse des Informationsflusses hinsichtlich des Zeitverhaltens und der Funktionalität des Modells relevant sind. Um dies zu ermöglichen, erfasst unser Ansatz *timed path conditions*, das heißt, diejenigen Bedingungen, die präzise das Kontroll-, Zeit-, und Datenverhalten abbilden, unter denen Informationsfluss stattfindet. Zum anderen schafft unsere Arbeit eine Verbindung zwischen den stark heterogenen Semantiken der signalflussorientierten und den auf Zustandsautomaten basierenden Komponenten. Unser Ansatz ermöglicht dies durch eine Übersetzung der Automaten in eine formal verifizierbare Darstellung, und die Kombination dieser Darstellung mit *condition observer automata*, welche wir aus den im ersten Schritt extrahierten *timed path conditions* generieren. Diese Verbindung der Semantiken ermöglicht uns, eine wohlfundierte Technik wie model checking zu nutzen, um genau das Verhalten des Zustandsautomaten zu identifizieren, welches zur Ausführung eines Informationsflusspfades führt.

Um die Anwendbarkeit unseres Ansatzes unter Beweis zu stellen, präsentieren wir außerdem eine vollautomatische und modular aufgebaute Implementierung für MATLAB Simulink/Stateflow und Modelica, zwei im Bereich sicherheitskritischer eingebetteter Software weit verbreitete Sprachen. Mithilfe dieser Implementierung konnten wir unseren Ansatz zur Informationsflussanalyse auf zwei Fallstudien aus dem industriellen Bereich anwenden. In beiden Fallstudien waren wir in der Lage, die Integrität kritischer Berechnungen sicherzustellen, indem wir Informationsfluss zwischen nicht-kritischen und sicherheitskritischen Komponenten ausschließen konnten.

#### Danksagung

Diese Arbeit wäre ohne die Anregungen und die Unterstützung einer Vielzahl von Menschen nicht zustande gekommen.

Zuallererst möchte ich Prof. Dr. Sabine Glesner für ihre jahrelange Unterstützung meiner Arbeit sowie für die vielen Gespräche und Anregungen danken. Sie hat mir nicht nur einen wunderbaren Rahmen für meine Promotion am Fachgebiet *Software and Embedded Systems Engineering* (SESE) der Technischen Universität Berlin geboten, sondern mich auch dazu ermutigt, mit meiner Arbeit in die Welt zu treten, sie an anderen Orten vorzustellen und dadurch voranzubringen. Dank ihrer Vermittlung konnte ich meine Arbeit auch an den Lehrstühlen von Prof. Dr.-Ing. Christian Hammer und Prof. Dr.-Ing. Frank Slomka vorstellen. Beide haben meine Arbeit im Anschluss daran als Gutachter betreut und begleitet. Die hilfreichen Anregungen und Hinweise beider haben diese Arbeit enorm verbessert und die Offenheit und Gründlichkeit beider im Umgang mit meiner Arbeit haben mich beeindruckt und geehrt.

Prof. Glesner hat mich auch darin unterstützt, sechs Monate als Visiting Research Collaborator in der Gruppe von Prof. Sharad Malik an der Princeton University zu verbringen. Die Gespräche und die gemeinsame Arbeit mit ihm, Prof. Aarti Gupta und Zhixing Xu haben meine Forschung extrem bereichert und mir neue Perspektiven eröffnet. Für Prof. Glesners Unterstützung in Planung und Durchführung dieser unvergesslichen Zeit bin ich ihr – sowie dem Deutschen Akademischen Austauschdienst – sehr dankbar.

Sehr dankbar bin ich auch für die Unterstützung durch das Bundesministerium für Bildung und Forschung (BMBF) sowie durch unseren Industriepartner Model Engineering Solutions GmbH (MES), die meine Forschungsarbeit im Rahmen der Projekte Change Impact Analyses for Software Models (CISMo) und Effective Complexity of Software Models (ECoSMo) förderten. Auf Seiten von MES war Dr. Heiko Dörr zu jeder Zeit ein sehr hilfsbereiter und engagierter Gesprächspartner für mich, der meine Forschung nicht nur durch das Zurverfügungstellen zahlreicher Anwendungsbeispiele maßgeblich vorangebracht und motiviert hat.

Der Softwareprototyp, der im Rahmen meiner Arbeit und Forschung entstanden ist, hat von der langjährigen Mitarbeit meiner studentischen Hilfskräfte Moritz Lummerzheim, Feras Fattohi und Umar Ahmad unheimlich profitiert. Ich bin sehr froh, dass ihr mir geholfen habt, meine Ideen Realität werden zu lassen.

Diese Arbeit wäre ohne die kontinuierliche Ermutigung, die klugen Kommentare und nicht zuletzt die immer tatkräftige Unterstützung von Prof. Dr.-Ing. Paula Herber und Dr.-Ing. Thomas Göthel nicht zustande gekommen. Sie haben diese Arbeit maßgeblich geprägt und vom ersten Satz bis zur letzten Seite begleitet. Dass die beiden nicht nur bewunderte Postdocs blieben, sondern mir auch zu Freunden wurden, ist ein großes Glück. Dafür, aber auch für ihre unermüdliche Unterstützung und ihr Interesse an meiner Arbeit werde ich immer dankbar sein. Meine Promotionszeit wäre nicht die gleiche gewesen ohne meine Kolleginnen und Kollegen am Fachgebiet SESE. Die Gespräche während all der gemeinsamen Kaffeepausen und Mittagessen haben die Arbeit an meiner Dissertation nicht nur sehr viel schöner, sondern auch besser gemacht. Ganz besonders froh und dankbar bin ich über die Freundschaften, die sich mit Dr.-Ing. Sebastian Schlesinger und Dr. Nils Berg entwickelt haben. Die Möglichkeit, mein Leid mit euch zu teilen, hat mir auch über Momente hinweggeholfen, in denen ich sicher war, diese Arbeit nie zu Ende bringen zu können.

Meinen Eltern danke ich für ihre große Unterstützung – nicht nur während meiner Promotionszeit, sondern auch in all den Jahren davor. Sie haben mich früh dazu ermutigt, meinen eigenen Weg zu gehen, haben mir an jedem Ort, an den es mich auf diesem Weg verschlagen hat, geholfen, ein Zuhause aufzubauen, und mir nicht zuletzt sehr früh ermöglicht, mich an meinem eigenen 486er auszuprobieren.

Mein innigster Dank gilt meiner Frau Laetitia Lenel. Ich bin nicht in der Lage, ihr genug für ihr Vertrauen in mich und meine Fähigkeiten zu danken, für unsere Gespräche und Diskussionen, ihre unendlich klugen Kommentare und Einsichten, sowie für ihre unermüdliche Ermunterung gegen meinen erbitterten Widerstand. Das gemeinsame Leben mit ihr und unserer wunderbaren Tochter Mathilda hat mir erst die Kraft, die Ruhe und den Mut gegeben, diese Arbeit fertigzustellen.

# Contents

| 1 | Intro | troduction |                                                             | 1  |

|---|-------|------------|-------------------------------------------------------------|----|

| 2 | Bac   | kgrou      | nd                                                          | 7  |

|   | 2.1   | Model-     | -Driven Development of Embedded Software                    | 7  |

|   |       | 2.1.1      | Model-Driven Development in Software Development Guidelines | 8  |

|   | 2.2   | Signal-    | Flow-Oriented Modeling Languages                            | 9  |

|   |       | 2.2.1      | Signal-Flow Graphs                                          | 10 |

|   |       | 2.2.2      | Syntax of Signal-Flow-Oriented Modeling Languages           | 10 |

|   |       | 2.2.3      | MATLAB Simulink/Stateflow                                   | 12 |

|   |       | 2.2.4      | Modelica                                                    | 17 |

|   | 2.3   | Inform     | ation Flow Analysis                                         | 20 |

|   |       | 2.3.1      | Types of Information Flow                                   | 20 |

|   |       | 2.3.2      | The Lattice Model of Secure Information Flow                | 22 |

|   |       | 2.3.3      | Information Flow Control                                    | 23 |

|   |       | 2.3.4      | Non-Interference                                            | 25 |

|   |       | 2.3.5      | Path Conditions                                             | 25 |

|   | 2.4   | Constr     | aint Logic Programming                                      | 27 |

|   | 2.5   | Model      | Checking                                                    | 29 |

|   |       | 2.5.1      | UPPAAL Timed Automata                                       | 30 |

|   | 2.6   | Summa      | ary                                                         | 31 |

| 3 | Rela  | ated W     | 'ork                                                        | 33 |

|   | 3.1   | Inform     | ation Flow Analyses of Sequential Programs                  | 33 |

|   | 3.2   | Inform     | ation Flow Analyses of Synchronous Systems                  | 34 |

|   | 3.3   | Inform     | ation Flow Analyses of Control System Models                | 35 |

|   | 3.4   | Formal     | Analyses of Signal-Flow-Oriented Modeling Languages         | 37 |

|   |       |            |                                                             |    |

|   |      | 3.4.1 Approaches Based on Model Checking Intermediate Languages 3      | 87         |

|---|------|------------------------------------------------------------------------|------------|

|   |      | 3.4.2 Approaches Built into Modeling Environments                      | <b>9</b>   |

|   |      | 3.4.3 Summary                                                          | <u>8</u> 9 |

|   | 3.5  | Formal Analyses of State-Machine-Based Models 4                        | 0          |

|   | 3.6  | Summary                                                                | 11         |

| 4 | Info | rmation Flow Analysis Approach 4                                       | 3          |

|   | 4.1  | Motivating Example                                                     | -5         |

|   | 4.2  | Model Structure         4                                              | ŀ7         |

|   | 4.3  | Assumptions                                                            | 19         |

|   | 4.4  | Information Flow Analysis of Discrete Embedded Control System Models 5 | 0          |

|   |      | 4.4.1 Information Flow Analysis of Signal-Flow-Oriented Models 5       | 51         |

|   |      | 4.4.2 Information Flow Analysis of Heterogeneous Models                | 52         |

|   |      | 4.4.3 Automation of our Information Flow Analysis Approach 5           | 53         |

|   | 4.5  | Summary 5                                                              | 54         |

| 5 | Info | rmation Flow Analysis of Signal-Flow-Oriented Models 5                 | 5          |

|   | 5.1  | Approach                                                               | 55         |

|   | 5.2  | Intermediate Model Representation 5                                    | 57         |

|   | 5.3  | Finding Paths of Interest    5                                         | 57         |

|   | 5.4  | Identifying Timing Dependencies                                        | 59         |

|   | 5.5  | Extracting Local Timed Path Conditions                                 | 54         |

|   | 5.6  | Evaluation of Control Signals    6                                     | 57         |

|   |      | 5.6.1 Identifying Control Paths                                        | 59         |

|   |      | 5.6.2 Backwards Propagation of Non-Cyclical Control Signals 7          | 0          |

|   |      | 5.6.3 Analysis of Cyclical Control Paths                               | '3         |

|   |      | 5.6.4 Composition of Global Timed Path Conditions                      | 6          |

|   | 5.7  | Translating and Solving Path Conditions    7                           | 78         |

|   | 5.8  | Summary                                                                | 32         |

| 6 | Info | rmation Flow Analysis of Heterogeneous Models 8                        | 3          |

|   | 6.1  | Approach                                                               | 33         |

|   | 6.2  | Relating the Timing Behavior of Heterogeneous Components 8             | 6          |

|   | 6.3  | Translating State-Machine-Based Controllers to Timed Automata 8        | 37         |

|   |      | 6.3.1 Generalization to Arbitrary Inputs                               | 88         |

|   | 6.4  | Translating Timed Path Conditions to Timed Automata                    | 0          |

|                     | 6.5                      | Reachability Analysis                                                      | 94  |

|---------------------|--------------------------|----------------------------------------------------------------------------|-----|

|                     | 6.6                      | Summary                                                                    | 96  |

| 7                   | Eva                      | luation                                                                    | 97  |

| •                   | 7.1                      | Implementation                                                             | 97  |

|                     | ,.1                      | 7.1.1 Components                                                           | 98  |

|                     |                          | 7.1.2 Optimizations                                                        | 100 |

|                     | 7.2                      | Case Study 1: Shared Automotive Communication Infrastructure               | 102 |

|                     | 7.3                      | Case Study 2: Shared Communication Infrastructure using Error Compensation | 108 |

|                     | 7.4                      | Analysis Complexity                                                        | 110 |

|                     | 7.5                      | Summary                                                                    | 113 |

| 8                   | Cor                      | nclusion                                                                   | 115 |

| 0                   | 8.1                      | Results                                                                    | 115 |

|                     | 8.2                      | Outlook                                                                    | 117 |

|                     | 0.2                      | Outlook                                                                    | 11/ |

| Li                  | st of                    | Definitions                                                                | 121 |

| Li                  | st of                    | Figures                                                                    | 123 |

|                     |                          |                                                                            |     |

| LI                  | List of Tables 12        |                                                                            |     |

| List of Listings 12 |                          |                                                                            | 127 |

| Li                  | List of Abbreviations 12 |                                                                            |     |

| Bi                  | blioc                    | Iraphy                                                                     | 131 |

|                     |                          |                                                                            |     |

| Ap                  | •                        | dix A Examples                                                             | 151 |

|                     | A.1                      | Information Flow Analysis of Signal-Flow-Oriented Models                   |     |

|                     |                          | A.1.1 Example 1: Unconditional Flow                                        |     |

|                     |                          | A.1.2 Example 2: Conditional Path Execution                                |     |

|                     |                          | A.1.3 Example 3: Complex Path Execution through Multiple Switches          | 156 |

| Ap                  | open                     | dix B Stateflow Semantics                                                  | 161 |

| -                   | В.1                      | State Transformation                                                       | 162 |

|                     | B.2                      | Transition Transformation                                                  | 162 |

|                     | B.3                      | Simulation Time Representation                                             | 163 |

# Appendix C Translating Discrete Control System Models to Mathematica165

| C.1 | Representation of Signal-Flow-Oriented Block Functionalities in Mathematica .         | 166 |

|-----|---------------------------------------------------------------------------------------|-----|

| C.2 | Identifying Non-Recursive Solutions to Cyclical Control Signals                       | 167 |

| C.3 | Calculating the Validity of Timed Path Conditions on Cyclical Control Paths $\ . \ .$ | 168 |

| C.4 | Summary                                                                               | 169 |

# Introduction

Embedded systems are shifting from unconnected to increasingly interconnected functionality. The connection of these *cyber-physical systems* to the internet and to each other poses severe threats to confidentiality, integrity and availability. In 2015, this was prominently demonstrated by software security researchers Miller and Valasek as they remotely exploited a vulnerability in the internet-connected entertainment system of a Jeep Cherokee, gaining control over vital functions such as acceleration, brakes and steering [Miller and Valasek 2015]. The attack was made possible by a combination of two factors: (1) the existence of the on-board *Controller Area Network* (CAN) bus [ISO 1993] which connects most major components in the car in order for them to receive commands and exchange information, and (2) a range of common vulnerabilities in the internetconnected entertainment system of the car [Koscher et al. 2010b; Checkoway et al. 2011; Mazloom et al. 2016; Choi and Jin 2019].

For safety-critical systems, correct operation at all times is of the utmost importance. To protect cars from attacks, i.e., to protect the safety-critical components from remote interference, every component in itself needs to adhere to strict security standards. Furthermore, as all modules are able to communicate with each other freely, thus, there is a risk of security violations as well as component failures traveling through the system without constraint. To overcome this problem, the state-of-the-art safety standard defined by the *International Organization for Standardization* (ISO) recommends partitioning of the software [ISO 2009]. The aim of this method is to safely break down the system into smaller parts in order for them to be analyzable individually without having to consider the complete system. The most basic partitioning method is to completely refrain from utilizing interconnected systems. If components are not able to communicate with each other, security violations and safety failures never travel between them. Modern

embedded systems, however, rely heavily on interconnections. Thus, more advanced analysis methods for connected systems are required, which are able to safely identify the flow of information between components in heavily interconnected systems.

Especially in the automotive domain, the complexity of embedded software systems has increased dramatically in the past. While in 2007, the binary code of the software in an upper-class vehicle amounted to approximately 65 MB, recent generations contain more than 1 GB of binary code [Pretschner et al. 2007; Braun et al. 2014]. Developers have therefore shifted towards MDD [Hailpern and Tarr 2006; Navet and Simonot-Lion 2009], which enables system design on a high level of abstraction and early simulation. Additionally, it allows for the automated generation of implementation-specific software, a highly error-prone process when performed manually. While model-driven development enables a better understanding of complex systems, further technique are needed to prove adherence to safety and security standards [ISO 2009]. However, due to the strongly differing semantics of models and code, classic analysis techniques are not applicable to MDD [Tanković et al. 2012]. It is therefore imperative to develop novel analysis approaches that are able to perform, e.g., information flow analysis or security policy compliance checks directly on the models that are used as the main development artifacts.

The challenges we face when developing novel static analysis techniques for modelbased development can be summarized as follows: (1) The semantics of the most widely-used modeling languages for discrete embedded controllers are based on the concept of signal-flow graphs (SFGs), which are a common abstraction used to model physical systems as well as their controllers. They naturally express data-intensive computations with local evaluation of data, as commonly found in control systems [Bonchi et al. 2017a]. This signal-flow semantics [Misra 2004] introduces characteristics not present in the semantics of traditional imperative programming languages which are utilized in the domain of safety-critical software. One of the strongest differences is the utilization of time-dependent, stateful modeling elements, extending the execution semantics of the model by a complex notion of timing. Additionally, due to the signal-flow nature of the models, they inherently utilize concurrency, further increasing the complexity of analyses of their execution behavior. (2) Modeling languages allow the developer to utilize development patterns with strongly differing semantics in the same model. To combine, e.g., data manipulation on signals with complex control flow mechanics, industrially used modeling languages, such as MATLAB Simulink/Stateflow and Modelica,

allow for the integration of state machines into signal-flow models. Thus, new analysis techniques that support the simultaneous extraction of information from both modeling styles are highly desirable.

The aim of this thesis is to establish a framework for the automated extraction and analysis of information flow in discrete embedded control system models. In the following, we list the criteria our approach should fulfill:

- 1. **Signal-Flow Semantics:** The proposed methodolody must be able to cope with the characteristics specific to discrete embedded control system models, i.e., with complex timing behavior as well as the concurrency inherent to these models.

- 2. **Combined Analysis:** The proposed approach has to be able to extract information flow from models that combine signal-flow and state-machine-based components.

- 3. Language Support: We require our methodology to be applicable to industrially used languages for the model-based design of discrete embedded control systems. Additionally, our approach should cover a broad range of modeling elements frequently used in the design of such systems and should facilitate easy extension of the set of supported elements.

- 4. **Automation:** To be integrated into existing quality assurance processes for MDD, the proposed methodology should be applicable fully automatically. This means that the analysis must not require annotations or user input.

- 5. **Applicability:** Finally, we require our methodology to have acceptable analysis effort. This should be demonstrated by applying our novel analysis technique to industrial case studies from the automotive domain.

To meet these criteria, we propose a novel methodology that provides a method to identify and analyze information flow relations in discrete embedded control system models containing complex control flow and timing behavior. To demonstrate the industrial applicability of our approach, we have fully implemented our methodology for two of the most widely-used modeling languages for the development of embedded controller software: MATLAB Simulink/Stateflow by The MathWorks and Modelica by the Modelica Association [Schroeder et al. 2015; Sutherland et al. 2016]. Both languages implement a graphical development front-end to develop models employing signal-flow semantics. As our approach targets the timing behavior of signal-flow-based semantics, we are confident that it can be applied to further simulation languages with similar semantics. To facilitate the extensibility of our approach, we have implemented it as a modular framework.

The main contributions of this thesis are:

- 1. We have developed an **information flow analysis approach for MATLAB Simulink models**. Our method adapts the concept of path conditions to the domain of model-based development, using MATLAB Simulink as a modeling language widelyused in the development of discrete embedded system controllers. Our extension, which we call *timed path conditions* (TPCs), is able to express the data as well as the time-dependent execution behavior of information flow paths through a signal-flow-oriented model. To identify non-interference between model elements, we use timed path conditions to formulate a *constraint satisfaction problem* and solve it using a constraint solver. If no solution can be found, we have shown non-interference for the model elements under analysis.

- 2. As industrial embedded system models most often contain complex control logic, our technique supports the analysis of information flow in combined MATLAB Simulink/Stateflow models consisting of signal-flow-oriented components modeled in Simulink and state-machine-based controllers implemented using Stateflow. To enable a combined analysis, we make use of an existing technique to translate one of the most common modeling languages for embedded controllers, Stateflow, into formally well-defined UPPAAL *timed automata*. Using this translation, we merge the two strongly differing execution semantics of embedded system controllers developed in MATLAB Simulink/Stateflow and are able to identify non-interference on paths through such combined models.

- 3. To demonstrate the applicability of our method to other modeling languages that are based on signal-flow graphs, we have developed an **information flow analysis for discrete embedded control systems developed using Modelica**.

- 4. We have developed a **fully automatic framework to analyze the information flow in discrete embedded systems**. Using this framework, we show that the extraction of *timed path conditions* from the signal-flow-oriented model components as well as the translation of the state-machine-based components to UPPAAL timed automata can be performed fully automatically.

5. The **experimental results** that we have obtained using our methodology show that the extraction and analysis of information flow from synthetic as well as **industrial case studies** from the automotive domain can be performed with **acceptable effort**.

We have published our work as follows: In Mikulcak et al. [2017], we have introduced the concept of timed path conditions and have shown how they can be utilized to identify information flow in a MATLAB Simulink model. In Mikulcak et al. [2016], we have extended our information flow analysis of MATLAB Simulink models to additionally support the extraction of flow data in the face of complex control behavior modeled in Stateflow. In Mikulcak et al. [2018], we have introduced a fully automatic solution based on a translation to UPPAAL timed automata that does not pose any restrictions on the controller implementation. Further, in this work we have presented experimental results from an industrial case study provided by our partners from the automotive industry to demonstrate the practical applicability of our approach. Finally, in [Mikulcak et al. 2019], we have published a detailed explanation of our method and its components.

This thesis is structured as follows: In Chapter 2, we introduce a number of concepts that are necessary for the understanding of this thesis. In Chapter 3, we provide a discussion of related work. Chapter 4 presents an overview of our system to identify information flow in discretely-timed embedded control system models and discusses requirements that models have to fulfill in order to be analyzable by our system. Chapter 5 and 6 explain the details of our system. In Chapter 5, we present our concept of timed path conditions and provide a detailed description of our technique to infer non-interference between arbitrary model elements using constraint solving. Chapter 6 presents our technique to extract information flow from models containing both signal-flow-oriented and state-machine-based components. In Chapter 7, we provide details on the implementation of our approach as a fully automatic and extensible framework, present case studies from the automotive domain and discuss experimental results. Chapter 8 closes this thesis with a conclusion and a discussion of future work.

# **2** Background

In this chapter, we provide preliminaries that are the foundation of this thesis. First, we give a brief introduction to the domain of model-driven development. Subsequently, we present signal-flow-based modeling languages, namely MATLAB Simulink/Stateflow and Modelica, after which we introduce the concept of information flow analysis. We close with an introduction to constraint satisfaction problems and their solvers as well as to system verification using model checking.

## 2.1 Model-Driven Development of Embedded Software

Models provide abstractions by forming a representation of the essential components and functionalities of a system. Consequently, models are less complex and they are easier to grasp, maintain, and debug, not only by the model developers, but also by specialists from other domains involved in the development process, e.g., electrical or mechanical engineers. The three major levels of abstraction commonly utilized in model-driven development are:

- *Computation-Independent Model* (CIM) The CIM defines what the system is expected to do while hiding all information-technology-related specifications, such as the algorithmic implementation [Truyen 2006].

- *Platform-Independent Model* (PIM) The PIM captures the detailed functionality of the system, defines algorithmic details as well as timing behavior.

- *Platform-Specific Model* (PSM) The PSM contains enough details about the functionality of the system as well as about the target platform to produce an implementation that can be deployed.

As part of the MDD approach standard defined in Kleppe et al. [2003], a PIM, combined with a *platform model*, contains sufficient information about the functionality of a system to enable the *automatic* generation of a PSM, i.e., enabling the *automated* generation of non-essential implementation-specific details.

In this thesis, we focus on *model-centric* approaches, as this style is the one most adopted in industrial software development processes for safety-critical systems [Albers et al. 2006; Frevert et al. 2006]. *Model-centric techniquees* describe a development style in which the development is solely focused on models. Models form the main development artifact and need to contain sufficient detail to, given a platform model, enable the automatic generation of a system implementation. This technique eliminates the need to feed back source code changes into the model, but introduces the necessity to utilize modeling languages expressive enough to capture all required details of the functionality as well as the timing of the system. However, as a wide range of modeling languages supports the design of systems on various levels of abstraction, the model focus can be maintained.

#### 2.1.1 Model-Driven Development in Software Development Guidelines

Due to the advantages of model-driven development and automatic generation of code from abstract models, the utilization of MDD techniques is recommended as *state of the art* by international standards for the design of safety-critical electronic systems. While IEC [2010] as an overarching standard for general safety-related electronic systems defines generic requirements for structuring and testing of software systems, ISO [2009] as the standard for automotive systems requires developers to utilize MDD-based methods to manage the complexity of the developed software and to increase maintainability [Bell 2006; ISO 2009; IEC 2010].

#### Software Safety Risk Classification Schemes

To define a common basis for comparison, IEC [2010] defines *Safety Integrity Levels* (SILs) that help developers in determining the necessary measures that need to be taken to ensure the correct operation of software systems. According to the dangers arising from a possible failure of a component, one of four SILs is assigned, ranging from the lowest level SIL 1 to the highest SIL 4. The higher the SIL assigned to a component, the more rigorous the testing and verification process needs to be in the development phase until a tolerable level of failure probability is reached [Bell 2006; IEC 2010]. ISO [2009]

builds on this concept by introducing *Automotive Safety Integrity Levels* (ASILs), ranging from the lowest ASIL A to the highest ASIL D for safety-critical components with the lowest to the highest automotive hazard. Additionally, a level *Quality Management* (QM) is introduced, which defines a base level for quality management that is necessary to be administered. In contrast to SILs, ASILs are not defined quantitatively, but qualitatively, i.e., a component level is determined via:

Risk = Expected severity in case of failure × Probability of failure, or ASIL = Severity × Exposure × Controllability

For every level and every step in the development process, ISO [ibid.] defines mechanisms required to be applied to mitigate the respective risk of failure of each component and the severity in case of such a failure. The highest levels, ASIL C and D, for example, require the use of unambiguous graphical representations of the software as well as the utilization of formal analysis techniques to gather information about data and control flow through the software. In addition to the assignment of an ASIL to each individual component, a connection between multiple components, i.e., the possibility for information flow between them, infers the requirement to develop and maintain all components on the level of the component with the highest ASIL. Only if a safe partitioning between components can be shown, ISO [ibid.] allows this requirement to be relaxed.

## 2.2 Signal-Flow-Oriented Modeling Languages

The largest number of embedded systems and internet-connected cyber physical systems are *reactive systems* [Berry 1989; Sander 2003]. Contrary to *interactive systems*, such as browsers or word processors, these reactive systems continuously react to their environment at the speed of the environment. In addition to the aspect of reactivity, embedded systems, such as, e.g., automotive control systems, are required to continuously perform computations on numerous incoming signals concurrently. In the design of safety-critical embedded systems, the *signal-flow-oriented* programming paradigm [Misra 2004; Kuo and Golnaraghi 2009], which naturally combines both aspects, has become the main development style. In the following, we first give a short introduction to the basic concept of signal-flow graphs. Subsequently, we present two modeling languages based on signal-flow-oriented semantics, MATLAB Simulink/Stateflow and Modelica, which we use as

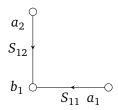

Figure 2.1: Signal-flow graph for Equation (2.1)

example languages in this thesis to present our information flow analysis method. Both languages are widely used in the domain of safety-critical systems and offer graph-based, signal-flow-oriented modeling of software systems.

#### 2.2.1 Signal-Flow Graphs

SFGs are graphical representations of signal processing algorithms that display the relationship between variables in sets of linear algebraic equations and consist of *nodes* interconnected by directed branches [Mason 1953; Abrahams 1965]. The nodes represent variables or parameters of the differential equations, the branches act as coefficients connecting the variables. Figure 2.1 shows an example of an SFG that implements the equation

$$b_1 = S_{11}a_1 + S_{12}a_2 \tag{2.1}$$

The corresponding SFG is comprised of three nodes  $(b_1, a_1, a_2)$  and two branches. The arrows on the two branches are directed from the *causes*  $a_1$  and  $a_2$  towards the *effect*  $b_1$ , modified by the coefficients  $S_{11}$  and  $S_{12}$ . As is shown there, the operations performed at nodes and branches are implicit: a multiplication with the corresponding coefficients on the branches, and a summing operation on a unification of multiple branches at a node.

#### 2.2.2 Syntax of Signal-Flow-Oriented Modeling Languages

Signal-flow-oriented modeling languages employ *blocks* which are connected using *signals*. Additionally, each block and signal is assigned a set of *parameters*. When relating a signal-flow-oriented *program* to traditional text-based programming languages, the signals connecting blocks are variables. The values of these variables are determined by the

blocks they are connected to, which represent functions defined over a continuum, i.e., the output value of a block is not only dependent on its current inputs but also on an internal state [Lee and Neuendorffer 2005].

A signal-flow-oriented model is defined, analogously to Boström and Morel [2007], Boström et al. [2007], and Zander-Nowicka [2009], as a tuple

$$\mathcal{M} = (B, root, sub_h, P, rlt, sig, subi, subo, C)$$

, where :

- *B* represents the set of blocks in the system. Depending on the functionality of a block, they are part of one of the following categories:  $B^s$  for subsystem blocks,  $B^i$  for inports to a subsystem,  $B^o$  for subsystem outports, merge blocks  $B^m$ , blocks that contain an internal state  $B^{\text{mem}}$ , and basic, or *direct feed-through*, blocks  $B^b$ . Additionally, every subsystem is either *virtual*,  $B^{vs}$  or *non-virtual*,  $B^{ns}$ , such that  $B^s = B^{vs} \cup B^{ns}$ . Virtual blocks, such as inports to a subsystem or subsystems themselves, do not influence the simulation behavior of a signal-flow-oriented model, while nonvirtual blocks do. Virtual blocks are purely used to structure the model and do not influence the behavioral semantics;

- $root \in B^{vs}$  represents the root subsystem;

- $sub_h : B \to B^s$  defines a function representing the subsystem hierarchy of the system. For every block  $b \in B$ , it returns the subsystem block  $b^s \in B^s$  that it is structured into;

- *P* is the set of ports that input,  $P^i \subseteq P$ , and output,  $P^o \subseteq P$ , data to and from blocks,  $P^i \cup P^o = P$ ;

- $rlt: P^i \rightarrow P^o$  is the function that maps every port to its corresponding block;

- $sig: P^o \rightarrow P^i$  is a relation that maps every outgoing port to the in-going port it is connected to via a signal line;

- $sub_i: B^s \to P \to \rho(P^i)$  is a partial function that maps the virtual inports of a subsystem to the non-virtual block driving it;

- $sub_o: B^s \to P \to \rho(P^i)$  describes a partial function that maps the virtual outports of a subsystem to the non-virtual block that it drives;

- C is the set of simulation parameters of the model.

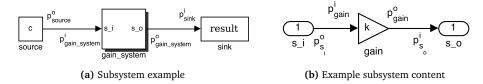

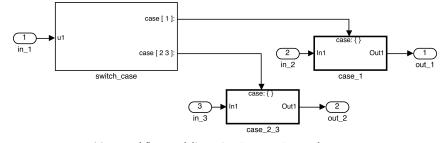

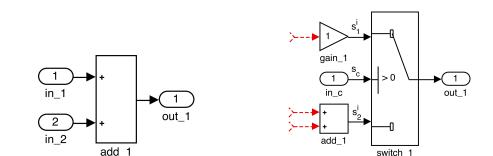

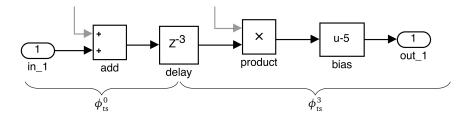

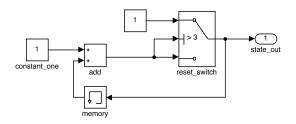

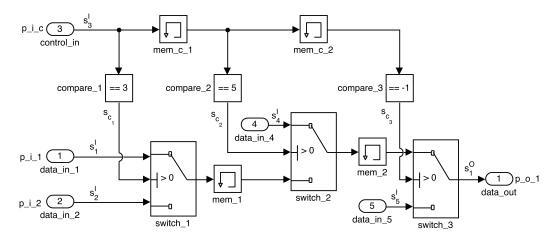

Figure 2.2: Simulink example model.

#### 2.2.3 MATLAB Simulink/Stateflow

MATLAB by The MathWorks [The MathWorks 2017b] is a multi-purpose numerical computing environment. In addition to this core functionality, MATLAB offers functionalities in the areas of, among others, data analysis and visualization, signal and image processing, financial modeling, or computational biology.

#### Simulink

Simulink is an add-on to MATLAB that enables multi-domain modeling and simulation of reactive control systems, offering an interactive graphical development environment for the model-based development of dynamic control systems. Simulink employs the syntax presented in Section 2.2.2.

Note that on the relations and functions defined in Section 2.2.2, there are several restrictions in order for a model to be considered a valid Simulink model. These restrict, e.g., the subsystem hierarchy and the signal connections over subsystem boundaries. In this thesis, we restrict our analysis to only support valid Simulink models, i.e., models that can be drawn using the graphical development environment and subsequently simulated. Invalid models that can be drawn but not simulated contain, e.g., unconnected signal lines.

Consider the example shown in Figure 2.2. The blocks are defined by

$B \stackrel{\wedge}{=} \{\text{source, gain_system}, s_i, \text{gain}, s_o, \text{sink}\}.$

The set of subsystems is given as

$$B^{\nu s} \stackrel{\wedge}{=} \{\text{gain system}, root\}, \text{ and } B^{ns} \stackrel{\wedge}{=} \emptyset.$$

with the hierarchy definition

$$sub_h \stackrel{\wedge}{=} \{(gain, gain_system), (gain_system, root), (source, root), \dots\}$$

.

When displaying Simulink diagrams, port names are usually omitted. Here, they are given as

$$P = \left\{ p_{\text{source}}^{o}, p_{\text{sink}}^{i}, p_{\text{gain_system}}^{o}, p_{\text{gain_system}}^{o}, \dots \right\}$$

The function describing which port is part of which block is given as:

$$blk \stackrel{\wedge}{=} \left\{ (p_{\text{source}}^o, \text{source}), (p_{\text{gain}}^i, \text{gain}), (p_{\text{gain}}^o, \text{gain}), (p_{\text{gain}\_\text{system}}^i, \text{gain}\_\text{subsystem}), \dots \right\}.$$

The connections between the ports is defined as

$$sig \stackrel{\wedge}{=} \left\{ (p_{gain\_system}^{i}, p_{source}^{o}), (p_{gain}^{i}, p_{s_{i}}^{o}), \dots \right\}$$

The relations describing how ports in inports and outports correspond to ports of subsystems are given by  $sub_i$  and  $sub_o$ . The inport of the subsystem is related to the outport of the in-block:

$$sub_i \stackrel{\wedge}{=} \left\{ \left( \text{gain\_subsystem}, p_{s_i}^o, \{ p_{\text{gain\_system}}^i \} \right), \dots \right\}.$$

The definition of the outputs of the subsystem is similar:

$$sub_o \stackrel{\wedge}{=} \left\{ \left( \text{gain\_subsystem}, p_{\text{gain\_system}}^o, \{p_{s_o}^i\} \right), \dots \right\}.$$

**Signal Flow.** Signal flow in Simulink is modeled using signals, or *signal lines*, connecting blocks. Signals carry the current value on the outports of blocks to inports of other blocks. Signals in Simulink are able to carry more than a single primitive value. According to the design of the model, signals carry either scalars, vectors, matrices, or even hierarchies of values. The precise type is not set statically, but is inferred by the underlying simulator at run-time according to the blocks driving the signals.

Signal flow through hierarchical Simulink subsystems is modeled using dedicated *vir*tual blocks. While these blocks of types InPort and OutPort do not modify the signals connected to them, they serve as connectors in the model which connect levels in the model hierarchy to each other. Signals leaving a subsystem are connected to OutPorts, which consequently do not have out-going ports. For each OutPort block, an out-going port is added to the subsystem, which in turn is connected via an InPort to the surrounding model environment. Figure 2.2b shows one InPort and OutPort, respectively, connecting the subsystem to its parent hierarchy level.

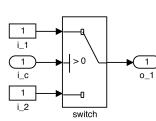

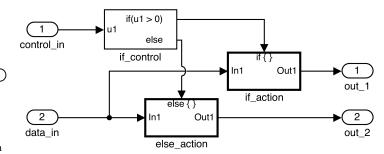

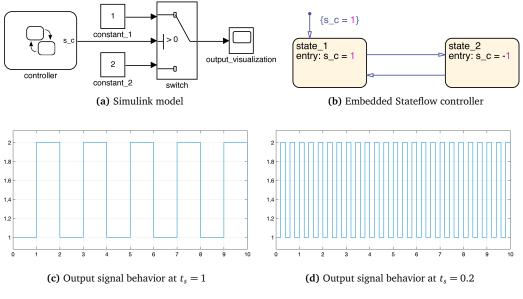

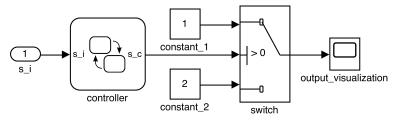

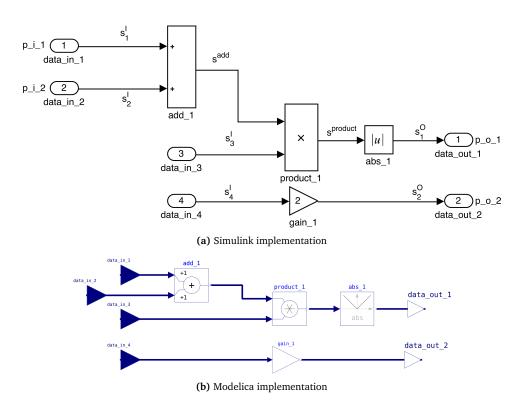

(a) Example model containing a Switch block to route signals

(b) Example model containing a set of conditionally executed subsystems implementing an if-then-else structure

(c) Control flow modeling using Switch-Case subsystems

Figure 2.3: Examples of control flow modeling in Simulink

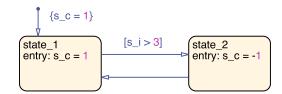

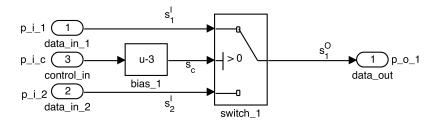

**Control Flow.** Control flow in Simulink is modeled using two different concepts. The first is the utilization of routing blocks  $B^R$ , such as Switch and MultiPortSwitch, which route one signal from a set of signals connected to the in-going ports of the routing block to a single out-going signal, depending on the current value of the signal connected to an in-going control port. Figure 2.3a shows an example model consisting of a Switch block that connects  $s_{i_1}$  or  $s_{i_2}$  to its out-going signal  $s_o$  if  $s_c > 0$  or  $s_c \leq 0$ , respectively. The second concept to model control flow is conditionally executed If-Action and Switch-Case subsystems. Control flow utilizing If type subsystems consists of at least two If-Action subsystems connected If-Action subsystem is triggered. A model utilizing the Switch-Case subsystems is modeled similarly, with the control block implementing a *switch* semantics based on a single in-going signal and triggering the execution of corresponding connected subsystems. Due to the underlying signal-flow semantics, the simulator has to calculate a value for every block and output at every simulation step.

In case of If-Action subsystems not triggered during the current simulation step, their output is reset to 0. In case of Figure 2.3b, if the subsystem if\_action is triggered, the value of outport out\_2 is equal to 0.

Simulation MATLAB Simulink Models. Simulation of a Simulink model is performed using solvers, which approximate the output of each block according to its semantics. Solvers for time-discrete as well as time-continuous interpretations of the block diagram exist. While the former compute the output for each simulation step based only on the current state of each block, the latter utilize numerical techniques to compute the state of each block based on multiple states and their derivatives. Further, solvers can be classified by the type of step size used in their calculation of the simulation state: Variable-step solvers aim at automatically finding a simulation step size for each block in the model to achieve a level of precision set by the model developer. Fixed-step solvers omit this step at the expense of precision while increasing performance. The former class of solvers is commonly used for hybrid or purely time-continuous systems that form differential equations, while the latter is used for time-discrete models forming difference equations. For the development of embedded control software, i.e., when code is generated from the developed models, solvers with a fixed time step size are used [Conrad 2004; The MathWorks 2017e]. In this thesis, our focus is the analysis of such discretely-timed models.

#### Stateflow

Stateflow [The MathWorks 2017d] is an extension to the MATLAB Simulink framework that enables the modeling of decision logic using a semantics based on Statecharts, originally introduced by Harel [1987]. Stateflow automata are hierarchical state machines composed of states labeled with actions and transitions labeled with guards as well as actions. Stateflow state machines are commonly used to model discrete control logic and modal behavior of a system.

The syntax of a Stateflow automaton *SF* given by Tiwari [2002] is described by a tuple SF = (D, E, S, T, f), where:

- $D = D_I \cup D_O \cup D_L$  is a finite set of typed variables partitioned into input variables  $D_I$ , output variables  $D_O$  and local variables  $D_L$ ;

- $E = E_I \cup E_O \cup E_L$  is a finite set of *events* partitioned into input events  $E_I$ , output events  $E_O$  and local events  $E_L$ ;

- *S* is a finite set of states, in which each state contains three set of actions: *entry*, *exit*, and *during*. An action can either be a variable assignment, as in imperative programming languages, or the broadcast of an event;

- *T* is a finite set of transitions, each given as a tuple (src, dst, e, c, ca, ta), in which  $src \in S$  is the source state,  $dst \in S$  is the destination state,  $e \in E \cup \{\epsilon\}$  is an event,  $c \in WFF(D)$  is a condition given as a well-formed formula in predicate logic over the variables *D*, and *ca*, *ta* are sets of *transition* and *condition* actions that are triggered when the transition is taken or a condition is evaluated to true, respectively;

- $h: S \rightarrow (\{and, or\} \times 2^S)$  is a mapping from the states to the Cartesian product of  $\{and, or\}$ with the power set of *S*, which describes the hierarchy of the Stateflow chart. It satisfies the following properties: (1) there exists a unique root state  $s^{root}$ , i.e.,  $s^{root} \notin \cup_i descendants(s_i)$ , where  $descendants(s^i)$  is the second component of  $h(s_i)$ , (2) every non-root state *s* has exactly one ancestor state, that is, if  $s \in descendants(s_1)$  and  $s \in descendants(s_2)$ , then  $s_1 = s_2$ , and (3) the function *h* contains no cycles, i.e., the relation < on *S* defined by  $s_1 < s_2$  iff  $s_1 \in descendants(s_2)$ is a strict partial order. If  $h(s) = (and, \{s_1, s_2\})$ , then the state *s* is an AND-state consisting of two substates  $s_1$  and  $s_2$ . If  $h(s) = (or, \{s_1, s_2\})$ , then *s* is an OR-state with substates  $s_1$  and  $s_2$ .

**Simulation of Stateflow Automata.** During simulation of a Stateflow automaton, the configuration describing the current state of the automaton  $C \in 2^S \times \mathcal{D}$  is a tuple consisting of the set of active states and a valuation of all variables in *D*, denoted by  $\mathcal{D}$ . If a non-leaf OR-state is active, then exactly one of its descendant substates is active, and if a non-leaf AND-state is active, then every descendant substate is active. The set of all configurations that satisfy these conditions, denoted by  $\mathcal{C}$ , is called the set of valid configurations. The Stateflow semantics is given by a function  $|SF| = \mathcal{C} \times \mathcal{D}_I \times E_I \to \mathcal{C}$ . This function maps a configuration, a valuation of the input variables, and an input event to a new configuration.

This semantics is only provided informally by the Stateflow specification [The Math-Works 2017d]. An input event *e* triggers the execution of the initial state. A state executes by performing its corresponding *entry* actions and *firing* all of its transitions that can be fired. If none of its transitions can be fired, the state triggers executions of its descendant states: either one or all, depending on the state being an OR-state or an AND-state. A

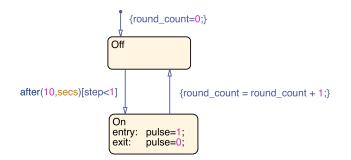

Figure 2.4: Example of a Stateflow automaton

transition t = (src, dst, e, c, ca, ta) can be fired if (1) event *e* is present, (2) condition *c* is evaluated to true, and (3) state *src* is currently active. If a transition executes, it preempts execution of state *src*, executes its corresponding condition actions *ca*, enters state *dst*, and executes its transition actions *ta*. Whenever an assignment action x := expr is executed, the variable  $expr \in D$  will be assigned the value *x*. An event broadcast can be considered similar to a function call in imperative programming languages, as it triggers execution of the states and transitions accepting the event.

Consider the example given in Figure 2.4. The automaton shown there utilizes two states *Off* and On. The initial state, Off, is set using the default transition from the • mark. When the automaton is initialized, the value of the output variable round\_count is set to 0. Shown in square brackets on the out-going transition is its *transition guard*, that only allows activation of the next state if its corresponding condition is fulfilled. To progress to state On from Off the condition step < 1 has to be fulfilled. Furthermore, this condition is only evaluated 10 s after state Off has been activated, i.e., after the *temporal logic condition* is fulfilled. Upon entering state On, its entry action is executed, setting the value of the internal variable pulse to 1. Upon exiting the state, its exit action is executed, setting pulse to 0. As its out-going transition is not marked by a condition, the state will always be left one simulation step after it has been entered. When taking this transition, its transition action is executed and the output variable round\_count incremented by 1.

#### 2.2.4 Modelica

Modelica is a modeling language that is used for the specification of mathematical models of complex systems whose behavior evolves as a function of time [Fritzson 2004]. First introduced in Fritzson and Engelson [1998], Modelica implements non-causal modeling

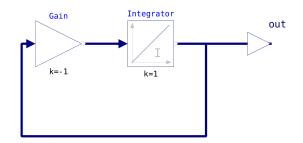

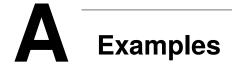

Figure 2.5: Graphical model representation

of signal-flow graphs, similar to that of MATLAB Simulink, i.e., based on equations instead of assignment statements. This enables reusability of components in multiple situations. In addition to this concept, Modelica is an object-oriented language with a generic class concept and implements *generics* (similar to *templates* in C++) and subtyping to further increase reusability of components [Modelica Association 2017]. Finally, it supports the modeling and simulation of physical systems with components from multiple domains. A set of libraries for each domain as well as a connecting layer that, e.g., resolves signal units, allows modeling of systems which share, e.g., mechanical, hydraulic, or electrical components. The syntax of Modelica is, analogous to MATLAB Simulink, defined as presented in Section 2.2.2.

```

model SimpleExample

1

Modelica.Blocks.Math.Gain Gain(k = -1)

2

annotation(Placement(/* omitted */));

3

Modelica.Blocks.Continuous.Integrator Integrator(y_start = 1)

4

annotation(Placement(/* omitted */)));

5

Modelica.Blocks.Interfaces.RealOutput out

6

annotation(Placement(/* omitted */)));

7

equation

8

connect(out, Integrator.y) annotation(

9

Line(/* omitted */)));

10

connect(Gain.u, Integrator.y) annotation(

11

Line(/* omitted */)));

12

connect(Gain.y, Integrator.u) annotation(

13

Line(/* omitted */)));

14

annotation(

15

uses(Modelica(version = "3.2.2")));

16

end SimpleExample;

17

```

**Listing 2.1:** Textual representation of the Modelica example model with layouting information omitted

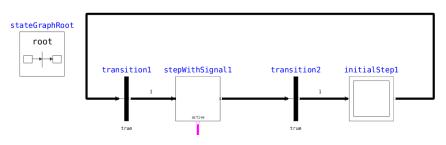

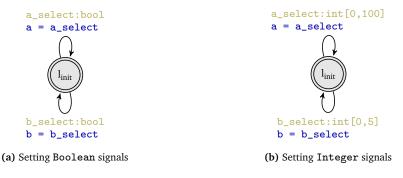

Figure 2.6: StateGraph example

An example of a Modelica model can be seen in Figure 2.5. Shown there is, analogous to functionality available in MATLAB/Simulink, a Gain block multiplying its incoming signal by -1, and an Integrator block, summing the values of its incoming signals from the start of the simulation. The internal state of the Integrator at the start of the simulation, i.e., the initial value necessary to solve the underlying difference equation, is set to 1. Listing 2.1 shows the textual representation of the system that is created automatically when designing the system. Shown there are the blocks comprising the system and the connections between them defining the functionality.

Due to the focus on component reusability and structural modeling, Modelica has found widespread adoption in the domain of high-level architectural design of safetycritical embedded systems [Tiller et al. 2003; Brückmann et al. 2009; Chrisofakis et al. 2011; Sutherland et al. 2016].

#### State-Machine-Based Modeling in Modelica

Modeling of state machines in Modelica is possible via the StateGraph library [Donath et al. 2008; The Modelica Association 2019b]. The blocks in this library offer the possibility to model finite state machines based on Steps and Transitions, i.e., states and edges, respectively. An example is shown in Figure 2.6. As can be seen there, steps represent to the possible states of a StateGraph model [Otter et al. 2005]. If a step is active, a Boolean variable corresponding to the step is true. Initially, all steps are deactivated, and the initialStep object is activated. This initial step is characterized by a double box. The state of the model is changed using transitions. When a step is activated, its outgoing transition is initially deactivated, and only activates once its transition condition is evaluated to *true*.

In addition to these basic modeling possibilities, controllers in StateGraph support parallel execution of transition, i.e., multiple states can be active at the same time.

## 2.3 Information Flow Analysis

The protection of confidentiality of information inside a software system as well as the protection from modification by unauthorized sources is a long-standing and increasingly important problem in the area of general computing as well as of embedded, and, in particular cyber-physical systems. Techniques that assert whether a system complies with a set of *security properties* are grouped under the term *information flow control* (IFC) [Hammer 2009].

When analyzing the security of a software system, the following main dimensions commonly referred to as the *CIA triad* [Saltzer and Schroeder 1975; Cherdantseva and Hilton 2013], can be identified:

- *Confidentiality* states that every party in a system is only able to read data according to its specified security level, i.e., that only authorized recipients are able to read data marked as confidential.

- *Integrity* ensures that critical computations cannot be manipulated from the outside or that data has not been altered during transmission from source to target.

- *Availability* guarantees that information or resources are available to authorized users when required, i.e., according to a specified extent and timing.

As first noted in Biba [1977], integrity can be considered a dual to confidentiality and both can be enforced by controlling *information flow* through a program. As explained above, confidentiality prohibits the flow of information to inappropriate sources while integrity requires that information is prevented to flow from inappropriate sources. To identify violations of either property, the flow of information through software systems has to be analyzed.

#### 2.3.1 Types of Information Flow

Within a software system, different kinds of information flow can be observed: *explicit* and *implicit* flows. The former describes flows of information through variables that are explicitly stated in the source code of the software under analysis, i.e., information is explicitly leaked to a publicly observable variable. An example, shown in Listing 2.2, uses two variables, h and l of differing security levels *HIGH* and *LOW*, respectively. As is shown there, the value of the private variable h is assigned to the publicly observable, lower-security variable l, a violation of confidentiality.

| 1 | var l, h; |

|---|-----------|

| 2 | l := h;   |

Listing 2.2: An explicit information flow from variable *h* to variable *l*

The second type of information flow, *implicit flow*, can manifest in a number of ways:

- *Control flow* With knowledge of the program source code and structure, an observer is able to deduce the values of private variables by observing the control flow of a program. An example for a flow of this kind is shown in Listing 2.3. There, the value of the private variable h is never directly assigned to a publicly observable variable but an observation of the public value of l allows deduction of h [Denning and Denning 1977].

- *Timing* Similarly, by using knowledge of the program structure, this implicit flow allows the deduction of the values of private variables by analyzing the execution time of the software for different sets of input values. As the example in Listing 2.4 shows, the execution time allows an observer to draw conclusions about the value of *h*, albeit not being directly assigned to a publicly observable variable [Kocher 1996].

- *Power* By measuring the power consumption of the system executing the software under analysis, e.g., a cryptographic algorithm, an observer can deduce private information, such as keys utilized in the computation [Kocher et al. 1999; Singh et al. 2017].

| 1 | <b>h</b> := <b>h</b> mod 2; |

|---|-----------------------------|

| 2 | 1 := 0;                     |

| 3 | if $h == 1$ then            |

| 4 | l := 1;                     |

|   |                             |

Listing 2.3: Implicit information flow through the control structure of a program

Which type of information flow is a concern to the developer depends on what attackers are able to observe. For example, smart cards or *Near Field Communication* (NFC) devices draw power from the potentially untrusted device they are inserted into or come into contact with, which makes it necessary to mask the power-based information flow in such systems.

```

var l, h;

if h == 1 then

// execute time-consuming function f()

f();

l := 0;

```

Listing 2.4: Implicit information flow through program timing

To be able to analyze information flow through a program, a variety of methods and approaches has been developed since the inception of the field in Lampson [1973]. These IFC approaches aim to make it possible to follow implicit as well as explicit flows of information through software and are additionally used to *control* the flow of information. Early works in the field, such as Fenton [1973] or Bell and LaPadula [1973], developed *mandatory access control*. In this approach, variables in a program are assigned *security levels*, and during the course of the execution of the program, an additional software layer calculates the dissemination of the data. In addition to its computational and storage overhead, this method has proven to be too restrictive for use in general code as no sharing of information between security levels is allowed. A further flaw of these purely run-time enforcement mechanisms lies in its inability to identify *implicit* information flow,.

#### 2.3.2 The Lattice Model of Secure Information Flow

In software systems, data is commonly classified into *security levels*  $L = \{l_1, ..., l_n\}$ . To express security policies, i.e., rules describing between which levels information is permitted to flow and has to be prevented, respectively, the following relations can be defined [Hammer 2009]:

- $\Rightarrow: L \times L$  is the transitive, reflexive and antisymmetric *interference relation*.  $x \Rightarrow y$  expresses that information from class x is only permitted to flow into class y.

- $\not\Rightarrow: L^2 \setminus \Rightarrow$  is the complement *noninterference relation*.  $x \not\Rightarrow y$  denotes that information flow from class *x* to class *y* must be prevented in the system.

In an early approach to define a mathematical framework to formulate requirements for secure information flow between sets of security levels, Denning [1976] identified *lattices* to naturally express relations between security levels. If these levels are arranged in a lattice, the relation  $\rightsquigarrow$  is equivalent to  $\leq$ . If a direct comparison between security

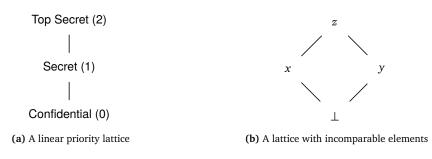

Figure 2.7: Examples of lattice representations of security models

levels is not possible, a complete lattice  $\mathcal{L} = \{L, \leq, \perp, \top, \sqcup, \sqcap\}$  can be defined. Figure 2.7 shows examples of both situations. In Figure 2.7a, an example of a linear priority lattice, the three security levels Confidential (0), Secret (1) and Top Secret (2) are ordered in a linear fashion and a direct comparison between every level is possible, i.e.,  $0 \le 1 \le 2$ . Figure 2.7b shows the more complex example of a security classification, in which a direct comparison between levels is not possible in every case, i.e., neither  $x \le y$  nor  $y \le x$ . In this case, the supremum operator  $\sqcup$  defines the resulting security level when two pieces of information from incomparable levels are combined. As the example in Figure 2.7a shows, when information from level x and y are joined, the resulting level must be z.

#### 2.3.3 Information Flow Control

An early method to track explicit as well as implicit flows on the source code level has been introduced in Bergeretti and Carré [1985]. In this work, the authors describe an IFA technique based on data flow equations, which are heavily utilized in the program optimization steps of compilers [Nielson et al. 1999].

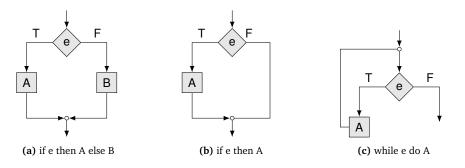

Figure 2.8: Control-flow graphs of program statements [Bergeretti and Carré 1985]

These information flow equations are constructed with special consideration of the three main program flow elements, shown in Figure 2.8. For each structure, the authors present equations to calculate three properties of information flow. For a variable  $v \in V$  and the expression  $e \in E$  in the statement *S*, the first property  $v \lambda_S e$  states that the v may be used in the evaluation of e in *S*. The example in Listing 2.5 contains two expressions, y > 0 and y + z. The value of y may be used in the evaluation of both expressions, while the value of z may be used be used in the expression y + z only. A more complex example for this property is shown in Listing 2.6. There, the value of x may be used in the evaluation of the final expression 2 \* y as depending on the value of x, an assignment to y will have been made in the previous statement y := 1 and this value will be used in the expression. This implicit flow of information between variables x and z therefore becomes visible.

| L | if $y > 0$ then |  |

|---|-----------------|--|

| 2 | x := y + z;     |  |

1

**Listing 2.5:** A simple example of the  $\lambda$  property

| 1 | if $\mathbf{x} > 0$ then |

|---|--------------------------|

| 2 | y := 1;                  |

| 3 | z := 2 * y;              |

**Listing 2.6:** A more complex example of the  $\lambda$  property

The second property  $e \mu_S v$  signifies that a value of the expression e in S may be used in obtaining the value of v on exit from S. An example is shown in Listing 2.7. Both the expressions w > 0 and y + z may be used in obtaining the value of the variable xon exit from the presented statement. In case of a successful evaluation of the first expression, the value of x on exit from S is the sum of y and z, otherwise it will retain its original value. In either case, both expressions may be used.

| 1 | if $\mathbf{w} > 0$ then                 |

|---|------------------------------------------|

| 2 | $\mathbf{x} := \mathbf{y} + \mathbf{z};$ |

**Listing 2.7:** A simple  $\mu$  property example

Finally, the third property  $v \rho_S v'$  describes a relation between two variables on entry and on exit of the statement *S*. The value of *v* may be used in obtaining the result of an expression *e* in *S*, which in turn may be used in obtaining the value of *v'* on exit from *S*. It can be expressed as  $\rho_S = \lambda_S \mu_S$  and therefore forms the necessary connection to put two variables in a single program construct *S* into an information flow relation to each other. The authors further extend the concept to the connection of multiple program statements to be able to calculate the information flow between arbitrary variables in the source code.

As is shown in these examples, this form of *static* information flow analysis is able to detect explicit as well as implicit flows of information in a given program. In comparison to dynamic IFA approaches, such as Suh et al. [2004], which are only able to track the flow of information over a single execution of a program, static methods identify flows over *all* executions and paths.

#### 2.3.4 Non-Interference

If data inside a program is to be kept confidential, its developer might create a security policy stating that the computation of this secret data is not affected by publicly observable inputs or outputs of the program. This allows secret data to be calculated and modified inside the program as long as visible outputs do not reveal any information about this data. Such a policy is called a *non-interference* policy, first introduced in Goguen and Meseguer [1982]. A usual method to show that a non-interference policy holds is to demonstrate that an observer of the public variables cannot distinguish between two executions of the program that only differ in their confidential inputs [Goguen and Meseguer 1984; Sabelfeld and Myers 2003], i.e., no information flow from the secret inputs to the publicly observable outputs is allowed. In this manner, information flow control techniques can be used to prove non-interference [Hammer and Snelting 2009].

### 2.3.5 Path Conditions

As explained in Section 2.3.3, a static information flow analysis is able to detect both implicit as well as explicit flows through a program due to its analysis of all paths through said program. Therefore, these analysis techniques are inherently *safe* with regard to their ability to detect information flow. However, to remain computable, such analyses only provide approximate answers [Nielson et al. 1999], i.e., they present an over-approximation of the actual solution. To increase the precision of a static information

Listing 2.8: Example utilization of path conditions in information flow analysis

flow analysis, King [1976] introduced *path conditions* that describe necessary conditions for paths to be executed. In Hammer et al. [2006, 2008], path conditions are used to capture all paths where information might flow from a source to a target.

Consider the example given in Listing 2.8. As is shown there, an element of the array a serves as storage for the value of high, in this example a variable of a high security level. Inside the if scope, the variable of low security, low, is assigned a value of the array. Given the policy that no high security information is to be leaked into a lower security domain, a static analysis, as presented in Section 2.3.3, detects a policy violation in the two assignments as information is able to flow through the array. However, when analyzing the condition of the if clause, it becomes apparent that information flow through the array only occurs for certain ranges of the variables i and j. It is therefore possible to express *path conditions* for the flow of information between Line 1 and Line 3 of the given example. Only if i > 10, the assignment to the low security variable occurs and a policy violation occurs. The following describes the path condition of information flow between Line 1 and Line 3 of Listing 2.8:

$$PC(1 \rightarrow 3) = \exists i, j((i > 10) \land (i + 3 = 2j - 42))$$

$$= true$$

1 a[i + 3] = high; 2 if ((i > 10) && (j < 5)) 3 low = a[2 \* j - 42];

Listing 2.9: More complex example utilization of path conditions in information flow analysis

A slightly more complex example is shown in Listing 2.9. There, the information flow condition is extended to include the variable j and the path condition is expressed in the following:

$$PC(1 \rightarrow 3) = \exists i, j((i > 10) \land (j < 5) \land (i + 3 = 2j - 42))$$

$$= false$$

As opposed to Listing 2.8, this extended path condition allows a safe conclusion about the existence of information flow between the high and low security variables. In fact, as there is no assignment of values to i and j such that the additional conditions are fulfilled. Information flow is therefore impossible.

### 2.4 Constraint Logic Programming

In the following, we give a brief introduction to the concept of *Constraint Logic Programming* (CLP). In this thesis, we utilize CLP to identify solutions to sets of path conditions extracted from the signal-flow-oriented components of control system models under analysis.

CLP was introduced in Jaffar and Lassez [1987] and extends *logic programming* to include the concept of *constraints*. In general, CLP can be seen as a technique to solve CSPs, which are defined as a triple  $\mathscr{P} = (V, D, C)$  consisting of [Frühwirth et al. 1992; Niederliński 2011]:

- a finite set of variables  $V = \{v_1, \dots, v_n\};$

- a set of domains  $D = \{D_1, ..., D_n\}$  with  $\{v_1 : D_1, ..., v_n : D_n\}$ ;

- a set of constraints C<sub>j</sub>(V<sub>j</sub>), j ∈ {1,...,m} with each constraint establishing a relation of a subset of variables V<sub>j</sub> = {v<sub>j1</sub>,...,v<sub>jk</sub>} ⊆ V to each other and to solutions from a subset of D<sub>j1</sub> × ··· × D<sub>jk</sub>.

A solution to a CSP is given by any assignment of domain values to variables that satisfies all constraints. It may be *non-unique* or *unique*; Additionally, CSPs may contain an *objective function* which, as an additional part of the solution, is to be minimized or maximized. In this case, they are referred to as *Constraint Optimization Problems* (COPs) and their solutions as *optimum* solutions. If the domains *D* are restricted to *finite* domains, the problem is called *a finite constraint satisfaction problem* (FCSP) [Mackworth

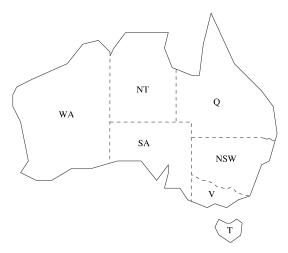

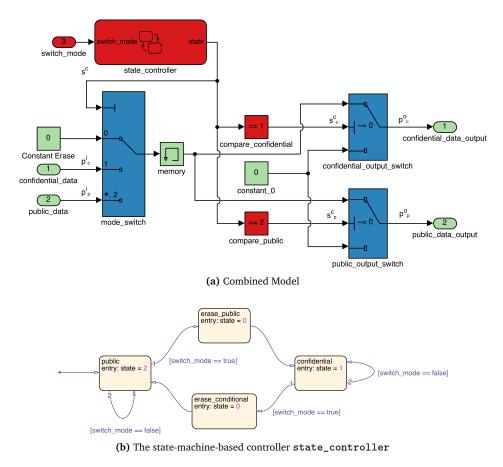

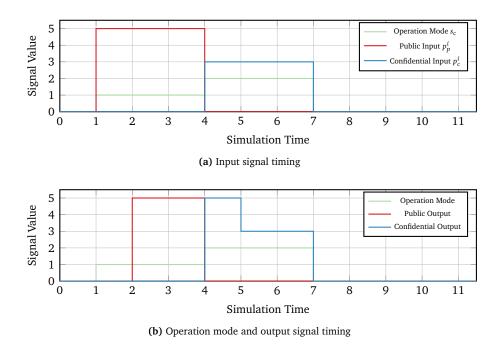

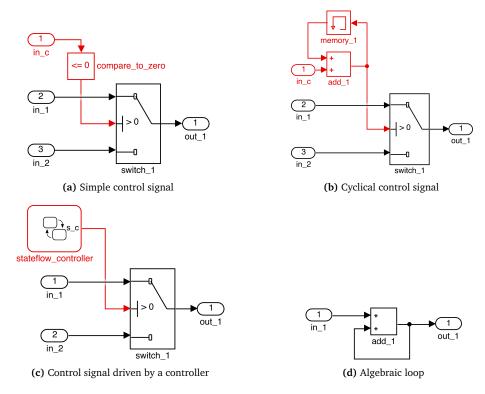

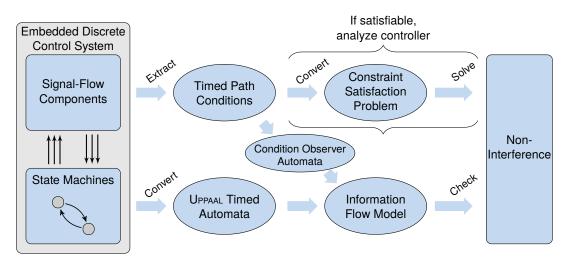

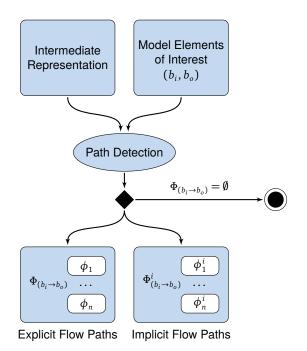

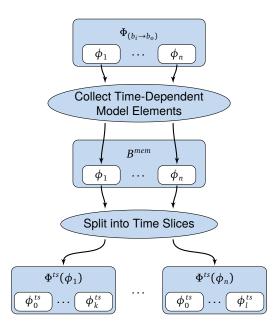

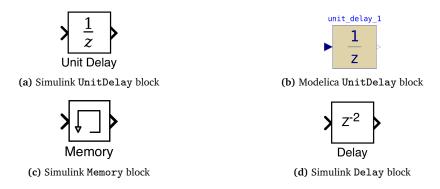

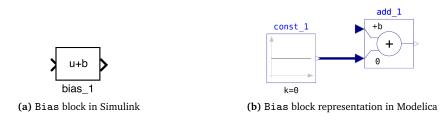

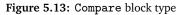

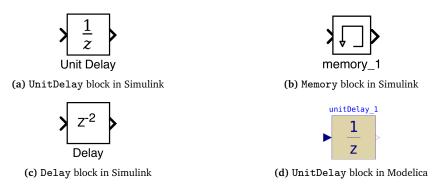

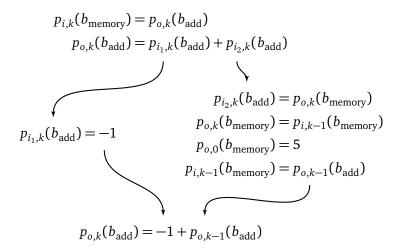

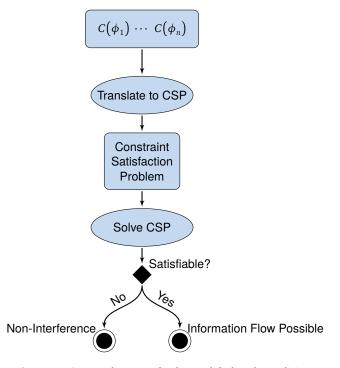

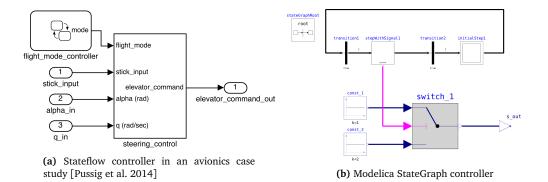

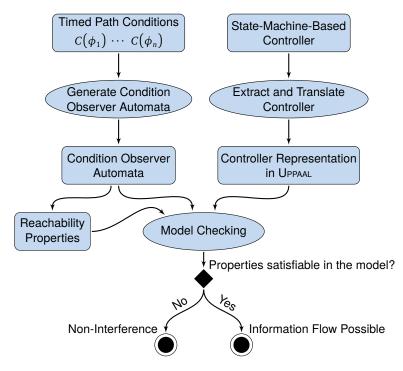

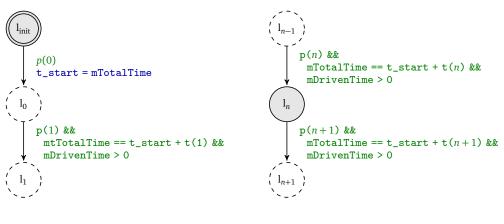

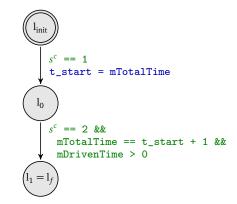

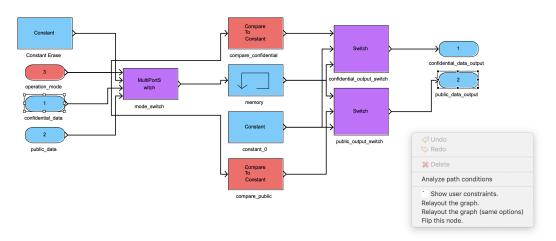

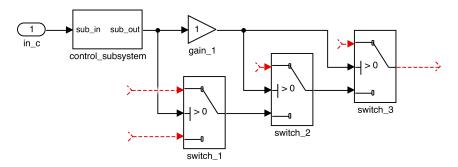

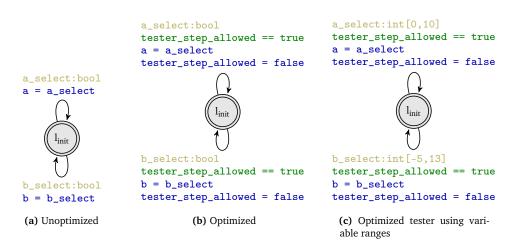

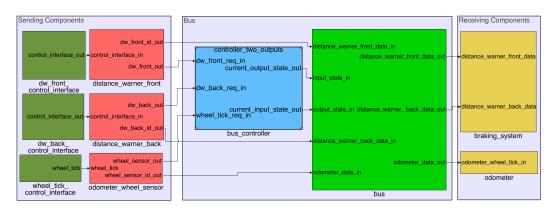

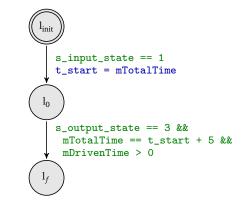

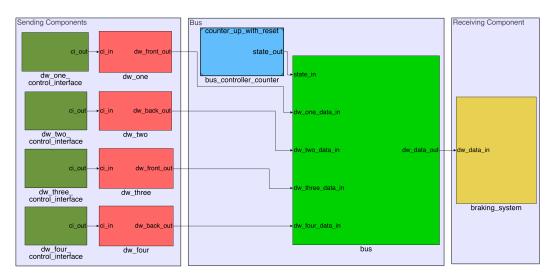

Figure 2.9: Map of the seven states and territories of Australia [Marriott et al. 1998]