## Parallelization of Legacy Automotive Control Software for Multi-Core Platforms

vorgelegt von M.Sc. Martin Lowinski

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

> Doktor der Ingenieurwissenschaften – Dr.-Ing. –

> > genehmigte Dissertation

Promotionsausschuss:

| Vorsitzender: | Prof. Dr. Clemens Gühmann |

|---------------|---------------------------|

| Gutachterin:  | Prof. Dr. Sabine Glesner  |

| Gutachter:    | Prof. Dr. Rainer Leupers  |

| Gutachter:    | Prof. Dr. Ben Juurlink    |

Tag der wissenschaftlichen Aussprache: 10. Dezember 2018

Berlin 2019

#### Abstract

Automotive control-based applications become more and more sophisticated due to the continuous addition of new functionalities. At present, this functionality is implemented as runnables that are recurrently and sequentially executed inside software tasks. These computing-intensive tasks are typically concurrent to each other and hence can be executed in parallel on multi-core platforms.

Due to the increasing functionality, future tasks will exceed the computational power of a single core and have to be parallelized. When parallelizing a single task, it is critical that the order of execution, the communication and its timing of the legacy implementation is maintained. Otherwise, the behavior may change that could result in an incorrect functionality. These legacy requirements limit the concurrency inside a task such that an efficient parallelization is often hardly possible. Due to the high amount of functional interdependencies and the varying runnable execution times, synchronization is required to ensure the correct order of communication between parallelized tasks. However, any synchronization can potentially degrade the performance especially when the observed worst case execution times (oWCETs) of the runnables are overrun.

In this thesis, we present a parallelization approach that can cope with the requirements of automotive legacy software tasks. Our approach provides scalable and efficient heuristics to exploit the concurrency of real-world legacy tasks for parallelization. By optimizing the parallelization toward a novel robustness metric, the approach can cope with oWCETs and reduce the synchronization between resulting parallel tasks.

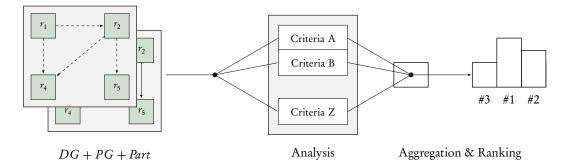

The concurrency inside legacy tasks is often limited due to various optimizations and construction principles for single-core platforms. Yet, these limitations are not always mandatory to the functional correctness. Our approach provides a semi-automated analysis to detect and eliminate these limitations and to increase the concurrency of a task that can be exploited for parallel execution. The typical bottleneck resource in any multi-core migration is the effort to ensure the functional correctness of the system by consulting functional development experts. This effort is reduced through our approach by ranking and proposing only the most promising task design changes to these experts for the validation of functional correctness.

Finally, we have implemented the proposed approach and evaluated it in several case studies with tasks from real-world automotive engine management systems.

#### Zusammenfassung

Aufgrund von neuen Funktionalitäten werden regelungstechnische Anwendungen im Automobilbereich stetig anspruchsvoller. Aktuell werden diese Funktionalitäten in Runnables implementiert, die periodisch und sequentiell innerhalb von Software Tasks ausgeführt werden. Diese rechenintensiven Tasks sind typischerweise zueinander nebenläufig und können somit auf Mehrkernsystemen parallel ausgeführt werden.

Infolge von zunehmender Funktionalität werden Tasks zukünftig die Rechenleistung eines einzelnen Rechenkerns übersteigen und müssen parallelisiert werden. Bei der Parallelisierung eines Tasks ist es entscheidend, dass die Ausführungsreihenfolge, die Kommunikation und dessen zeitliche Abfolge der vorhergehenden Implementierung beibehalten wird. Andernfalls könnte es das Verhalten so verändern, dass eine Funktionalität unzulässig wird. Diese Alt-Anforderungen beschränken die Nebenläufigkeit innerhalb eines Tasks, sodass eine effiziente Parallelisierung oft kaum möglich ist. Aufgrund von einem hohen Maß an funktionalen Abhängigkeiten und unterschiedlichen Ausführungszeiten der Runnables ist eine Synchronisation notwendig, um eine ordnungsgemäße Kommunikation zwischen den parallelisierten Tasks zu gewährleisten. Allerdings beinhaltet jede Synchronisation das Risiko die Leistung zu verschlechtern, insbesondere wenn die beobachteten WCETs der Runnables überschritten werden.

In dieser Dissertation präsentieren wir ein Vorgehen zur Parallelisierung, das den Anforderungen von Software Tasks aus Alt-Systemen im Automobilbereich genügt. Unser Vorgehen bietet skalierbare und effiziente Heuristiken um die Nebenläufigkeit von Tasks aus industriellen Alt-Systemen auszunutzen. Durch die Optimierung der Parallelisierung mittels einer neuen Robustheits-Metrik beherrscht unser Vorgehen beobachtete WCETs und reduziert die Synchronisation zwischen parallelisierten Tasks.

Oft ist die Nebenläufigkeit von Tasks aus Alt-Systemen jedoch durch Optimierungen für Single-Core Prozessoren beschränkt. Diese Einschränkungen sind allerdings nicht immer notwendig um die ordnungsgemäße Funktion zu gewährleisten. Unser Vorgehen bietet eine halbautomatische Analyse, um diese Einschränkungen zu finden und zu entfernen und damit die Nebenläufigkeit eines Tasks zu erhöhen, die widerum bei der parallelen Ausführung von Nutzen ist. Der typische Engpass bei jeder Migration auf Multi-Core Prozessoren ist der Arbeitsaufwand die funktionale Korrektheit zu gewährleisten indem Funktionsentwickler befragt werden. Dieser Arbeitsaufwand wird durch unser Vorgehen reduziert, da nur die vielversprechendsten Änderungen im Design eines Tasks diesen Experten zur Validierung der funktionalen Korrektheit vorgeschlagen werden.

Wir haben das vorgeschlagene Vorgehen implementiert und in mehreren Fallstudien mit Tasks aus Motorsteuergeräten aus dem Automobilbereich evaluiert.

## Acknowledgments

I would like to say thanks to all the people that supported me during my time as a PhD student. First and foremost, I want to thank Prof. Dr. Sabine Glesner for supervising my thesis and the insightful discussions and always helpful advice. I'd also like to thank Prof. Dr. Leupers and Prof. Dr. Juurlink for advising and surveying this thesis. I am grateful for being a part of the SESE research group at the TU Berlin, although working from Stuttgart. Thank you for all your advices, helpful discussions and support.

As an industrial PhD student at the Robert Bosch GmbH in Renningen, I want to express my sincere gratitude to my supervisor Dr. Dirk Ziegenbein. His valuable and sharp insights from academia and industry has made my time at the ManyCore project a both challenging and enriching experience. My appreciation also goes to my Bosch colleagues and especially to Dr. Jochen Härdtlein and Dr. Björn Saballus who created this extended collaboration of academia and industry. While sharing a research vision with my fellow ManyCore PhD students, namely Alexander Biewer, Dr. Matthias Freier, Dr. Peter Munk and Felix Rützel, I am likewise thankful for the good times we had. Thanks also to all the members of the Bosch research project ManyCore and the CR/AEA department. It was a pleasure to work with you in this skillful, friendly and open-minded environment.

Last but not least, I am most grateful for my family and dear friends. Thank you for the continuous encouragement, the endless support, love and joyful moments in my life. Writing this thesis would not have been possible without you.

## Contents

| Ti | Title Page<br>Abstract<br>Contents |                                              |    |  |  |

|----|------------------------------------|----------------------------------------------|----|--|--|

| Ał |                                    |                                              |    |  |  |

| Co |                                    |                                              |    |  |  |

| 1  | Intr                               | oduction                                     | 1  |  |  |

|    | 1.1                                | Problem                                      | 1  |  |  |

|    | 1.2                                | Objectives                                   | 3  |  |  |

|    | 1.3                                | Proposed Solution                            | 3  |  |  |

|    | 1.4                                | Main Contributions                           | 5  |  |  |

|    | 1.5                                | Overview of this Thesis                      | 5  |  |  |

| 2  | Арр                                | lication Domain                              | 7  |  |  |

|    | 2.1                                | Automotive Embedded Systems                  | 7  |  |  |

|    |                                    | 2.1.1 Feedback Control Systems               | 8  |  |  |

|    |                                    | 2.1.2 Real-Time Requirements                 | 13 |  |  |

|    |                                    | 2.1.3 Multi-core Platforms                   | 18 |  |  |

|    |                                    | 2.1.4 Model of Computation and Communication | 20 |  |  |

|    | 2.2                                | Software Development Process                 | 24 |  |  |

|    |                                    | 2.2.1 Model-based Development                | 25 |  |  |

|    |                                    | 2.2.2 Legacy Software                        | 26 |  |  |

|    | 2.3                                | Standards                                    | 28 |  |  |

|    |                                    | 2.3.1 ASAM                                   | 29 |  |  |

|    |                                    | 2.3.2 AUTOSAR                                | 31 |  |  |

| 3  | Rela                               | ated Work                                    | 33 |  |  |

|    | 3.1                                | Automatic Parallelization                    | 33 |  |  |

|    | 3.2                                | Parallelization using Domain Knowledge       | 36 |  |  |

|    | 3.3                                | Summary                                      | 38 |  |  |

| 4  | Solı                               | ition Space                                  | 41 |  |  |

|    | 4.1                                | Legacy Design of Tasks                       | 42 |  |  |

|    | 4.2                                | Evolving Tasks                               | 45 |  |  |

|    | 4.3                                | Splitting                                    | 46 |  |  |

|    | 4.4                                | Relaxation                                   | 50 |  |  |

|   | 4.5           | Parallelization Strategies 51           |  |  |  |  |  |

|---|---------------|-----------------------------------------|--|--|--|--|--|

|   | 4.6           | Summary                                 |  |  |  |  |  |

| 5 | Para          | arallelization Concept 55               |  |  |  |  |  |

|   | 5.1           | Software Development Process            |  |  |  |  |  |

|   | 5.2           | Graph Structures                        |  |  |  |  |  |

|   |               | 5.2.1 Dependency Graph 58               |  |  |  |  |  |

|   |               | 5.2.2 Precedence Graph 61               |  |  |  |  |  |

|   |               | 5.2.3 Partitioning Information          |  |  |  |  |  |

|   | 5.3           | Dependency Graph Extraction             |  |  |  |  |  |

|   |               | 5.3.1 Communication Dependencies        |  |  |  |  |  |

|   |               | 5.3.2 Functional Dependencies           |  |  |  |  |  |

|   | 5.4           | Summary                                 |  |  |  |  |  |

| 6 | Split         | ting 71                                 |  |  |  |  |  |

| - | 6.1           | Precedence Graph Generation 73          |  |  |  |  |  |

|   | 6.2           | Unsynchronized Splitting 77             |  |  |  |  |  |

|   | 6.3           | Synchronized Splitting 80               |  |  |  |  |  |

|   |               | 6.3.1 Objectives                        |  |  |  |  |  |

|   |               | 6.3.2 Mapping 85                        |  |  |  |  |  |

|   |               | 6.3.3 Synchronization 88                |  |  |  |  |  |

|   |               | 6.3.4 Integration                       |  |  |  |  |  |

|   | 6.4           | Summary                                 |  |  |  |  |  |

| 7 | Relaxation 93 |                                         |  |  |  |  |  |

| - | 7.1           | Relaxing Dependencies                   |  |  |  |  |  |

|   | 7.2           | Workflow                                |  |  |  |  |  |

|   | 7.3           | Impact Criteria                         |  |  |  |  |  |

|   |               | 7.3.1 Synchronization Points            |  |  |  |  |  |

|   |               | 7.3.2 Forward Evaluation                |  |  |  |  |  |

|   | 7.4           | Success Criteria                        |  |  |  |  |  |

|   |               | 7.4.1 Dependency Classification         |  |  |  |  |  |

|   |               | 7.4.2 Reaction Constraints 110          |  |  |  |  |  |

|   | 7.5           | Candidate Aggregation & Ranking 112     |  |  |  |  |  |

|   | 7.6           | Dependency Analysis                     |  |  |  |  |  |

|   | 7.7           | Summary                                 |  |  |  |  |  |

| 8 | Case          | Case Studies 11                         |  |  |  |  |  |

| - | 8.1           | Standalone Synchronized Splitting 115   |  |  |  |  |  |

|   | 8.2           | Relaxing & Unsynchronized Splitting 119 |  |  |  |  |  |

|   | 8.3           | Relaxing & Synchronized Splitting 121   |  |  |  |  |  |

|   |               |                                         |  |  |  |  |  |

| 9                          | 9.1             | clusion & Future Work<br>Summary | <b>127</b><br>127<br>129 |  |

|----------------------------|-----------------|----------------------------------|--------------------------|--|

| Bil                        | Bibliography    |                                  |                          |  |

| Publications by the Author |                 |                                  | 143                      |  |

| List of Figures            |                 |                                  | 145                      |  |

| List of Tables             |                 |                                  | 149                      |  |

| List of Algorithms         |                 |                                  | 151                      |  |

| Lis                        | List of Symbols |                                  |                          |  |

| List of Abbreviations      |                 |                                  | 155                      |  |

# **I** Introduction

Today's automotive applications employ highly sophisticated comfort, safety and powertrain functionalities which will continue to grow in the future [Aoy12, BKPS07]. For example, the power-train has to fulfill constantly tightened emission limits. The resulting complex functionality is implemented in embedded real-time control software with an increasing demand for computing power. Parallelism provided by multi-core processors is the most promising solution to satisfy the computational demand [But12]. To leverage it efficiently, the legacy software, originally developed and optimized for single-core processors, needs to be parallelized.

### 1.1 Problem

Automotive legacy control software is composed of interdependent software units. These software units are allocated to recurrently executed and concurrent tasks. Using the concept of Logical Execution Time (LET) [HHK01], the tasks can run on single- or multi-core processors with a deterministic behavior independent of their distribution to cores. However, there has been the established construction principle to allocate all software units with the same recurrence pattern to a single task. This construction principle is optimized for single-core processors and reduces the resource overhead. With this principle, additional or more complex functionalities cause the number of software units of a task to grow. The computational demand of tasks thereby increases and may exceed the computational power of a single core [MHAK15]. Such a task has to be parallelized by remapping the software units to multiple parallel tasks.

The software units interact through sensors and actors with the physical environment [SZ16]. The interaction is based on messages that are communicated between the software units. Every communication creates data and ordering dependencies. While parallelizing, these dependencies have to be maintained to ensure the data flow and thus the correct functionality of the legacy software. Also, control-based software is very sensitive to timing [AEF<sup>+</sup>14]. A change in the timing of a dependency results either in earliness or lateness of the communicated data. Especially in the latter case, a delayed communication potentially alters the functionality of controllers. Depending on the controller design, the delay may violate latency or stability requirements and other performance criteria. But ensuring all dependencies and their respective timing limits the parallizability and is prohibitively expensive in terms of synchronization overhead.

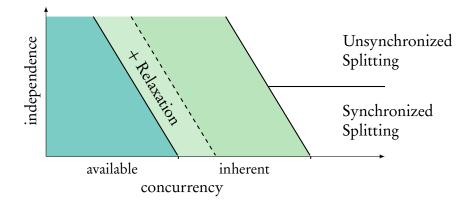

For a better understanding of the relationship between dependencies, timing and parallelization we introduce two fundamental terms by an example. Assuming a task is periodically executed and has two software units. One software unit samples the engine temperature and communicates the temperature value to the other software unit that represents the engine thermal controller. Due to the optimization for single-core, both software units are allocated to the same task as they have the same recurrence pattern. Furthermore, the two software units are executed in the order such that the sampling software unit runs before the engine thermal controller and always receives the latest temperature value. The timing between the two software units results in a tight coupling and a reduced concurrency, the *available concurrency*. However, from the physical and control-engineering perspective the temperature value could be communicated with a delay without compromising the correctness of the system. In our example, the assumed requirement is that the engine thermal controller has to start the engine fan when the temperature hits a threshold within 5 seconds. Assuming that the task that contains both software units is executed every 100 ms, a delay in communication of 100 ms between the sampler and the controller does not violate this requirement. With a delay, i. e., a relaxed timing, the thermal controller receives the temperature value from the sampler of the previous task instance. Hence, the two software units are decoupled temporally inside the task. The effect is that they become concurrent to each other which again can be used for parallelization. The resulting concurrency is called *inherent concurrency* as it represents the physically required timing and coupling of the software units.

The key for an efficient parallelization of a task is the knowledge of the *inherent concurrency* as the physically required timing is often more relaxed than the *available concurrency*. A relaxed timing improves the concurrency between software units inside a task that in turn can be exploited for parallelization. While the dependencies are maintained, relaxing means to change the timing of the communication and thus possibly changing the functionality. The knowledge where relaxation is allowed is typically not documented and hence only domain experts of the system are able to determine if the functionality is still correct. There are various techniques for the experts to evaluate the impact of an altered timing on the functionality of the controller such as formal verification or simulation. Nevertheless, the impact on the controllers' functionality of a relaxed timing can only be evaluated for a small number of dependencies due to time and cost reasons.

## 1.2 Objectives

This thesis addresses the problem described above which is the parallelization of highly inter-dependent tasks from automotive control software. Our solution establishes an analysis to guide a domain expert in finding a suitable and functionally correct parallelization with little effort. We require our analysis to fulfill the following criteria:

- *Automotive Ecosystem:* The approach should use existing models and respect requirements as well as constraints of the automotive domain. A convenient integration into the development processes of automotive Electronic Control Units (ECUs) and its surrounding ecosystem is required.

- *Scalable & Efficient:* The approach should cope with large and complex software models from e.g., real-world automotive applications such as an Engine Management System (EMS).

- *Observed WCET:* The approach should cope with execution time bounds that are measured at certain working points and are thus only observed bounds, i. e., tight but unsafe. Due to the complexity of automotive applications and the lack of predictable hardware, exact execution time bounds are unavailable.

- *Improve Concurrency:* The legacy design of tasks in the automotive domain strongly limits the concurrency inside a task. The approach should therefore be able to increase the level of concurrency, but should always maintain correctness.

- *Reduces Interactions with Experts:* Interactions with domain experts should be reduced in all phases of the approach because the domain expert is a scarce resource and the invested time needs to be spent efficiently. Requests of information to the domain expert should be precise and simple to ease information retrieval.

## 1.3 Proposed Solution

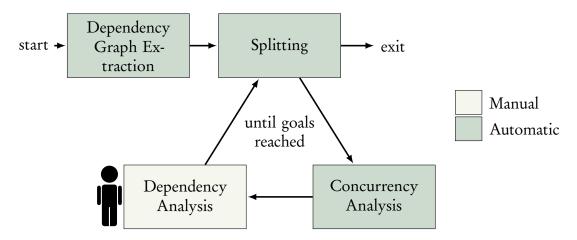

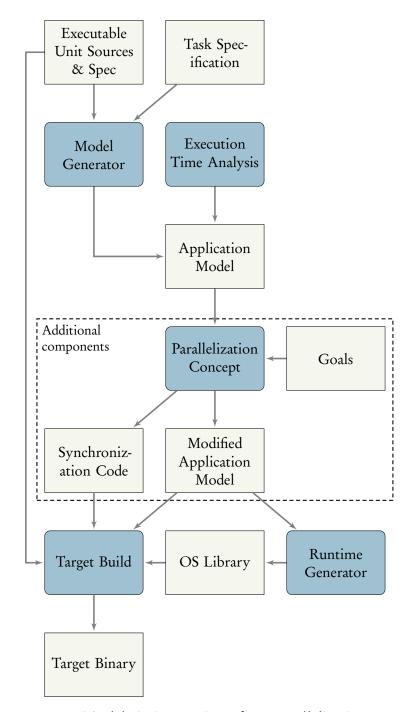

To achieve the objectives given above, we propose a semi-automatic iterative approach to parallelize a task by leveraging domain knowledge of experts. The main idea is to relax specific dependencies, i. e., changing the timing of the communication which may alter the functional behavior but is validated to remain correct. The starting point of our approach is the abstract representation from the legacy implementation of a task with its containing software units, dependencies and timing.

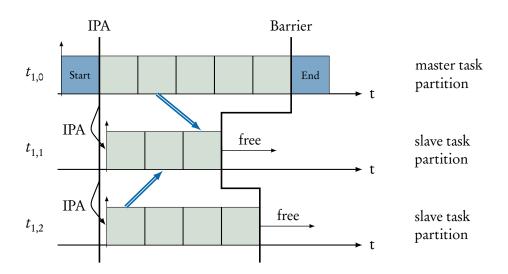

In the first step we parallelize a task by exploiting the available concurrency and check if the resulting parallel tasks match the parallelization goal. We parallelize by remapping the software units to multiple task partitions within the boundaries of the available concurrency. The dependencies and the respective timing between the software units are hereby maintained to ensure the legacy functionality. For the remapping we have two techniques. The first technique uses domain-specific heuristics that are scalable and can cope with high numbers of dependencies. We tackle the problem of widely varying execution times and Observed Worst-Case Execution Time (oWCET) by introducing synchronization between task partitions only where absolutely necessary. This technique can therefore deal with the current state of the practice in the automotive domain where software is typically not designed to allow tight Worst-Case Execution Time (WCET) bounds and sporadic misses of task deadlines are often tolerable. The second technique exploits the functional independent or temporally decoupled software units of the available concurrency. According to LET, when two software units of the same task either do not communicate or communicate solely via a relaxed timing, each can be allocated to a separate task partition. This technique allows to create task partitions without any synchronization and thus without any overhead.

If the parallelization goal is not reached, the available concurrency is too limited, e. g., due to the high number of dependencies or the synchronization overhead. Thus, in a second step we iteratively advance further towards the inherent concurrency by relaxing dependencies.

In general, every dependency is a potential candidate for evaluation by an expert to check if its timing can be relaxed without compromising the correctness of the system. To reduce the amount of interactions with an expert, we specifically look for dependencies which are more *relevant* to solve the parallelization challenge than others. The central idea is to determine a single dependency as candidate for evaluation by an expert. Through static analysis of the software units' dependencies and their role in the control algorithms, every dependency is assessed by multiple criteria. To identify the relevance, there are two groups of criteria: The first group indicates the potential benefit of a dependency, if it is relaxed, toward the given parallelization goal. Using graph algorithms, this group analyzes properties of the communication between software units. The second group rates the success, i. e., how likely it is that the timing of a dependency can be relaxed without significantly degrading the functional behavior. This can be quantified by the analysis of the physical dynamics of a dependency. These two groups of criteria are evaluated for each dependency, aggregated, and tuned for the different parallelization strategies. The results create the basis to select the most relevant dependency candidate. As our approach is iterative, the most relevant dependency is presented to the expert on every iteration.

The expert then evaluates if the controller still behaves correctly despite the relaxed timing of the dependency. On success, i. e., when the timing can be relaxed safely, the relaxation refines the implemented concurrent design of the task. This refined design becomes the input for the next iteration in our approach to find a suitable parallelization of a task.

## 1.4 Main Contributions

In summary, the main contributions of this thesis are:

- We propose a general model-based semi-automated workflow to parallelize a task from automotive legacy control software.

- We present two techniques to create multiple task partitions from a single task while maintaining all dependencies of the legacy implementation.

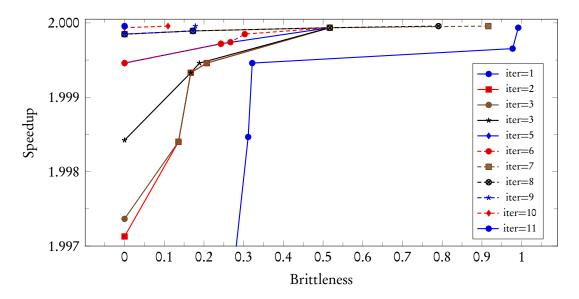

- The first most notable technique parallelizes using domain-specific scalable heuristics while keeping the synchronization to a minimum. By optimizing for a novel robustness metric, we can handle observed worst case execution times while sustaining a speedup despite synchronization.

- The second technique exploits the characteristics of LET with functionally independent or temporally decoupled software units to parallelize a task without any synchronization overhead.

- To extract the inherent concurrency of a task, we propose an approach to determine the dependencies which are more relevant to ease the parallelization challenge and thus more promising candidates for evaluation by a domain expert than others. This approach reduces the interactions with the domain expert and requests are held simple.

- The whole approach was implemented using the open source platform AMALTHEA to fit into the complex tool chains in the automotive domain. This supports interoperability, extensibility and unifies data exchange between tool vendors, engineering companies and other suppliers in the toolchain.

- We evaluated our approach on a real-word Engine Management System as an example of a complex application in the automotive domain. We performed experiments to investigate the performance benefit of our parallelization approach that shows a significant speedup while maintaining correctness.

These contributions have been made as part of the ManyCore research project in the Corporate Sector Research and Advance Engineering of the Robert Bosch GmbH. The Robert Bosch GmbH is a multinational company for engineering and electronics and a leading supplier of automotive components, technologies and services. Within Bosch, the ManyCore project is researching on systems engineering technologies and methods for parallel automotive applications. This thesis also represents a contribution to the project and its vision for parallel and robust control applications.

## 1.5 Overview of this Thesis

This thesis is structured as follows: In Chapter 2, we give an introduction to the automotive systems domain with its real-time requirements, feedback control systems, related standards and multi-core platforms. Then, in Chapter 3, we review related work on parallelization approaches, in particular approaches that utilize domain knowledge. In Chapter 4, we describe the fundamental problems when searching for concurrency that can be exploited for parallelization and outline the solution idea. In Chapter 5, we present our general concept and describe the contained components in detail. Starting with the fundamental graph structures, this chapter presents the core workflow for the parallelization of a legacy task. This chapter also describes the integration of the concept into the automotive development processes. The Chapters 6 and 7 present the two main components for splitting a task into multiple task partitions and the analysis to find suitable candidates to improve concurrency. In Chapter 8, we show the benefit of our approach applied to real-world automotive case studies. In particular, we use an EMS to demonstrate the efficient parallelization of a task with little effort. We conclude in Chapter 9 and provide possible directions for future research.

# 2 Application Domain

This chapter introduces fundamental background concepts, terminologies and notations that are used in this thesis. We start with embedded real-time control systems, then discuss standards and models and finish with the typical development process in automotive.

Technological advances foster ubiquitous and omnipresent electronic devices that are integrated in products of today's everyday life. These devices interact with the outside world by measuring, controlling and actuating through the product itself to the physical environment around it. In the following we use the term *embedded system* for an electronic computing device or system that forms an indivisible part or is tightly integrated into a product and is designed for a dedicated function [Mar10]. In contrast to general purpose computers, embedded systems have to cope with conflicting priorities such as performance, resource requirements (e. g., size, weight, power) and costs. Also, ninety-eight percent of all produced microprocessors are integrated in embedded systems [Bar09] and hence play a huge role in the semiconductor industry. Besides products that integrate embedded systems such as fridges, ticket machines, or TVs, safety-critical embedded systems such as pacemakers, robots or the field of Highly Automated Driving (HAD) are a far greater challenge.

### 2.1 Automotive Embedded Systems

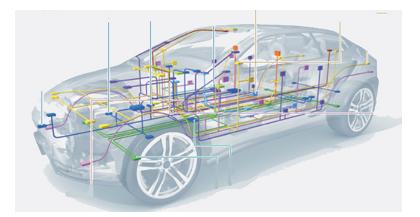

An especially challenging field for embedded systems is the automotive domain due to conflicting requirements of safety, performance and resource efficiency, low costs and coping with the increasing amount of systems and software [Bro05]. Figure 2.3 shows the car as a product with its many and diverse *system of embedded systems*. In a car, these embedded systems are typically integrated as an Electronic Control Unit (ECU). Therefore, embedded systems are not only a challenge due to being safety-critical, but also due to the complexity as the embedded systems need to cooperate to provide the dedicated function of a car. Automotive embedded systems have to be safety-critical because an error can cause high costs, severe injuries or in the worst case the loss of human lives. Examples that highlight this requirement are the airbag, Electronic Stability Control (ESC), Anti-lock Braking System (ABS) or radar-based systems. Resources for embedded systems in the automotive domain are limited because of efficiency and power dissipation reasons. For example, the camera for road sign detection is typically mounted behind the rear mirror. Therefore it cannot be actively cooled as it is part of the passenger compartment. The hardware parts for embedded systems are highly cost sensitive due to mass production. Small changes in the price per unit can have a huge impact on the production and business model. Today, a premium-class car contains 70 to 100 microprocessor-based Electronic Control Units (ECUs) and executes approximately one hundred million lines of code [Cha09]. An overview of such a system of embedded systems is illustrated in Figure 2.3. This huge amount originates from an exponential growth in software. The growth is caused by innovation through new functionalities that depend on complex algorithms and process huge amounts of data under real-time and safety-critical constraints [UBG<sup>+</sup>13]. One big driving force for this trend are the driving assistance systems. Starting with the simple cruise control system, these systems develop toward Highly Automated Driving (HAD) and ultimately autonomous driving.

Figure 2.1: Overview of the system of embedded systems in a car [Don14]. Every box represents an Electronic Control Unit with a dedicated function inside the car and is connected to other ECUs.

#### 2.1.1 Feedback Control Systems

A single embedded system inside a car always integrates hardware and software into a combined product that is interacting with and controlling its environment. In the following we call the integrated software an *application* because of its dedicated functionality. In embedded systems and especially in the automotive domain, the main purpose of applications is to control a chain of cause-and-effect with the environment. Hence they are *control applications* for feedback control systems. Control applications have the task to influence a time-continuous process such that it behaves in a certain way. Hereby, a parameter has to be chosen that is adjustable from the outside and can achieve a certain goal. As this choice depends on the distance to the specified goal, this process becomes a feedback loop with a controller that has yet to be defined. Control applications interact with a *dynamic system* (also called: plant). A system becomes dynamic when the characteristic parameters are a function of time. There are two important kinds of characteristic parameters. The input parameters cause changes inside the system in a time-continuous manner while the output parameters characterize the behavior of the system to these input parameters. The goal-oriented interference with a dynamic system is called controlling. A controller calculates a control signal depending on a reference signal. The controller and the dynamic system are interacting continuously, hence it is called a control loop.

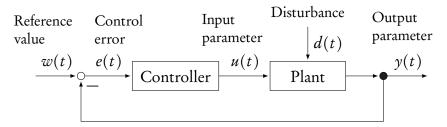

The more detailed interaction of a controller and a dynamic system in conjunction with its parameters is shown in Figure 2.2 [Lun16]. In this figure, the controller's task is to determine the input parameter u(t) that is fed into the system such that the output parameter y(t) ideally equals the reference value w(t) at all times t. Hereby y(t) is dependent on u(t) and the disturbance of the dynamic system d(t) that is manipulable. For the calculation of u(t), the controller knows the reference value w(t) that is to be achieved and the current output parameter y(t) of the dynamic system. Based on these two parameters, the controller can determine the control error e(t) which is important to calculate the input parameter u(t) and a unique characteristic of feedback control systems. The time the controller needs to calculate u(t) is called dead time.

As the controllers are integrated on ECUs that integrates a digital microcontroller or -processor, the processing is done discretely. Hence, a continuous input parameter has to be converted to a time- and value-discrete parameter and a discrete output parameter back to its external form of the dynamic system. The conversion from continuous parameters to time-discrete ones is called sampling; the parameters become value-discrete due to quantization errors in analog-digital converters.

**Figure 2.2:** General concept of a feedback control system that shows the interaction of the controller, the plant and the corresponding parameters [Lun16].

The Engine Management System (EMS) is one of the most complex and computing intensive examples of an automotive control application [Cha09, But12]. An EMS is a

control application and the software part of the ECU that controls a combustion engine. The automotive combustion engine is technically highly complex and sophisticated [Rei14]. Such an EMS constitutes the use case throughout this thesis. For less complex systems, the presented approach in this thesis is assumed to be applicable as well.

When looking at the evolving mechanism of the combustion engine itself, its essential goal is to generate a mechanical force by combustion of a fuel. At the time the Otto and Diesel combustion engines were invented, the dynamic system of combustion was controlled purely by mechanical components. However, the continuing development increased the complexity drastically over the years. This development was and is still motivated by the automotive industry and the government to increase efficiency and performance.

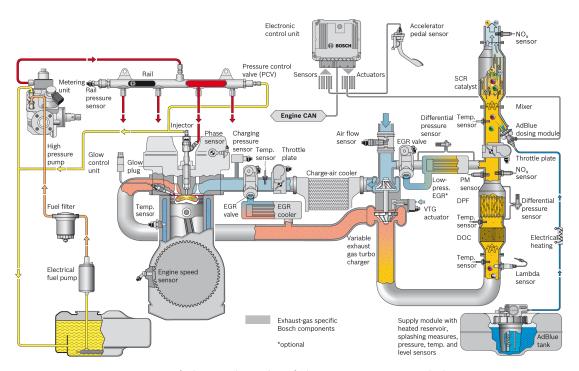

Today, the EMS is one of the most complex control applications as it has to control a wide variety of subsystems. Figure 2.3 gives an overview of the subsystems that an EMS for an up-to-date Diesel engine has to manage. Similar to the car itself, the EMS is again a system of systems. In the beginnings of the combustion engine, the throttle, injection, ignition and exhaust systems were the main components. Today, there are turbochargers, catalysts, additives injected into the exhaust and many more additional systems. Each system brings its own dynamic system and controlling challenge.

Internally, each subsystem of an EMS typically controls its own dynamic system. Yet, most of these systems are not isolated but highly dependent on each other. Additionally, the physical requirements of an engine demand high quality and stable controllers. Besides the physical requirements, many stakeholders, laws and regulations require improved fuel efficiencies, less  $CO_2$  emission and other features. This again facilitates the complexity of the subsystem controlling in an EMS.

All controlling systems in an EMS have to follow a causal loop such that the combustion works properly. For example, the system for the throttle calculates the amount of air needed by the injection, the injection system calculates the amount of gas that has to be combusted, air and gas have to be ignited at the right time that is calculated by the ignition system and so on. This causal loop is a very sensitive process as it depends on a huge amount of parameters that are dictated from the dynamic system and the controllers. This leads to a tight coupling of the systems and a high amount of communication between them.

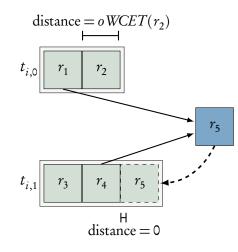

Inside a subsystem of an EMS, a single functionality is encapsulated into a *runnable* [ITE]. For example, one functionality of the subsystem for the injection is to calculate the amount of gas for the combustion. This calculation, i. e., the algorithm, is wrapped in a runnable. Other typical functionalities are the sampling of parameters from the environment or driving actuators. A runnable from the set of runnables  $r \in \mathbf{R}$  is technically an encapsulated portion of sequential code, i.e., a void-void function. Besides the functionality, the characteristic properties of a runnable needed in this thesis are: Maximum sample interval, service, size and the Observed Worst-Case Execution Time

Figure 2.3: Overview of the multitude of diverse systems and their respective connection of an up-to-date Engine Management System for a diesel engine [Rob].

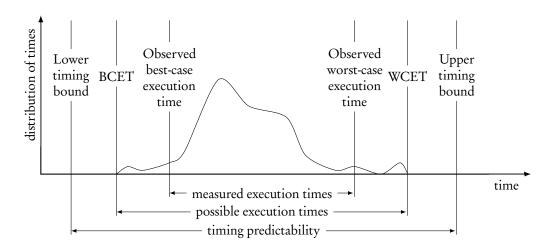

(oWCET). The maximum sample interval is determined by the Nyquist-Shannon sampling theorem [Lun16] and the environment. It is a lower bound for the frequency at which the runnable has to be executed. As a runnable represents a piece of sequential code, instructions in this code can call other runnables. When a runnable is only called from other runnables, it becomes a service. In automotive applications the resulting call hierarchy is limited in depth and recursive calls are typically not allowed. We assume for our purposes that this call hierarchy is flattened. I. e., the size and oWCET aggregate all service runnables that are called inside a runnable. The flattening of the runnable call hierarchy is often done by the compiler. The size of a runnable is the number of bits the runnable occupies in memory. The Observed Worst-Case Execution Time (oWCET) of a runnable denotes the upper bound of a runnable's execution that has been traced or measured. A comparison to the estimated and exact Worst-Case Execution Time (WCET) is illustrated in Figure 2.4. We assume that the execution time bounds of runnables are measured at a certain working point of the ECU and are thus observed bounds. For example, a working point could be a specific number of Rotations Per Minute (RPM) when in mode "driving". The current state of the practice in automotive is that software is typically not designed to allow tight WCET

bounds, due to e.g., different operation points, control strategies and failure modes [BEGL05, MGL06, GE07]. Due to this complexity and the lack of predictable hardware, safe and tight execution time bounds are unavailable.

Figure 2.4: Execution time distribution of runnables with estimated, exact and observed best- and worst case boundaries [WEE+08].

Runnables have no input and output parameters (void-void), but communicate indirectly via *labels*. A label represents a data element in our application model. Labels are used as parameters, temporarily existing variables or represent constants and can be read and written from runnables at any point in time during their execution. A label  $d \in \mathbf{D}$  can be of different data type, e. g., bit, array, or characteristic map and is stored in shared memory. Note that large data types such as a characteristic map are typically read-only and only segments are accessed. Besides the data type, other general properties of a label are: volatile(Boolean), constant(Boolean) and the initial value. Specific for the automotive domain is A2L which describes additional properties of labels for measurement and calibration purposes. The description standard A2L is extensively covered in Section 2.3.1.

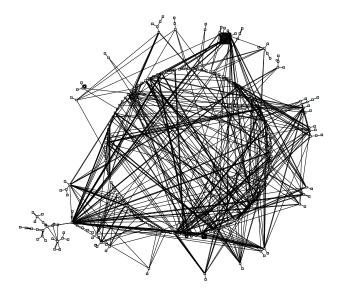

When runnables access a label, these accesses can either be a read or write. Multiple reads or writes are aggregated using statistical values, i. e., how often a read or write is performed. The statistical values are typically extracted from source code using code analysis tools. Hence, when a runnable is executed, a read/write might be performed but does not necessarily have to. In our application model, these label accesses are unordered and do not follow a specific sequence within a runnable. Due to its complexity, automotive applications are highly communicative. Figure 2.5 shows a set of runnables from a real-world EMS, depicted as boxes and their respective communication, depicted as edges. Each edge represents a read-write relationship of two runnables via a label.

**Figure 2.5:** A typical, highly interdependent task with 229 runnables from a realworld automotive application. Each box represents a runnable and each edge a read-write communication via a label.

#### 2.1.2 Real-Time Requirements

In the previous sections we have covered automotive applications in its embedded environment functionality-wise. In addition to the functionality, the timing is an important characteristic for automotive embedded systems. An application interacts with the environment through the hardware and connected peripherals such as sensors and actuators. When interacting, it has to respond to external stimuli within a certain amount of time, known as timing constraints. Thus, the correctness of a response does not depend solely on the correctness of its value, i. e., the logical result, but also on the time at which the value is made available. Responding too late or not at all is as bad as responding with a wrong value. The following definitions are based on Buttazzo's book on hard real-time computing systems [But11]. Buttazzo calls a system a real-time system when it "must react within precise time constraints to events in the environment". These precise time constraints, in the following called real-time requirements, are usually defined through experts of the domain by analyzing the functionality of the system and its environment. As stated before, real-time systems in the automotive domain are typically control systems. Hence, the control applications have to react to the environment ensuring certain real-time requirements. Hereby, a reaction typically implies a functionality that has to be provided to the environment and within the real-time requirements after a stimulus has occurred.

In a real-time system, this functionality is contained in a *task t* from the set of tasks T that is triggered by a stimulus and responds to this input by producing a result in

time. Hence, a task is a container for functionalities, i. e., a set of runnables. A task is an abstract unit of scheduling and executes the containing runnables sequentially. The stimulus that triggers a task is mostly a recurrent stimulus. It could be an interrupt coming from a clock or from connected peripherals. For example, a typical trigger for a task that provides the functionality of sampling a sensor signal is a recurring interrupt from a clock. When and how a task is triggered depends on the control paradigm of the provided functionality. In either way, a task  $t_i \in \mathbf{T}$  that is triggered by a stimulus releases a job  $J_{i,k}$  from an infinite sequence of jobs  $J_{i,k}$ ,  $k \in \mathbb{N}$ .

In automotive applications, tasks are typically recurring in the following way [But11]:

- **Periodic Task:** A periodic task  $t_i$  is cyclically activated with a fixed time interval, the period  $P_{t_i}$ . The task releases jobs  $J_{i,k}, k \in \mathbb{N}$  at a constant interval. Each job  $J_{i,k}$  of task  $t_i$  is activated at  $a_{i,k+1} = a_{i,k} + P_{t_i}$  with  $a_{i,0} = 0$ . In the automotive domain, the periods of the tasks are harmonic, i. e., a task's period is an integer multiple of the period of any other task. A representative example for runnables that are mapped to a periodic task is the sampling of a sensor signal.

- **Sporadic Task:** A sporadic task is activated and releases jobs at a priori unknown times but its activations are separated by a minimum inter-arrival time. An example for runnables that are mapped to sporadic tasks are runnables depending on a specific angle of the crank in an automotive engine.

Our approach is independent of the job release intervals and can thus handle all kinds of tasks (i. e., also aperiodic tasks that release jobs with no pattern and irregularly). In examples and use cases we mainly demonstrate the approach on periodic and sporadic tasks.

Besides the stimuli of tasks and the recurrent creation of jobs, there are also requirements in real-time systems when a task has to respond. As stated before, the correctness of the response from tasks is based on the logical result of the computation and also on the point in time when the response is available. This specific point in time is called a deadline. A task  $t_i$  has a relative deadline  $D_{t_i}$  when a task must be completed and has to provide the desired response. The deadline  $D_{t_i}$  is relative and thus an offset to the activation time of the task  $a_{i,k}$ . Missing the deadline has different consequences and depends on the system and its environment.

In automotive real-time applications, we usually have the following kinds of deadlines [But11]:

**Firm Deadlines:** The response, that is produced after the deadline, is discarded or useless for the system. In automotive applications, sporadic deadline misses are often tolerable [ZH15]. An example is the EMS where e.g., the injection controller maintains stability despite missed deadlines and thus sampling losses due

to the physical inertia of the combustion engine<sup>1</sup>. Systems with firm deadlines are also called weakly hard real-time systems.

**Hard Deadlines:** People are hurt when a deadline is missed. The most widely known example for such requirements is the airbag system. When the deadline of the airbag task is missed, the inflation module cannot provide the cushioning and restraint for the occupants during a crash event.

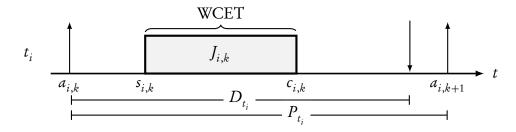

The approach presented in this thesis is applicable to tasks with both kinds of deallines, hard and firm. Also, for our applications we assume constraint deadlines which are typical for automotive systems. In such systems, the relation between the period  $P_{t_i}$  and the deadline  $D_{t_i}$  of a task  $t_i$  is  $D_{t_i} \leq P_{t_i}$ . Figure 2.6 summarizes the notation of the presented real-time properties.

**Figure 2.6:** Real-time properties of a task  $t_i$  with a deadline  $D_{t_i}$  and a period  $P_{t_i}$ . The task is activated at  $a_{i,k}$  and releases a job  $J_{i,k}$  that starts its execution at  $s_{i,k}$  until it is finished at  $c_{i,k}$ .

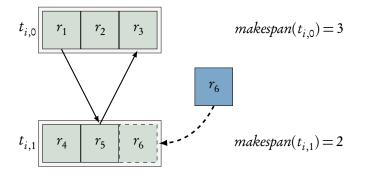

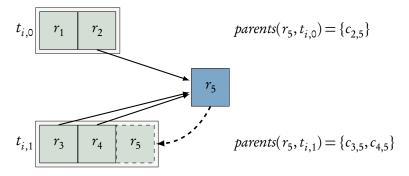

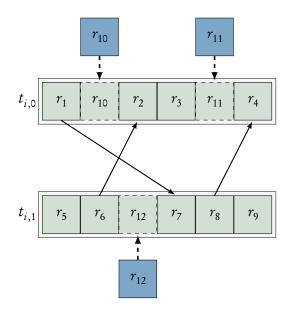

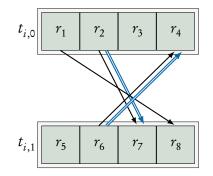

A task  $t_i \in \mathbf{T}$  encapsulates runnables and is an abstract unit of scheduling. Runnables are thus mapped to a task by the function  $m : \mathbf{R} \to \mathbf{T}$ . In the automotive domain there is the established construction principle to map all runnables with the same recurrence pattern to a single task. This is most resource efficient on single-core processors and allows static control of dependencies between runnables with the same recurrence pattern. Inside a task, the runnables are executed sequentially, yet the runnables can be concurrent to each other. Let  $t_i$  be a task, then the order of execution of runnables is defined as the totally ordered set of precedences  $\mathbf{P}(\mathbf{R}_{t_i},\prec)$ . A task can be divided in its structure by remapping the runnables to task partitions. We denote the *j*-th task partition by  $t_{i,j}$  from the set of task partitions  $\mathbf{T}_i$  of a task  $t_i$ . This means that each task  $t_i$  can be splitted into an arbitrary number of task partitions  $\mathbf{T}_i$ . A task partition requires the same properties as the task itself. Hence, each task partition in  $\mathbf{T}_i$  has to have the same recurrence pattern and deadline as the original task  $t_i$ .

Besides being a container for runnables, a task is also the unit of scheduling for the underlying operating system. For automotive systems the operating system is typically

<sup>&</sup>lt;sup>1</sup>Tobuschat et al. [TEHZ16] presented a timing feasibility test that exploits the robustness of control applications.

OSEK-compatible [OSE05]. OSEK (dt. Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug) is a standard for an open-ended architecture for distributed control units, e. g., ECUs in automotive vehicles. Among others, the objective of OSEK is to create independence from the hardware and implementation to provide portability and reusability. The scheduling algorithm provided by the OSEK Operating System (OS) is static, preemptive and uses priorities [ZH15]. In the automotive domain, the priority of a task  $t_i$  is based on the period  $P_{t_i}$  (also called: rate) of the task. The smallest period being the highest priority. This is known as a rate monotonic scheduler. Specifically, the OSEK-compatible operating system for the EMS discussed throughout this thesis uses an (offline) partitioned fixed-priority preemptive scheduling policy with a deadline-monotonic priority assignment scheme.

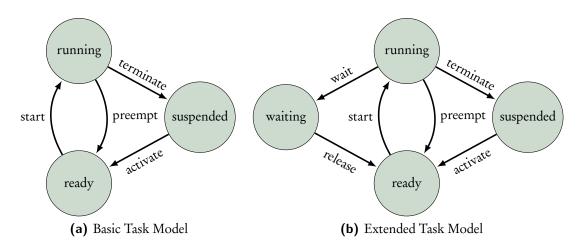

The concept of the OSEK OS knows two different task models for scheduling: The basic and extended task model. The task models differ in the state machine, as illustrated in Figure 2.7. The state machine of the basic task model in Figure 2.7a consists of only three states: running, ready, suspended. When a task is in the state running, the task is assigned to a core and instructions are executed. In the state ready, all functional requirements for running the task are met but another task is assigned to the predestined core, hence it is waiting for a scheduling decision. When a task is not activated, it is in the state suspended. In this task model, a task can never be blocked as there is no waiting state. Thus, it is primarily used for systems or functionalities that have no synchronization or complex I/O. In the extended task model, shown in Figure 2.7b, there are the same three states from the basic task model, plus an additional waiting state. In this state, a task is waiting of at least one event. This task model allows that tasks can be blocked and is hence used for complex systems with interfering resource accesses and communication. There is also an additional overhead when using the extended task model compared to the basic task model due to the event processing feature. It also increases the complexity when developing applications that use the extended task model because applications have to be analyzed for possible deadlocks. These are also the reasons why the EMS is using the basic task model.

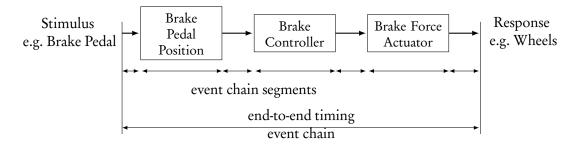

Event chains are another approach to specify and describe real-time requirements. When scheduling real-time tasks and their runnables, there are also real-time requirements that follow the propagation of a signal through the system. A typical example for such a requirement is the braking system with brake-by-wire [BP03]. By law it is required that the actuators for the brakes respond to the brake pedal within a certain timeframe. As there can be many ECUs, subsystems, tasks and runnables between sensing the brake pedal and the actuation for the brakes, these timing requirements have to be specified over a chain of events. These *event chains* allow to specify timing information and requirements on causal loops of events through the system.

Event chains can reference highly diverse events but have to contain at least two of them: the stimulus event and the response event, e.g., a sensor to actor. An event can

Figure 2.7: State machines of the basic and extended task model defined in the OSEK OS in comparison [OSE05].

be the activation or termination of a runnable, it can be an interrupt, or an external stimulus from the driver. But the stimulus is always the first event of an event chain and the response is always the last event. All other events that are defined in between are called event segments and are optional. Event chains can have different end-to-end timing constraints. For example, a reaction constraint or an age constraint. Reaction constraints are one of the most widely used constraints for control systems and define how long after a stimulus a corresponding response must occur with a minimum and maximum value. Figure 2.8 gives an example of an event chain between a sensor and an actuator with a reaction constraint over multiple tasks.

Figure 2.8: Example of a brake-by-wire event chain. A list of event chain segments from a stimulus to a response create an event chain.

Event chains and their corresponding timing constraints can be formally specified using the Timing Augmented Description Language (TADL) (presented in [FRNJ08], specified in  $[C^+09]$ ). Event chains can be modeled on different levels of abstraction,

from the vehicle level to the design level. In this thesis we focus on tasks and hence on event chains on the design level.

#### 2.1.3 Multi-core Platforms

In the beginning of this chapter we argued that the software of automotive embedded systems follows an exponential growth. Modern automotive control algorithms become increasingly complex as a result of more comfort, safety and power-train functionalities. This software has to be integrated into ECUs. Hence, there is an increasing computational demand from the software to the hardware resources of an ECU. Processors in the consumer electronics industry already faced the technology change from single-core platforms to multi- and many-core platforms. This same change in technology is currently challenging the automotive domain [BDN<sup>+</sup>15], delayed due to longer development cycles and certification processes. Although the demand for more computing power has always been there, for consumer electronics as well as for automotive electronics, the boundary conditions for this technology change are different. Still, the primary motivation roots in the physics of our processors. This technology change is often called "the free lunch is over" [Sut05] and essentially describes the upcoming *power wall*. In the automotive context, the power wall (also known as the end of Dennard Scaling) is the main reason why single-core processors cannot reasonably cope with the computational demand. When increasing the clock speed of a processor, power consumption increases as well and leads to an advanced heat generation. Current automotive-grade cooling solutions are not able to dissipate this amount of heat and also the environment around an ECU does not allow advanced cooling mechanisms such as liquid cooling. Processors have to cope with difficult and alternating environment conditions, e.g., high temperature in an engine compartment. This excludes consumer electronics processors with high clock rates to be used in automotive in many cases. Besides that, advanced cooling solutions would be very expensive for automotive grade solutions. Furthermore, as transistors get smaller due to improved manufacturing, power density increases even more. Another way to provide computational power is to support Instruction-Level Parallelism (ILP). In processors of consumer electronics, ILP is a common feature. Yet, ILP increases the processor complexity and thus the power consumption while its performance gains are diminishing.

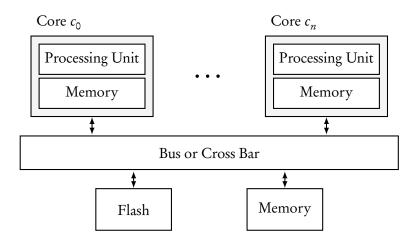

In the following we describe the characteristics of a typical architecture of multi-core platforms for the automotive domain. An automotive multi-core platform typically consists of a number of identical cores that are connected by a common shared resource. In contrast to single-core processors, the architecture of a core on a multi-core platform is much simpler. The cores have short in-order instruction pipelines, a reduced instruction set and preferably no speculative execution. The automotive domain has high predictability requirements and needs guarantees to satisfy timing constraints. Hence, components that improve the average-case performance are generally not integrated into automotive processors [CFG<sup>+</sup>10]. There is typically no hardware prefetching integrated. Prefetchers work in the background, consume interconnection network bandwidth and make latency computation difficult. While prefetching is great from a performance perspective, it should be avoided when deterministic systems are needed as within the automotive domain. Determinism is also the reason why automotive multi-core platforms have no caches or only caches for constants and code. Modern caches are very difficult to analyze due to high associativity and replacement strategies. Also, cache coherence becomes inefficient when the number of cores increases. Hence, a flat cache-less memory hierarchy is typically employed in automotive multi-core platforms which is also attractive when considering chip area and power consumption. However, besides the a processing unit on which a runnable is executed, a core contains also local memory for program code and temporary data. To obtain data from other cores or the global memory and flash, there is a common shared resource which is typically a bus or a cross bar. A bus architecture is often used because the needed chip area is small. In comparison, a cross bar provides a higher throughput but needs more chip area than a bus as it connects all components with each other. This is also the limiting factor when the number of cores increases. Example manufacturer for automotive multi-core platforms used in our EMS case study are JDP and Infineon with 3-6 cores. The block diagram in Figure 2.9 shows the architecture of a typical automotive multi-core platform.

It is important to note that our approach can also be applied to many-core platforms. Many-core platforms bypass the limiting cache-coherence mechanisms by e.g., using core-local memories as scratchpads in conjunction with a Network-on-Chip. Although the interconnect is different to multi-core platforms, its influence to our method is negligible.

**Figure 2.9:** Block diagram of a typical automotive multi-core platform consisting of *n* cores, flash, memory and a bus or cross bar.

#### 2.1.4 Model of Computation and Communication

As automotive control software is highly communicative, there is a tight link between the computation and communication. Especially the communication timing and its effect on control applications is of interest to us. While the runnables inside tasks encapsulate the functionality and hence the computational part, the communication between runnables always takes place indirectly via labels. There are two kinds of communication among runnables that any communication semantic of a Model of Computation (MoC) has to address. This semantic depends on the task the runnables are mapped to. When a runnable communicates to another runnable inside the *same* task it is called *intra-task* communication. When a runnable communicates to another runnable inside a *different* task it is called *inter-task* communication.

The most widely-used and established communication semantic in automotive is Last Is Best (LIB). LIB relies on the fact that all communication between runnables goes through labels that are shared in global memory. The data that is written to a label is available globally as soon as the writing instruction has finished. In other words, while a task is executing a set of runnables, the values of labels change continuously. Hence, by writing to a label its new value is immediately available to all other runnables as well as reading a label always transfers the latest values from shared memory. This applies to intra-task as well as to inter-task communication. The advantage of LIB is that it has generally short latencies after being optimized for the given platform. LIB was originally used and still is for applications running on single-core platforms. On multi-core platforms, this communication concept has some consequences.

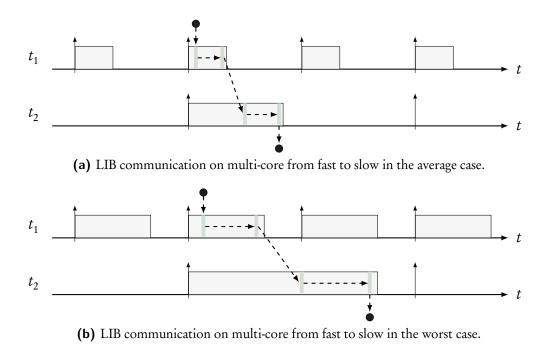

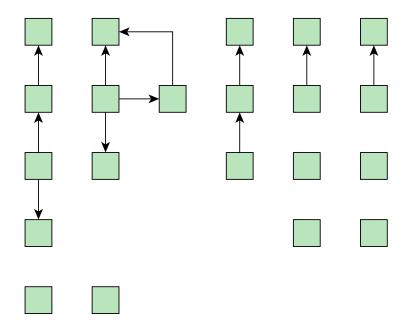

The consequence of LIB on multi-core platforms is that runnables get *either* stale data (or there are even sampling losses) or fresh data. This communication semantic is not deterministic and depends on the distribution scenario, workload and order of execution inside a task [ZH15]. Figure 2.10 illustrates two cases on a multi-core platform in which runnables of a fast task  $t_1$  communicate with runnables of a slower task  $t_2$  using the LIB semantic under different workload scenarios. The figure shows that the point in time where the communication is executed is dependent on the execution time of the runnables and hence the task. In the average case, the communication of both tasks is executed within the period of task  $t_2$  while in the worst case it takes almost twice the time. The drawback is that controllers have to be designed to cope with different timeliness of the data. Controllers have to be tested if they are stable and adhere to required performance criteria (e.g., robustness). Such a controller design is costly in terms of development effort and resource efficiency. For example, controllers would need to run at a higher rate to be stable enough. Also, data consistency has to be enforced by critical sections due to concurrent accesses from different cores. These sections have to be added manually and can lead to race conditions.

In contrast to LIB, the concept of Logical Execution Time (LET) [HHK01] provides a deterministic communication semantic among runnables in tasks. The advantage

**Figure 2.10:** LIB communication on multi-core platforms from fast to slow tasks under different workload scenarios. The runnables indicated as green boxes communicate inside a task as well as across tasks. The communication between runnables is illustrated as a dashed arrow, start and end of all communication is depicted as black dots.

of Logical Execution Time (LET) is that its read and write semantic enforces a deterministic data exchange, for single- and multi-core platforms. As stated before, this is a very useful property for designing and composing control software<sup>2</sup>. The described communication semantic is also known as Timed Implicit Communication in the AU-TOSAR environment [KQnBS15]. In the concept of LET, the same result/response is produced from the same input/stimulus independent of distribution, workload, or task execution timing (meaning e.g., the offset). Hence, LET can provide task-level determinism and guaranteed data consistency<sup>3</sup>. The benefit of LET is that it enables portability and allows to map tasks to different cores under the assumption that the WCET of a task is less than its LET interval [GSVK<sup>+</sup>06]. The only drawback is that the communication latency is fixed to the worst-case of LIB.

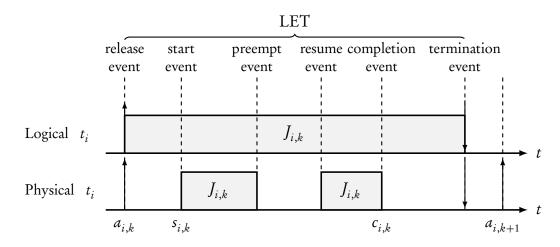

LET as used for deterministic multi-core platforms in the automotive domain separates the computation from the communication. The logical specification of a LET task consists of the following [GSVK<sup>+</sup>06]:

<sup>&</sup>lt;sup>2</sup>Presented at the Embedded Multicore Conference (EMCC) by Jochen Haerdtlein

<sup>&</sup>lt;sup>3</sup>The data consistency is dependent on the implementation of the copy operation at release and termination event.

- A sequential piece of code that has its own local memory space.

- A set of program variables (input variables), i. e., the labels that are read by the task.

- A set of program variables (output variables), i. e., the labels that are updated by the task.

- Some timing constraints, i. e., a release event and a termination event.

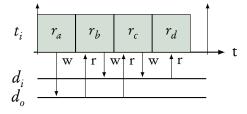

While the program variables are accessible by any task and thus global, the local memory space of a task is only accessible by itself. The timing constraints define the LET of a task, cf. Figure 2.11. Within the LET interval, a task can start later than the release event, complete before the termination event and can be preempted and resumed at any time inbetween. When a LET starts (the release event), all program variables that are input variables are read from global memory and copied to the local memory of the task. Likewise, at the end of a LET (the termination event), the program variables in the global memory are updated by the state of the output variables in local memory of the task. The process of copying the program variables to and from the global memory happens in logical zero time.

Figure 2.11: Definition and notation of a task's Logical Execution Time in relation to its physical execution.

In case of intra-task communication, the runnables simply read and write to and from the program variables located in the task's local memory. Within the task's LET this altered data is only available to the task itself.

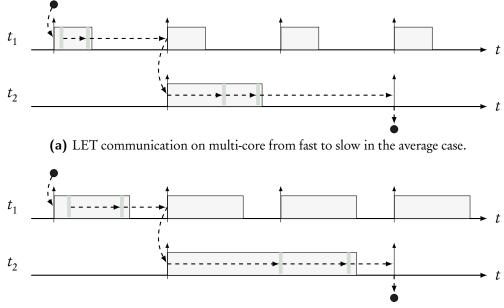

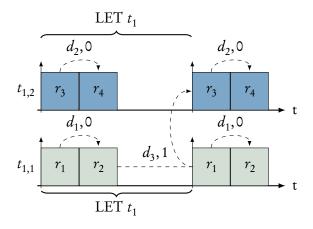

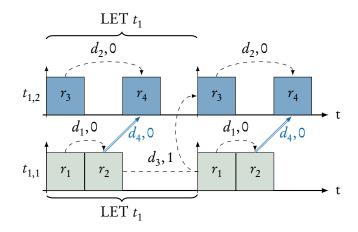

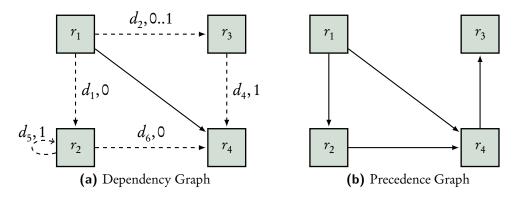

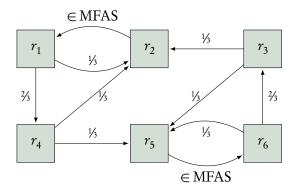

The inter-task communication between jobs happens logically instantaneous at fixed points in time: at the beginning and end of each LET. Figure 2.12 shows two cases on multi-core platforms under different workload scenarios that follow the LET semantic when communicating. In both cases the boundaries represent the beginning and end of a LET for the corresponding task. At each write, the label is only altered in the local memory of the task. As soon as the LET is finished the global memory is updated with the state of the local memory of the task. At this point in time, the altered values of the labels are available to other tasks. Figure 2.12 also illustrates that this behavior is independent of the workload.

(b) LET on multi-core from fast to slow in the worst case.

Figure 2.12: LET communication on multi-core platforms from fast to slow tasks under different workload scenarios. The runnables indicated as green boxes communicate inside a task as well as across tasks. The LET interval of a task is the time between subsequent activations. The communication is illustrated as a dashed arrow, start and end of all communication is depicted as black dots.

For our approach we use LET as a model of computation and communication with the following notation, cf. Figure 2.11. Let  $t_i$  be a task with a deadline  $D_{t_i} = P_{t_i}$ , then for a job  $J_{i,k}$ , the LET starts with its activation  $a_{i,k}$  and ends latest with the next activation  $a_{i,k+1}$ . For tasks with a constraint deadline  $D_{t_i} \leq P_{t_i}$  holds and the termination event is the deadline  $D_{t_i}$ . For our approach, the point in time when updates of program variables are made is highly important, i. e., when the updated labels are available and to whom they are available. We call this point in time the publication event.

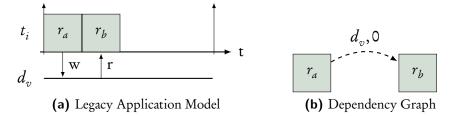

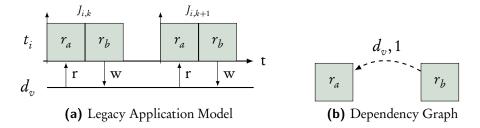

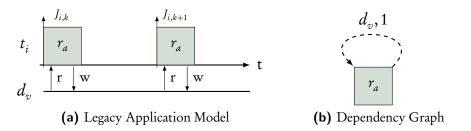

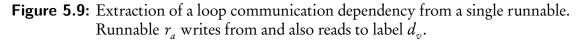

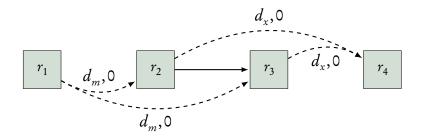

For intra-task communication the communication is defined as follows. Let m be a mapping such that runnables  $r_a$  and  $r_b$  are mapped to the same task  $m(r_a) = t_i$ ,  $m(r_b) = t_i$  and runnable  $r_a$  writes to label  $d_v$  that is read by runnable  $r_b$ . I. e.,  $r_a$ communicates with  $r_b$  and  $r_a \prec r_b$ . In this case, as soon as runnable  $r_a$  finished writing to label  $d_v$  in the task's local memory, the updated value of  $d_v$  is immediately available to  $r_b$  and all other runnables that precede  $r_a$  within the task. The updated value of  $d_v$ is published during the execution of  $r_a$  to all runnables  $r_k \in \mathbf{R}_{t_i}, r_a \prec r_k$ . For runnables that precede runnable  $r_a$  in the job instance  $J_{i,k}$ , the updated value is available in the following job instance  $J_{i,k+1}$ . This is similar to the inter-task communication, which we explain in the following.

The inter-task communication with LET is defined in the following way. Let m be a mapping such that runnable  $r_a$  is mapped to producer task  $m(r_a) = t_p$  and runnable  $r_b$  to consumer task  $m(r_b) = t_c$ . Also, runnable  $r_a$  writes to the label  $d_v$  that is read by runnable  $r_b$ , i. e.,  $r_a$  communicates with  $r_b$ . Again, we assume harmonic periods, i. e., the period of one task is always an integer multiple of the period of any other task. As soon as runnable  $r_a$  finishes writing to label  $d_v$ , only the corresponding program variable located in the task's local memory contains the updated value of  $d_v$ . This value is published instantly at the earliest of the termination event of the producer task  $t_p$ . Hence, the updated value is available to  $r_b$ , all following jobs  $J_{p,k+1}$  of the same task and all other runnables outside the producer task  $t_p$ .

As already mentioned, LET fixes the communication latency to LIB worst-case. Hence, the transition from LIB to LET introduces a delay in communication for most cases. When doing such a transition, the application has to be checked for increased latencies that exceed the worst-case scenario of the LIB implementation or affected critical paths that do not allow additional latencies. Our approach is based on applications that are fully transitioned to LET. We assume that all additional latencies, critical paths, or event chain constraints have been checked and do not violate any requirements of the system.

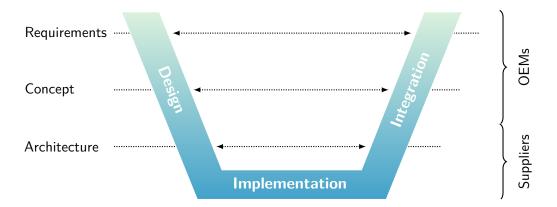

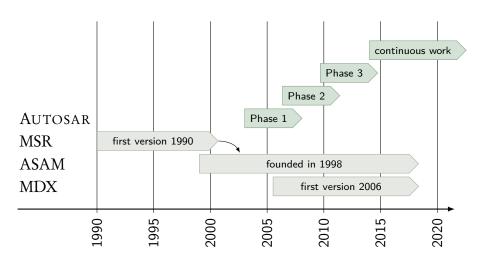

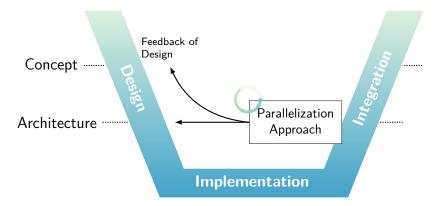

#### 2.2 Software Development Process

In the automotive industry, the development of systems, hardware and software typically follows the V-model [SZ16]. The V-model [KKuBdBfIidB98] is a phase-based development process model and an extension of the waterfall methodology. It is defined in multiple standards that differ in abstraction and domain e.g., ISO 12207, V-Modell 97, V-Modell XT. The idea of the V-model is the separation of the specification, implementation and integration phases, cf. Figure 2.13. The model requires that results of a phase are complete before entering the next phase. For example, the requirements of design or architecture clearly have to be defined before going into the next phase, the implementation. Hence, the V-model only defines activities and results and excludes the order of the activities. The V-model is also divided by layers such that each phase during the specification has its counterpart within the same layer during integration. For example, for the architecture design there is the counterpart that provides unit-tests during integration.

The benefit of the V-model is that it improves the process of planning the development with its clear process lifecycle. This is especially important for the automotive industry with its heavy supply chain. Figure 2.13 shows the V-model when developing a car. The Original Equipment Manufacturers (OEMs) are typically responsible for the top layers of the V-model and set up the requirements for a car and integrate the products from the suppliers, while the suppliers are responsible for the bottom layers of the V-model. The phases of the V-model can also be aligned to other major standards, e. g., Automotive SPICE, the domain specific variant of the ISO/IEC 15504 standards to assess the development process. Besides the OEMs, also the suppliers typically use the V-model can be used for various products that are integrated by the OEM. In fact, the V-model can be used for various products and in different shapes and sizes. When focusing on a single ECU, the development process follows the Double-V-Model having one development process for the hardware part of the product and one for the software part. In this approach we refer to the V-model as the software development process of an ECU application.

#### 2.2.1 Model-based Development

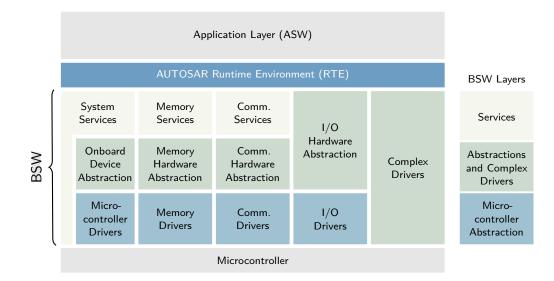

As the systems and software of ECUs in the automotive domain gain more and more complexity over the last decades, so has the process of developing these systems. In the early days, these systems were developed within the domain of mechanical engineering. Today, automotive systems development is a highly interdisciplinary challenge at a unique complexity level. In the previous sections we showed that standards such as AUTOSAR can contribute and ease the system development by abstraction and au-

**Figure 2.13:** Example of a simple V-model for the development of a car that is devided into design, implementation and integration [SZ16].

tomation. Another concept that targets the problem of efficient systems development is the model-based approach. The model-based approach also abstracts and automates the systems' development process, ideally to cope with complexity. And because of its benefits, model-based development has become a standard methodology in the automotive industry [BKK<sup>+</sup>13]. Modeling aims at improving the effectiveness of engineering by using models as important artifacts in the development process and not solely for documentation purposes. Modeling enables early verification and validation activities on various stages which reduces costs, supports generation of lower-level artifacts (e. g., source code) and can be used for communication with other multidisciplinary stakeholders [SZ16].

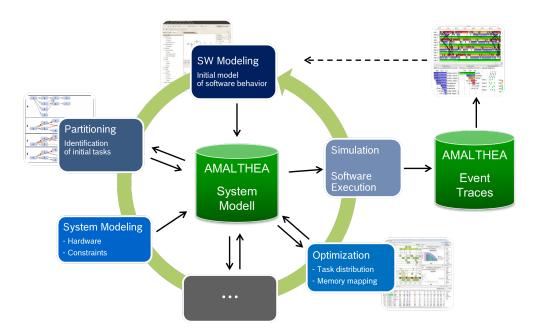

AMALTHEA [ITE] is a tool platform for embedded multi- and many-core software systems engineering. It is an ITEA2 funded project, created in 2013, and primarily focuses on, but not limited to, automotive systems. The main goal of AMALTHEA is to enable efficient software engineering especially for multi-core platforms. As a model-based development platform, it promotes and simplifies data exchange in cross-organizational projects. Figure 2.14 illustrates this benefit. Complex tool chain elements such as simulation and validation can be managed easily. Hence, products and knowledge from tool vendors and other suppliers can be integrated efficiently. This allows to explore the decision space extensively and to support decisions in designing automotive systems with accurate information [WKH<sup>+</sup>15].

The AMALTHEA system model contains information on the software, hardware, timing behavior and constraints for the embedded system under development. It hereby extends AUTOSAR by dynamic architecture details. AMALTHEA and AUTOSAR share the same concept of tasks, runnables, components and interfaces, yet with a different implementation. Also events, event chains and timing constraints are implemented in both platforms as they share a common origin.

#### 2.2.2 Legacy Software

Since the beginning of E/E (electric/electronic) systems in cars, embedding additional systems with software has been a major trend for the automotive industry. While the number of individual systems and ECUs has increased, also the communication infrastructure had to grow with it. In 2010, innovations in the form of electronics and software inside an automotive are at a staggering 90 % [Fü10]. Premium-class cars integrate close to one hundred million lines of code in 2009 [Cha09]. Whereas a low-end car already embeds 30–50 ECUs, a premium-class car consists of up to 70 ECUs that are connected via 5 different system busses [Fü10]. When focusing on a single ECU, the automotive supplier Bosch has been experiencing a 15 % increase of load per year in an ECU for an EMS on average. This number is obviously depending on the project and segment, but the increase in software on ECUs is nevertheless steady and significant. However, decades of ECU software development have also left a huge amount

**Figure 2.14:** Model-based development using the AMALTHEA platform [ITE]. The common AMALTHEA system model is the foundation for all activities on the model.

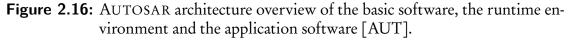

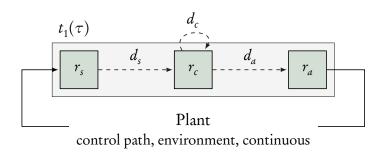

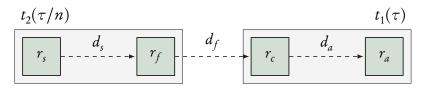

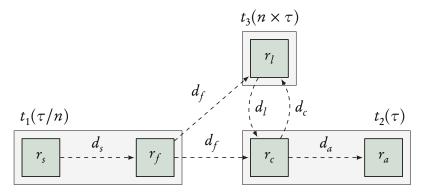

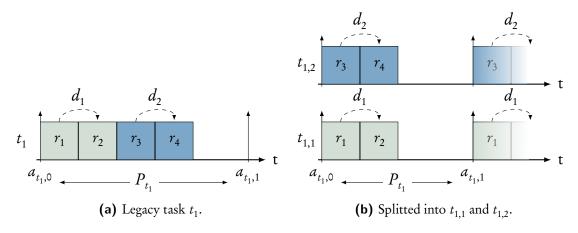

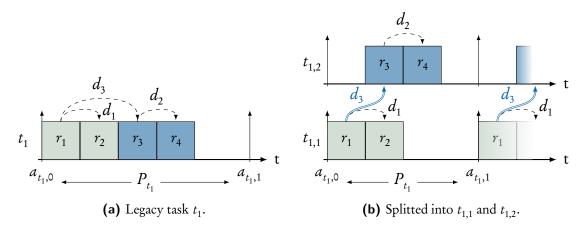

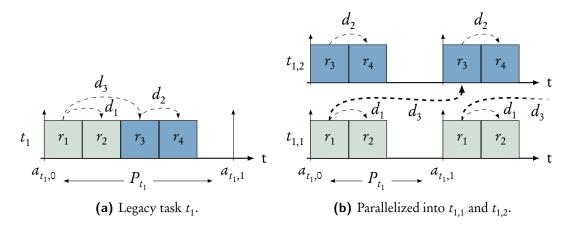

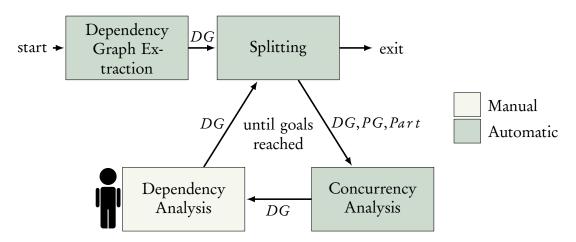

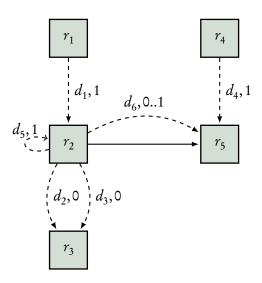

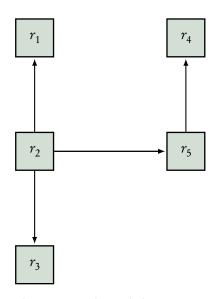

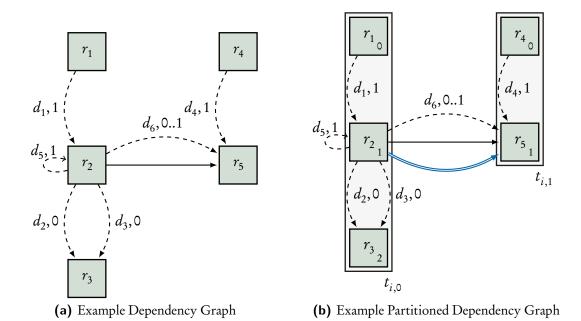

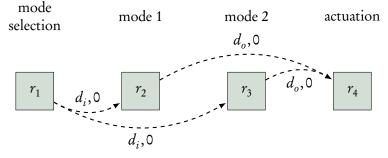

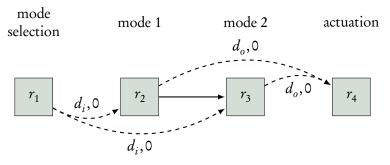

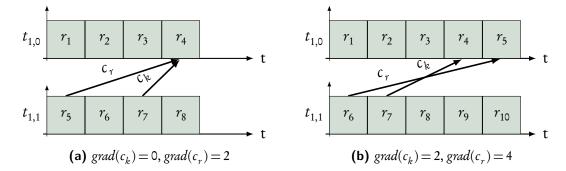

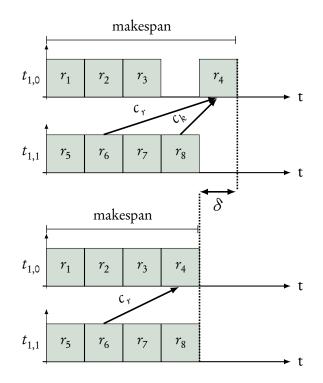

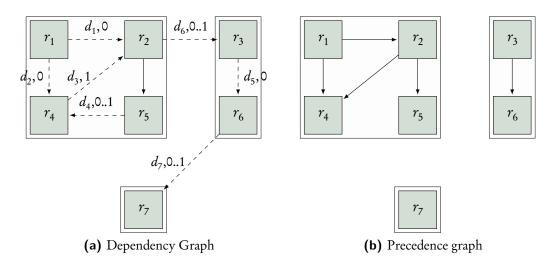

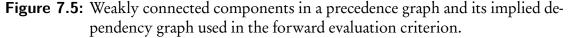

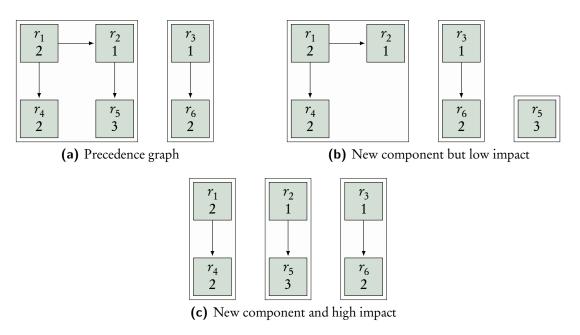

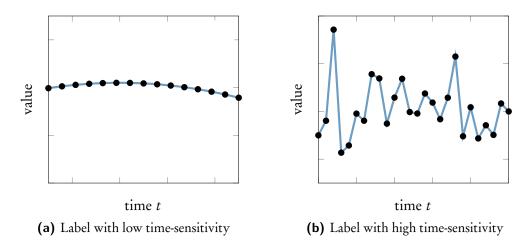

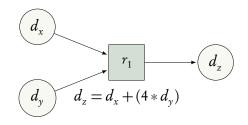

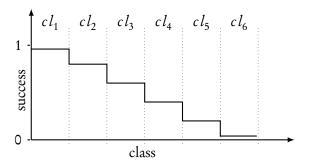

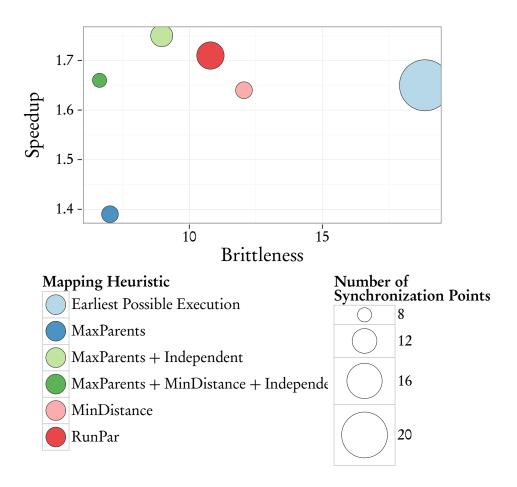

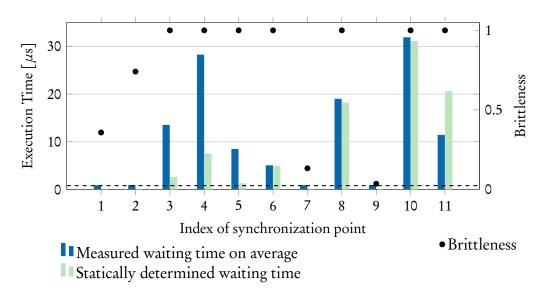

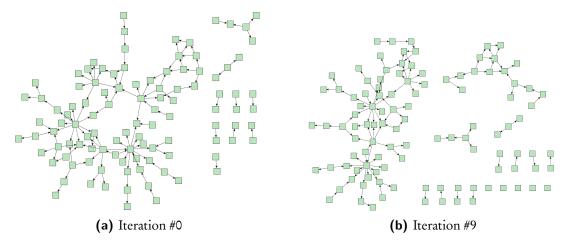

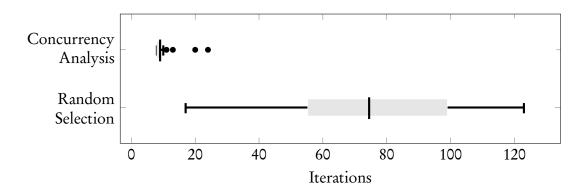

of legacy software. This legacy software is built for single-core platforms and cannot be executed on multi-core platforms without issues. It needs to be migrated to multicore platforms. Yet, a complete redesign and reengineering of the legacy software for multi-core platforms is prohibitive due to cost and time-to-market reasons. The transition from single-core to multi-core platforms also carries a paradigm change which we explain in the next paragraph.