# GPU Power Modeling and Architectural Enhancements for GPU Energy Efficiency

vorgelegt von Dipl.-Ing. Jan Lucas geb. in Berlin

von der Fakultät IV - Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften - Dr.-Ing. -

genehmigte Dissertation

# Promotionsausschuss:

Vorsitzender: Prof. Dr. Thomas Sikora

Gutachter: Prof. Dr. Ben Juurlink

Gutachter: Prof. Dr. Henk Corporaal

Gutachter: Prof. Dr. Jean-Pierre Seifert

Tag der wissenschaftlichen Aussprache: 7. Dezember 2018

Berlin 2019

# CONTENTS

| ΑB | STRA | CT vii                                                 |

|----|------|--------------------------------------------------------|

| ZU | SAMI | menfassung ix                                          |

| PR | E-PU | BLISHED PAPERS Xİ                                      |

| 1  | INTI | RODUCTION 1                                            |

|    | 1.1  | GPU Architecture and Programming Model 1               |

|    | 1.2  | (GP)GPU History 3                                      |

|    | 1.3  | GPGPU Applications 5                                   |

|    | 1.4  | GPU Power Consumption 5                                |

|    | 1.5  | GPU Power Measurement and Modeling 6                   |

|    | 1.6  | GPU Architectural Enhancements for Energy Efficiency 6 |

|    | 1.7  | Research Questions 7                                   |

|    | 1.8  | Thesis Structure 8                                     |

| 2  | GPU  | ARCHITECTURE 11                                        |

|    | 2.1  | Programming Model 11                                   |

|    | 2.2  | Top-Level Architecture 14                              |

|    | 2.3  | GPU core datapath & register file 15                   |

|    | 2.4  | Memory interface 18                                    |

|    | 2.5  | Warp Control Unit 20                                   |

|    | 2.6  | DRAM Interface 23                                      |

|    | 2.7  | Summary 26                                             |

| 3  | REL  | ATED WORK 27                                           |

|    | 3.1  | GPU Architecture 27                                    |

|    | _    | Power Measurement 28                                   |

|    |      | Architectural GPU Power Modeling 28                    |

|    | 3.4  | Data-Dependent Power Modeling 30                       |

|    | 3.5  | Optimal DBI Encoding 31                                |

|    | 3.6  | Sparkk 32                                              |

|    | 3.7  | Temporal SIMT and Spatio-Temporal SIMT 33              |

|    | 3.8  | Scalarization 35                                       |

| 4  | GPU  | POWER MEASUREMENT 37                                   |

|    | -    | Power Measurement Concept 37                           |

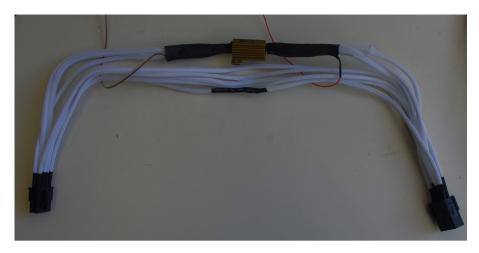

|    | 4.2  | LPGPU1 Testbed 38                                      |

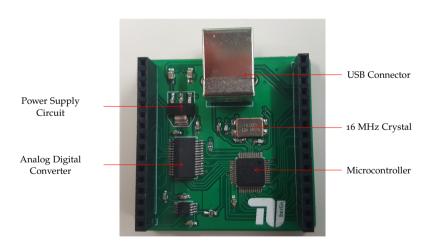

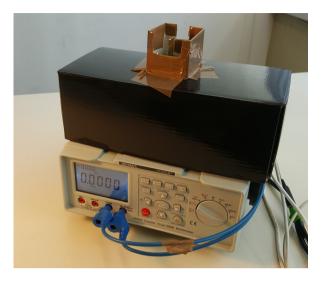

|    |      | 4.2.1 Analog to Digital Conversation 40                |

|    |      | 4.2.2 Insertion of Current Shunts 41                   |

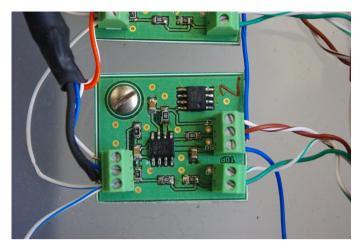

|    |      | 4.2.3 Signal conditioning 42                           |

|    |      | 4.2.4 Software 44                                      |

|    | 13   | LPGPU2 Testhed 40                                      |

|   |            | 4.3.1 LPGPU2 Testbed Hardware 50                        |

|---|------------|---------------------------------------------------------|

|   |            | 4.3.2 LPGPU2 Testbed Firmware Programming and Calibra   |

|   |            | tion 52                                                 |

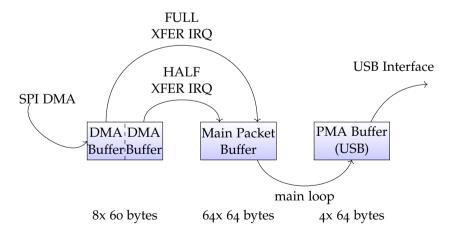

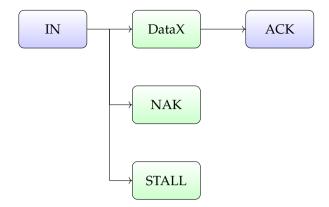

|   |            | 4.3.3 Microcontroller Firmware 52                       |

|   |            | 4.3.4 Host Software 55                                  |

|   |            | 4.3.5 Android Software 55                               |

|   |            | 4.3.6 Summary 55                                        |

| 5 | ARC        | HITECTURAL GPU POWER MODELING 57                        |

|   | 5.1        | THE CONTROL OF THE I                                    |

|   |            | 5.1.1 Overview 59                                       |

|   |            | 5.1.2 Power Model 60                                    |

|   |            | 5.1.3 Modeled Architecture 61                           |

|   |            | 5.1.4 Deriving Power Empirically 66                     |

|   | 5.2        | Experimental Methodology 67                             |

|   |            | 5.2.1 Measurement Equipment 68                          |

|   |            | 5.2.2 System Configurations 68                          |

|   |            | 5.2.3 Benchmarks 69                                     |

|   | 5.3        | P. I.                                                   |

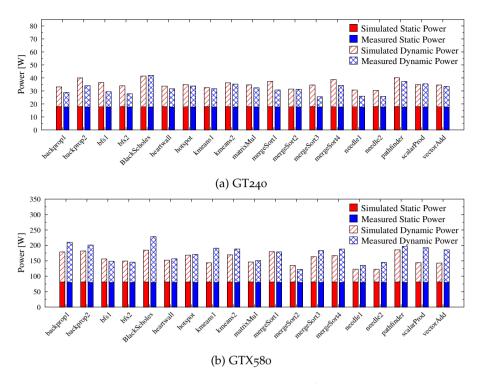

|   |            | 5.3.1 Simulated and Measured Power 71                   |

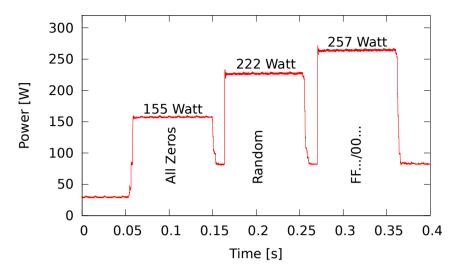

|   |            | 5.3.2 Power Profiling 72                                |

|   | 5.4        | Summary 74                                              |

| 6 | DAT        | A-DEPENDENT ALU POWER MODELING 75                       |

|   | 6.1        |                                                         |

|   | 6.2        | Experimental Methodology 81                             |

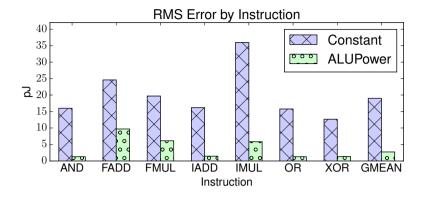

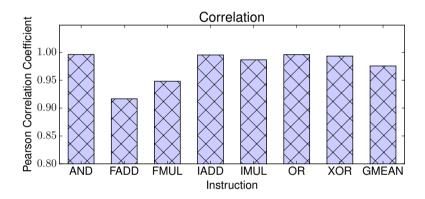

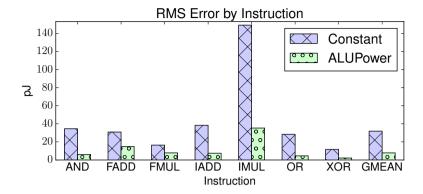

|   | 6.3        | Experimental Results 83                                 |

|   |            | 6.3.1 Data-Dependent Power Consumption on Fermi and     |

|   |            | Maxwell 83                                              |

|   |            | 6.3.2 Impact of Register File 85                        |

|   | <i>(</i> . | 6.3.3 Energy Consumption per Instruction 88             |

|   |            | ALU Energy Model 88                                     |

|   |            | Accuracy 97                                             |

|   | 6.6        | Summary 99                                              |

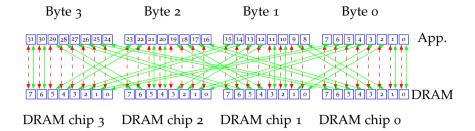

| 7 |            | A-DEPENDENT MEMORY MODELING 101                         |

|   | 7.1        | Experimental Setup 102                                  |

|   | 7.2        | Memory Layout 103 Data-Dependent Energy Consumption 106 |

|   | 7.3        | 1 0, 1                                                  |

| 2 | 7.4        | Summary 113                                             |

| 3 |            | Ontimal Engading                                        |

|   | 8.1        | Optimal Encoding 117                                    |

|   | 8.2        | Experimental Setup 119                                  |

|   |            | 8.2.1 Power Model 119                                   |

|   |            | 8.2.2 Hardware 120                                      |

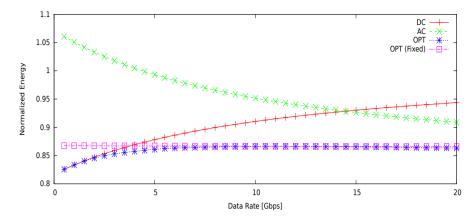

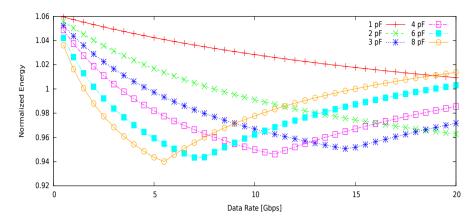

|    | 8.3  | Results 123                                           |

|----|------|-------------------------------------------------------|

|    | 8.4  | Summary 125                                           |

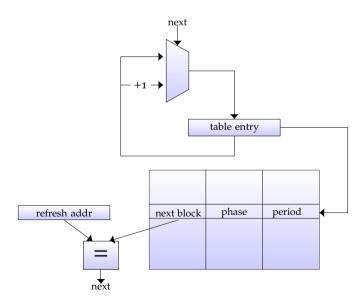

| 9  | SAVI | NG DRAM REFRESH POWER 127                             |

|    | 9.1  | Approximative Storage 128                             |

|    | 9.2  | Sparkk 129                                            |

|    |      | 9.2.1 Sparkk Storage 129                              |

|    |      | 9.2.2 Controlling the refresh 131                     |

|    |      | Modeling of Sparkk 133                                |

|    | 9.4  | Evaluation 135                                        |

|    | 9.5  | Summary 137                                           |

| 10 | SPAT | TIO-TEMPORAL SIMT 139                                 |

|    | 10.1 | A Temporal SIMT GPU Architecture 142                  |

|    |      | 10.1.1 TSIMT Cores and Lanes 142                      |

|    |      | 10.1.2 Control Divergence 144                         |

|    |      | 10.1.3 Instruction Issue 145                          |

|    |      | 10.1.4 Memory Access Coalescing 146                   |

|    |      | 10.1.5 Shared Memory 146                              |

|    |      | 10.1.6 Latency Hiding 147                             |

|    |      | 10.1.7 Register File 147                              |

|    |      | 10.1.8 Area 149                                       |

|    | 10.2 | Experimental Evaluation 150                           |

|    |      | 10.2.1 Experimental Platform and Benchmarks 150       |

|    |      | 10.2.2 Synthetic Benchmark Analysis 152               |

|    |      | 10.2.3 Full Benchmark Analysis 156                    |

|    |      | 10.2.4 Load Balancing Issues 158                      |

|    |      | 10.2.5 Register Allocation Optimizations 159          |

|    |      | 10.2.6 TSIMT Design Tradeoffs 161                     |

|    |      | 10.2.7 Spatio-Temporal SIMT 162                       |

|    | -    | Summary 163                                           |

| 11 |      | LARIZATION 165                                        |

|    |      | Hardware Support for Scalarization 166                |

|    |      | Compiler Scalarization Algorithm 166                  |

|    | _    | Implementation of the Scalarization Algorithm 167     |

|    | •    | Scalarization Results 169                             |

|    | -    | TSIMT+Scalarization 170                               |

|    |      | Power and Energy 172                                  |

|    |      | Summary 173                                           |

| 12 |      | CLUSIONS & FUTURE WORK 175  Conclusions 175           |

|    |      | Conclusions 175 Answers to our Research Questions 180 |

|    |      | Future Work 181                                       |

|    | 12.3 | ruture WOIK 101                                       |

#### ABSTRACT

Graphics Processing Units (GPUs) can now be found in nearly every PC and smartphone. Initially designed for 3D graphics, they evolved into general purpose accelerators, able to outperform CPUs on many tasks. The architecture of GPUs is optimized for massively parallel applications. This reduces the required control logic but also results in lower performance in applications with irregular control flow. The energy per instruction is often lower in GPUs than in CPUs, but due to their high throughput, discrete GPUs can still use 200 W and more. GPU performance is limited by power consumption, as the power dissipation at higher speeds would exceed the cooling abilities. Better energy efficiency does not only extend battery life and reduce power bills but also enables higher performance.

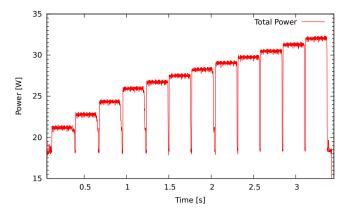

To increase the energy efficiency, we measure and model the energy consumption of existing GPUs. A custom GPU power measurement infrastructure and an architectural power simulator called GPUSimPow are described and evaluated. Due to the lower control overhead in GPUs, accurately modeling the power consumption of the memory interface and execution units is important. Regular architectural simulators do not model the data-dependent energy consumption but assume that energy consumption per operation does not depend on the data. We show that this assumption is not true, but that GPU power consumption can vary by more than 60% with different data and present two data-dependent power models.

Afterwards, we focus on architectural enhancements to improve the energy efficiency. Two techniques focus on the memory interface: A novel approximation technique reduces the DRAM refresh energy and an optimized encoding scheme reduces the power consumption of the external interface between GPU and DRAM by up to 6%. We continue with enhancements to improve the energy efficiency of the GPU cores. We evaluate an alternative to the conventional SIMT GPU architecture called temporal SIMT (TSIMT) and extend it to spatiotemporal SIMT. Temporal SIMT makes the execution of code with irregular control flow more efficient but can reduce the performance of applications by decreasing the ability of the GPU to tolerate memory latency. Spatiotemporal SIMT provides a good combination of conventional SIMT and TSIMT. In both architectural variants so-called Scalarization can be used to remove redundant operation. We show that spatiotemporal SIMT with Scalarization improves the energy-delay product by 26.2% compared to conventional GPUs.

# ZUSAMMENFASSUNG

Graphics Processing Units (GPUs) sind heute Teil nahezu jedes PCs oder Smartphones. Ursprünglich für 3D Grafik entwickelt, wurden sie zu allgemein nutzbaren Beschleunigern weiterentwickelt, die viele Aufgaben schneller als CPUs erfüllen. Ihre Architektur ist optimiert für massiv parallele Anwendungen. Dies reduziert die nötige Kontrollogik, aber senkt auch die Rechenleistung bei uneinheitlichem Kontrollfluss. Pro Instruktion verbrauchen GPUs oft weniger Energie als CPUs, aber durch ihren hohen Durchsatz, können sie trotzdem 200 Watt und mehr verbrauchen. Die Rechenleistung wird dabei von der elektrischen Leistungsaufnahme beschränkt, weil bei höhren Geschwindigkeiten die Kühlung überfordert würde. Eine höhere Energieeffizienz führt daher nicht nur zu einer verlängerten Batterielaufzeit und geringeren Energiekosten, sondern ermöglicht auch höhere Rechenleistung.

Um die Energieeffizienz zu erhöhen, messen und modelieren wir zunächst den Energieverbrauch existierender GPUs. Eine speziell angepasste Meßinfrastruktur und ein architekturelles Powermodell namens GPUSimPow werden vorstellt und getestet. Der geringe Kontrolloverhead in GPUs macht die genaue Modellierung der Energie von Speicherinterface und Ausführungseinheiten besonders wichtig. Gewöhnliche Architektursimulatoren modellieren keinen datenabhängigen Energieverbrauch, sondern nehmen einen konstanten Energieverbauch pro Operation an. Wir zeigen, das diese Annahme nicht zutrifft und der Energieverbrauch der GPU sich durch andere Daten um mehr als 60% erhöhen kann und präsentieren zwei datenabhängige Powermodelle.

Anschließend zeigen wir Verbesserungen der GPU Architektur zur Erhöhung der Energieeffizienz. Zwei Techniken setzen am Speicherinterface an: Eine neuartige Näherungstechnik reduziert den Energieverbrauch des DRAM Refresh und ein optimiertes Kodierungsverfahren reduziert die Energie der Schnittstelle zwischen GPU und DRAM um bis zu 6%. Danach verbessern wir die Energieeffizient der GPU Kerne. Wir untersuchen "temporal SIMT" (TSIMT), eine Alternative zu konventionellen SIMT GPU Kernen und erweitern es sie zu "spatiotemporal SIMT" (STSIMT). TSIMT ermöglicht eine effektivere Ausführung von Programmcode mit uneinheitlichem Kontrollfluss, reduziert aber auch die Möglichkeiten der GPU Speicherlatenzen zu tolerieren. STSIMT ist eine gute Kombination von konventionellen SIMT mit TSIMT. In beiden Architekturvarianten kann Skalarisierung verwenden werden, um redundante Operationen zu vermeiden. Die Kombination von STSIMT mit Skalarisierung kann das Energie-Verzögerungs-Produkt um 26.2% gegenüber einer konventionellen GPU verbessern.

#### PRE-PUBLISHED PAPERS

Parts of this thesis are based on the following pre-published papers.

#### **IOURNAL**

J. Lucas, M. Andersch, M. Alvarez-Mesa, and B. Juurlink, "Spatiotemporal SIMT and Scalarization for improving GPU efficiency," *ACM Transactions on Architecture and Code Optimization*, vol. 12, no. 3, 32:1–32:26, Sep. 2015, ISSN: 1544-3566. DOI: 10.1145/2811402

#### CONFERENCE

- J. Lucas, S. Lal, M. Andersch, M. Alvarez-Mesa, and B. Juurlink, "How a single chip causes massive power bills GPUSimPow: A GPGPU power simulator," in *Proceedings of the International Symposium on Performance Analysis of Systems and Software (ISPASS)*, IEEE, 2013. DOI: 10.1109/ISPASS.2013.6557150 © 2013 IEEE

- J. Lucas and B. Juurlink, "ALUPower: Data dependent power consumption in GPUs," in *Proceedings of the International Symposium on Modeling, Analysis and Simulation of Computer and Telecommunication Systems (MASCOTS)*, IEEE, 2016. DOI: 10.1109/MASCOTS.2016.21 © 2016 IEEE

- J. Lucas, S. Lal, and B. Juurlink, "Optimal DC/AC data bus inversion coding," in *Design, Automation and Test in Europe, DATE*, EDAA, 2018. DOI: 10.23919/DATE.2018.8342169

#### WORKSHOP

J. Lucas, M. Alvarez-Mesa, M. Andersch, and B. Juurlink, "Sparkk: Quality-scalable approximate storage in DRAM," in *The Memory Forum*, 2014

# INTRODUCTION

Today GPUs can be found in nearly every personal computer as well as in devices such as smartphones, gaming consoles or tablets. GPU stands for Graphics Processing Unit, but their usage is not limited to graphics anymore, instead, GPU serve as general purpose Turing-complete computing devices. They are able to outperform CPUs on many tasks. CPUs and GPUs complement each other and are now often integrated into a system on a chip (SoC).

This chapter provides an introduction for the thesis. We start with a high-level overview of the architecture of GPUs and their programming model. We then provide a short history of GPUs and their usage for non 3D graphics applications, the so-called general purposed GPU computing or short GPGPU. The thesis continues with an overview of current usages of GPGPU computing. We then explain the issues caused by GPU power consumption and why measuring and modeling the GPU power consumption is important and continue with a discussion of architectural enhancements for improved energy efficiency. The main research questions of this thesis are formulated in Section 1.7. We conclude this introduction with an overview of the structure of this thesis.

# 1.1 GPU ARCHITECTURE AND PROGRAMMING MODEL

GPUs complement CPUs because their architecture focuses on the effective execution of algorithms that are embarrassingly parallel and offer high levels of data parallelism. High performance CPUs use large parts of their area and power budget for complex control logic that enables OutOfOrder execution and for large caches. These design choices enable high performance execution of single-threaded code, but due to the complex logic and high power consumption, only a few of these cores fit on the silicon die. Embarrassingly parallel algorithms execute well on GPUs, as they do not require high single threaded performance. GPUs remove large caches and simplify the control logic and add a higher number of cores and very wide SIMD (Single Instruction Multiple Data) execution units per core. This results in a slow execution speed of each thread but if a high number of threads runs

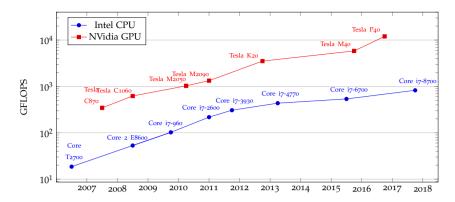

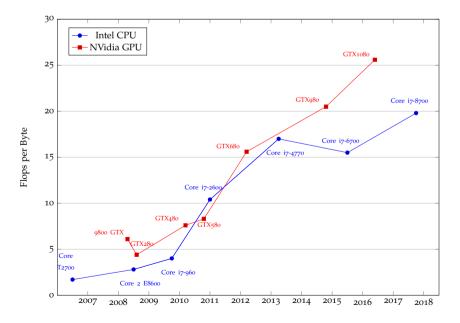

Figure 1.1: CPU vs. GPU Peak Performance

in parallel, GPUs can reach a very high throughput, one or even two orders of magnitude above CPUs. This difference in peak performance can also be seen in Figure 1.1. It compares the peak performance of high performance NVIDIA GPUs with high performance Intel CPUs over time. The difference in peak performance is not due to better process technology nor clock speed. NVIDIA GPUs typically are one or two process nodes behind Intel CPUs and clock speeds are significantly lower. Despite executing their instruction using SIMD execution units, GPUs are typically programmed using SPMD (Single Program Multiple Data) programming models. This programming model is often easier to use for programmers than directly using very large masked SIMD instruction but allows GPUs to amortize the cost of instruction fetch, decoding and scheduling over groups of threads called warps (NVIDIA) or wavefronts (AMD). If all threads in a warp follow the same control flow, the full throughput of the SIMD execution units can be utilized. If the control flow of the threads within a warp differs, the control flow is serialized and the execution units are only partially active. This is also called control flow divergence and results in a reduced throughput. NVIDIA coined the term SIMT (single instruction multiple threads) for this programming model that executes using SIMD execution units but mostly looks like programming independent scalar threads to the programmer. The execution model is efficient as long as control flow divergence is rare, however, with more complex and irregular applications running on GPUs the control flow often becomes divergent and performance, as well as power efficiency, is reduced. As kernels executed on the GPU get increasingly more complex, this problem becomes more important.

The high performance of GPUs in many applications would not be possible without the development of special high bandwidth memories. GPUs use special memory technologies such as GDDR5/5X and HBM/HBM2 that focus

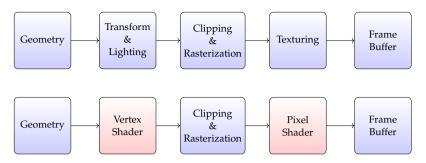

Figure 1.2: 3D Graphics Pipelines

on very high bandwidth while accepting their higher cost and smaller density compared to mainstream CPU memory technologies such as DDR3 and DDR4.

# 1.2 (GP)GPU HISTORY

GPUs evolved out of fixed function 3D graphics accelerators. The top of Figure 1.2 shows a simplified, typical 3D pipeline. 3D geometry as triangles is ingested into the pipeline at the start, the geometry is then rotated and translated to a specific viewpoint. Lighting information is calculated and a perspective transform is applied. Clipping removes triangles and parts of triangles that are outside of the viewing area. Rasterization breaks the triangles down into individual pixels. Finally, texturing applies a wrapped image ("texture") to these pixels. In the first 3D accelerators only parts of this pipeline were present. Evans and Sutherland's Picture System [1] from 1974 employed a vector display that used the electron beam to directly draw lines to the screen and was used to draw wire-frame graphics only. Lighting, Rasterization, and Texturing were not required in such a system. SGI's IRIS systems were early systems that implemented nearly the whole pipeline, albeit without texturing. These early systems employed complex designs using many chips. The geometry engine was built from one the first VLSI chips. Twelve of these chips were combined to implement  $4 \times 4$  matrix multiplication, clipping and scaling to the display coordinates [2]. SGI's IRIS systems were also very influential in regards to the programming interface to the 3D hardware. They introduced the IRIS GL API which would later evolve into the OpenGL standard. These early systems were very expensive high-end systems or workstations. In 1989 Namco released their "System 21" arcade system board [3] that employed hardware accelerated polygonal 3D graphics for entertainment in video game arcades. In the 1990s accelerated 3D graphics arrived in mainstream PCs and video game consoles. One of the first successful 3D accelerator for PCs was the 3Dfx "Voodoo" accelerator. It focused

on texture mapping and used the PC CPU for calculating the perspective transformation and set up the triangle rasterization engine on each triangle. Similar to the old high-end 3D accelerators a multi-chip design was employed. One chip was used for texturing while the other chip handled the framebuffer and the PCI interface. NVIDIA's Geforce 256 included hardware support for transform and lighting [4]. NVIDIA coined the term "Graphics Processing Unit" (GPU) for this design launched in late 1999 [5]. It combined transform and lighting, triangle setup and texturing into a single chip. However, these first GPUs had little in common with today's GPGPU as they were restricted fixed-function units, designed for a single task. Demand for more realistic graphics resulted in more flexibility being added in the next few generations of GPUs. NVIDIA's Geforce 3 GPUs supported vertex- and pixel shaders: Small programs running on the GPU to control the transformation of the scene and the shading of each pixel. In the beginning, these shaders were severely limited in their capabilities. Only short shaders with a few instructions were possible and the control flow was restricted. Later generations lifted these restrictions. These early GPUs also employed different hardware units (shaders) for vertex and pixel calculations. Vertex transformation and lighting calculation were performed using floating point arithmetic while pixel shaders often used lower accuracy fixed-point arithmetic. The Xbox 360 was the first gaming console utilizing unified shaders that are used to execute both pixel and vertex shaders [6]. Research showed that this leads to higher performance and better area efficiency and adds the flexibility to efficiently render scenes with varying pixel and vertex shader workload balances [7].

As early as 2004 people started applying GPUs to regular computing tasks such as sorting numbers or linear algebra tasks using APIs intended for 3D graphics [8]. The use of GPUs for general-purpose computing purposes is often called general-purpose computing on graphics processing units or short GPGPU. APIs tailored towards GPGPU such as Brook for GPUs, NVIDIA's CUDA and OpenCL from Khronos Group helped to kick-start a wide adoption of GPUs for computing [9], [10].

GPUs were especially successful as accelerators for high-performance computing. At the end of 2010 three out of first seven supercomputers with more than 1 petaflops utilized GPUs [11]. GPUs performed well especially in terms of energy efficiency and at the end of 2011, almost all the Top 30 slots of the Green 500 list of the most power efficient supercomputers used GPUs [12].

GPUs are now ubiquitous, not just in HPC, desktop PCs and laptops but also in smartphones, tablets and gaming consoles. Even on these low power, mobile platforms GPUs are not only employed for rendering 3D graphics but also to perform GPGPU workloads such as neural network interference [13], [14], face recognition [15] or image processing [16].

#### 1.3 GPGPU APPLICATIONS

GPU have also been popular for the so-called "mining" of cryptocurrencies, as they greatly increased the hashrate compared to CPUs. Before the availability of FPGA and ASIC based mining devices, GPU quickly replaced CPUs for bitcoin mining [17]. Newer cryptocurrencies such as Ethereum employ proof-of-work function specifically engineered to be GPU friendly [18]. The popularity of GPU mining resulted in strong demand for GPUs and pushed up AMD's share price [19].

An even more important market for GPUs is artificial intelligence (AI) and in particular, "deep learning". In 2009 Raina et al. demonstrated a speedup of 70× by using GPU for training a large scale deep neuronal network [20]. Various artificial intelligence frameworks such as Theano [21], Tensorflow [22], Torch [23] and Caffe [24] support GPU acceleration. In 2013 Coates et al. showed how to train very large network using 12 GPUs while previously training a similar network at the same speed required 16000 CPU cores [25]. In parts of the training, each GPU exceeded 1 TFlops in application performance. Mayor cloud computing platforms such as Amazon Webservices, Google Cloud Platform, and Microsoft Azure now offer virtual machines with GPUs and often advertise GPUs for artificial intelligence applications [26]–[28]. AMD offers GPUs specifically aimed at the AI market [29] and NVIDIA added special execution units called tensor cores to some of their GPUs that provide even higher throughput for some linear algebra operations common in AI [30].

# 1.4 GPU POWER CONSUMPTION

Especially in these battery-powered devices, power consumption is an important topic for the design of GPUs. High GPU energy consumption would cause a short battery life. At the same time, energy conservation applies and the energy consumed by the GPU is turned into heat. This heating is often an issue, even when battery life is not a concern. Many mobile GPU containing devices have relatively direct contact to the skin of its user and must limit their surface temperatures to 45°C or less [31]. This limits the possible power consumption of the GPU even further. GPU performance is limited by the maximum possible power dissipation is not limited to mobile devices. Even the performance of discrete desktop GPUs with an elaborate active cooling system is often limited by the maximum possible power dissipation. The used semiconductor technology would allow the use of higher frequencies but running at these frequencies would cause the GPU to quickly exceed the maximum allowed temperature. GPUs now often employ "boost clocks" several 100 *Mhz* above their base frequency. These boost clocks allow the

GPU to run at a higher frequency if the workload has a low average power consumption. This happens, e.g.: if the workload is concentrated into short peaks with gaps in between where the GPU is able to cool down again or if the workload does not fully utilize the GPU. Another issue directly linked to power consumption is power delivery. Current desktop GPUs can easily use more than  $250\,W$  and at the same time they utilize core voltages only slightly above  $1\,V$ . This can result in currents of  $200\,A$  and more. At these extremely high currents even tiny resistances can easily cause significant voltage drops [32].

#### 1.5 GPU POWER MEASUREMENT AND MODELING

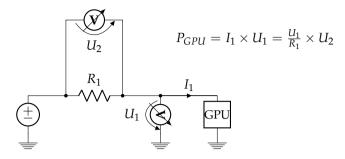

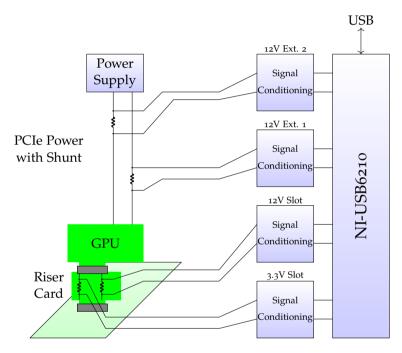

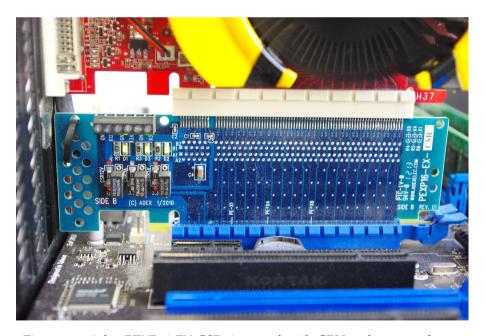

In order to understand the power consumption of GPUs, we need to measure and model the power consumption. Discrete GPUs are plugged into a computer system and they receive power via the PCIe slot and also via additional power cables. In this thesis, we developed power measurement testbeds that allow us to measure the power consumption of GPUs.

We can, however, only measure existing GPUs and can only measure the power consumption of the whole GPU, but cannot measure the power consumption of individual GPU components within an application. However, to improve the power efficiency we need to be able to estimate the power efficiency of modified (and potentially improved) GPU designs and gain insight into the power consumption of the individual components. This thesis presents an architectural power simulator along with two improvements. The power simulator allows us to estimate the power consumption of a GPU workload. The configuration of the GPU can be determined using a configuration file. Performance and energy benefits of architectural enhancements can estimated by implementing the proposed changes in the simulator.

#### 1.6 GPU ARCHITECTURAL ENHANCEMENTS FOR ENERGY EFFICIENCY

Measuring and modeling the energy consumption of GPUs is the first step to increase the energy efficiency of GPUs. But what concrete architectural enhancements are possible for improving the energy efficiency? Many proposals can improve the performance of GPUs, but cause an even stronger increase of the power consumption and reduce the energy efficiency of the GPU.

#### 1.7 RESEARCH QUESTIONS

In this thesis, we aim to answer to following research questions:

- (A) How can we measure the power consumption of GPUs and kernels running on GPUs?

- (B) How can we estimate the power consumption using an architectural simulator?

- (C) Can architectural enhancements improve the energy efficiency of GPUs?

Each of these three broad main research questions, generates multiple more detailed questions. For power measurements, we need to answer to following questions:

- $(A_1)$  How can we acquire high quality GPU power measurements?

- $(A_2)$  How can power measurements be combined with application level event information?

In terms of power estimation and modeling, our main questions are:

- (*B*<sub>1</sub>) Can an architectural simulator predict the power consumption of a GPU from its architectural level configuration?

- (*B*<sub>2</sub>) How to design microbenchmarks to measure the power consumption of individual GPU components?

- (*B*<sub>3</sub>) How can microbenchmarks and power measurements be used to discover unpublished architectural details?

Regarding architectural enhancements, we ask our self the following questions:

- (C<sub>1</sub>) Which GPU components can we change to improve the power consumption?

- (C<sub>2</sub>) Can enhancements that improve performance, but also increase power consumption still result in gains in energy efficiency?

- (C<sub>3</sub>) What kind of architectural enhancements will increase the applicability of GPUs for new applications and still improve energy efficiency?

We provide detailed answers to these questions in the individual chapters of this thesis and a summary in Chapter 12

#### 1.8 THESIS STRUCTURE

After this introduction, the thesis starts in Chapter 2 with a detailed look at GPU architecture with a focus on NVIDIA GPUs. Chapter 3 continues with an overview of the related work.

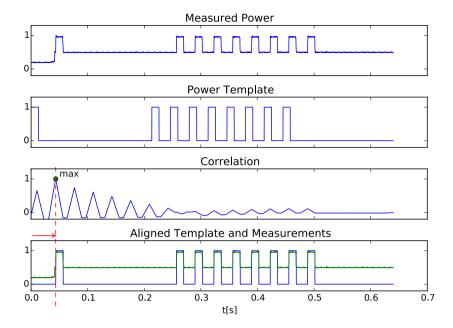

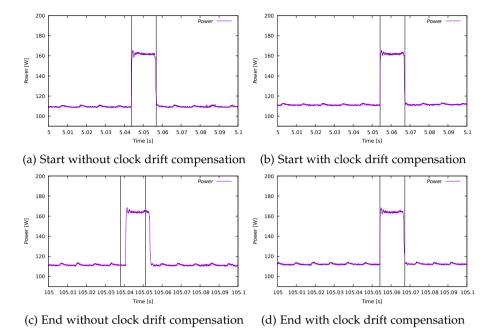

We aim to improve the power efficiency of GPUs, but before we can start to improve the power efficiency, we first need to understand the power consumption of existing GPUs. We need to be able to measure it and have models that allow us to break down the power consumption into individual parts. In Chapter 4, we describe the requirements for our measurement infrastructure, as well as the development of custom hardware for fast and accurate measurements of the power consumption of both GPUs and System on Chips (SoCs) containing (mobile) GPUs. The chapter also describes, how the raw measurement data can be processed, in order to measure the energy consumption of events such as GPU kernel executions.

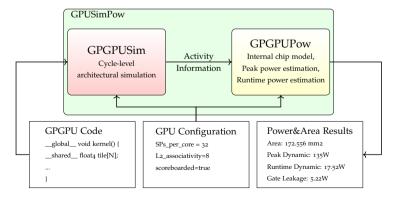

Chapter 5 describes the development and validation of the initial GPUSim-Pow power model. It is based on a combination of architectural modeling as well as measurement-based models. The measurement infrastructure from the previous chapter is used to validate the model as well as for the development of some models.

In Chapter 6, we refine the model by taking data values into account. In this chapter, we show that processed data values significantly influence the power consumption of the GPU and describe a model to accurately estimate the power consumption of the ALUs based on the processed data.

Another refinement is presented in Chapter 7. Here we present an extension to the GPUSimPow model that also considers the effect of data values during memory access.

Armed with the knowledge gained by investigating and modeling the power consumption of GPUs, we developed various optimizations to the GPU architecture that aim to improve the energy efficiency. We start with two chapters describing how the memory and memory interface could be made efficient. Chapter 8 describes an improved encoding scheme for the data transfer between GPU and DRAM, that is able to reduce the power consumption of the interface by up to 6%. The next Chapter describes a technique that reduces the refresh power of DRAM using approximation. This is especially important for mobile applications as refresh power is even consumed while CPU and GPU are in a sleep state.

After we have proposed multiple optimizations of the memory interface we look at the main GPU architecture and try to improve its power efficiency. We start by making the execution of divergent workloads more efficient. In Chapter 10 of this thesis, we look at an alternative GPU architecture called spatiotemporal SIMT, that is able to execute code with branch divergence both faster and more efficiently.

Chapter 11 explains an additional technique called Scalarization. The use of SIMD units and an SPMD programming model often leads to redundant calculations as the threads of a warp often perform calculations with identical inputs and outputs. This leads to a higher power consumption as a calculation is performed 32 times instead of once when each warp consists of 32 threads and it also leads to an inefficient use of the register files, as the results need to be stored for each thread instead of storing the results just once per warp. Scalarization aims to reduce these redundant calculations and stored values. The chapter presents a novel algorithm to identify scalar instructions as well as scalar values in regular GPU kernels automatically and details how Scalarization can easily be integrated into spatiotemporal SIMT and evaluates the performance as well as energy efficiency benefits of Scalarization on this GPU architecture.

Finally, the thesis concludes with Chapter 12. An overview of the results of this thesis is provided, conclusions are drawn and an outlook into research directions for the future is provided.

After this overview of the thesis structure, this chapter ends and we continue the thesis with an overview of GPU architecture in the next chapter.

# GPU ARCHITECTURE

This chapter provides an overview of current GPU architecture. It focuses on the GPU architectures used by NVIDIA and AMD, as those are the two biggest vendors of discrete desktop GPUs. Less information is available regarding the architecture of embedded mobile GPUs. However, small versions of NVIDIA's Kepler and Maxwell GPU cores were employed in the Tegra SoCs. Different vendors and programming standards employ different terms for the same parts of GPU architecture. This thesis mostly follows the terminology used by NVIDIA's CUDA programming model. This chapter starts in Section 2.1 with a discussion of the programming model employed for (GP)GPU programming. Section 2.2 continues with a top level overview of NVIDIA and AMD GPUs. The core data path and the GPU register file is discussed in Section 2.3. In the following Section 2.4, the GPU memory interface within each core is examined. Section 2.5 delves into warp scheduling and the warp control unit. The DRAM interface is explored in Section 2.6. Finally, a short summary is provided in Section 2.7.

#### 2.1 PROGRAMMING MODEL

GPUs are programmed either with 3D graphics APIs or GPGPU computing APIs. Common 3D graphics APIs are OpenGL (ES), DirectX or Vulkan. Recent version of these API also contain interfaces for GPGPU computing. GPGPU computing uses APIs such as OpenCL or CUDA. In this thesis, we focus on GPGPU computing.

OpenCL and CUDA offer a single program multiple data (SPMD) programming model. In this programming model, the same program is executed on multiple data items, if possible in parallel. As the programming model allows for parallel execution of the different data items but does not require parallel execution, the same program can be executed on different GPUs with different numbers of parallel execution units and the parallelism can be adjusted to match the capabilities of the hardware. CUDA is limited to NVIDIA GPUs, however, OpenCL is an open standard supported on a wide range of GPUs, GPUs, FPGAs and other accelerators. The support of multiple architectures in OpenCL comes at a price: OpenCL is often more limited in capabilities

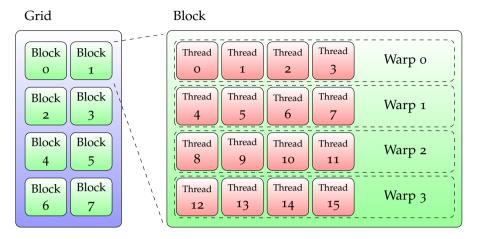

Figure 2.1: Thread Hierarchy in CUDA and OpenCL

than CUDA, because it needs to be efficiently executable on a wider range of architectures and thus can only implement features that can be executed efficiently on all supported platforms.

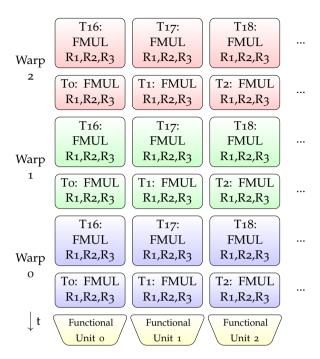

Both OpenCL and CUDA avoid explicitly launching single threads. Instead, a grid¹ of threads is launched. This concept is further illustrated in Figure 2.1. The grid is composed out of smaller blocks. The total number of threads launched per grid is *blocks* × *threads per block*. The threads within one block are running in parallel on the same GPU core. The threads from different blocks, however, can be executed in parallel or sequentially depending on the available GPU resources. To execute the threads within each block GPUs use a combination of data level parallelism (DLP) and thread level parallelism (TLP). Each block is broken down into groups of threads called warps. NVIDIA uses 32 threads per warp and AMD uses 64 threads per warp in their GCN architecture and calls them wavefronts.

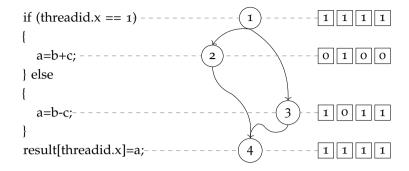

These warps are executed using SIMD execution units. Despite execution on SIMD units, each thread in the warp is (almost) able to follow its own control flow as if they would be completely independent threads. NVIDIA and AMD GPUs, however, maintain only one program counter (PC) per warp and use predicated execution, an active mask and a special stack to maintain the illusion of independent thread within each warp. NVIDIA calls this execution model Single Instruction, Multiple Threads (SIMT). Figure 2.2 provides a short example of divergent branch execution with SIMT: On the left, the figure shows a small CUDA example, the middle shows the corresponding control flow graph and on the right, the active mask is displayed. The first line is executed on all threads, the active mask is thus one for all threads.

<sup>&</sup>lt;sup>1</sup>Grid is CUDA terminology, NDRange is the equivalent term in OpenCL

| Step | PC / | Mask | Stack      | Comment             |

|------|------|------|------------|---------------------|

| 1    | 1 /  | 1111 | empty      | Divergent Branch    |

| 2    | 2 /  | 0100 | [3 / 1011] |                     |

| 3    | 4 /  | 0100 | [3 / 1011] | Reconvergence Point |

| 4    | 3 /  | 1011 | empty      |                     |

| 5    | 4 /  | 1011 | empty      | Reconvergence Point |

| 6    | 4 /  | 1111 | empty      |                     |

Figure 2.2: SIMT execution with Reconvergence Stack

When the branch is executed, first the taken path is executed [33] and the not taken path is pushed to the reconvergence stack [34]. When node 2 is executed, only thread 1 uses the taken path, and only thread 1 is enabled in the active mask. Node 4 is called the reconvergence point. It is the immediate post-dominator of our branch node 1. A post-dominator of a specific node is a node where every path that passed through the node is also guaranteed to pass by [35]. Node 4 is also the immediate post-dominator of node 1, the first node that is a dominator of node 1. When the control flow from node 2 reaches the reconvergence point at node 4, it switches the current PC and active mask to one stored on the top of the reconvergence stack. Node 3 is then executed on all threads but thread 1 and when the reconvergence point is reached again, execution continues for all threads. While the SIMT execution relies on hardware support, it relies on compiler support as well. The reconvergence points are identified at compile time and some branches are replaced by predicated instructions.

AMD uses a slightly different approach: Instead of maintaining a dedicated hardware stack, the stack is stored in regular registers. Always executing taken branch first can require up to one entry per thread in the stack for nested branches. AMD reduces the number of stack entries needed by always executing the path with fewer (or equal) active threads first [36]. With this optimization, each time a new stack entry is pushed to the stack, the number of active threads is at least halved. When only a single thread is active,

Figure 2.3: GPU Architecture Overview

divergent branches are not longer possible and no deeper reconvergence stack entries can be created. After the GPU has executed the path with fewer active first and has reached the reconvergence point, the stack entry is removed. Remembering the already executed path is not required and thus does not require a reconvergence stack entry. As AMD uses a warp size of 64 threads, this limits the maximum number of stack entries to  $log_264 = 6$  which is significantly lower than the 64 entries that would be required without this optimization.

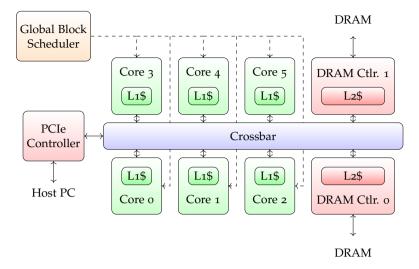

#### 2.2 TOP-LEVEL ARCHITECTURE

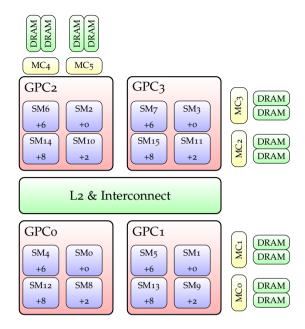

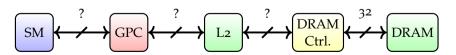

A high-level overview of a typical GPU architecture is shown in Figure 2.3. Several cores, in this example six, are connected to a crossbar that links the cores to the memory controller and PCIe controller. Each core contains a small L1-cache and each memory controller contains a part of the L2-Cache. Both NVIDIA and AMD report thousands of cores in their documentation, e.g.: Geforce GTX1080 GPU is reported to have 2560 "CUDA Cores" and the Radeon RX Vega 64 spots 4096 "stream processors". However, these cores do not feature the elements normally expected in a core, e.g.: they do not have their own control logic or caches. Each of these "cores" is a single precision floating point ALU. Together with the clock frequency can be used to calculate peak single precision flops. In this thesis core refers to what NVIDIA calls "streaming multiprocessor" or AMD calls "compute unit" (CU): Mostly self-contained cores with multiple floating ALUs configured as one or multiple

Figure 2.4: GPU Datapath [39] © 2016 IEEE

SIMD execution units, the required interface to the memory interconnect and various caches. AMD's RX Vega 64 contains 64 of these compute units and NVIDIA's GTX1080 contains 20 "streaming multiprocessors" (SM). Each SM contains 128 single precision floating point ALUs and each of the CUs contains 64 floating point ALUs in their SIMD units.

Outside the of the cores, a global block scheduler distributes new work to the cores if both additional work and enough resources on the core are available. GPGPU-sim models this scheduler as a simple round-robin scheduler, however, the actual behaviour is slightly more complex and has advantages in terms of locality [37], [38]. The PCIe controller allows DMA transfers and direct access from the host PC memory to the GPU DRAM. It also enables the host PC to submit new work to the GPU and query the execution status of already submitted work.

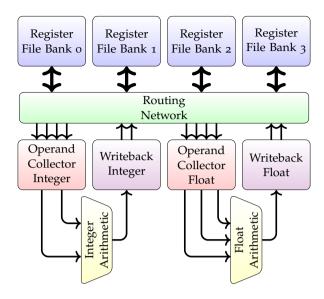

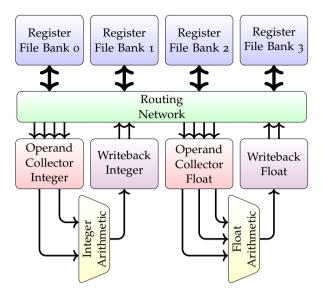

#### 2.3 GPU CORE DATAPATH & REGISTER FILE

A simplified GPU data path is shown in Figure 2.4. While CPUs often used multi-ported memory for register file to allow fetching several operands in the same cycle, GPUs often used several register banks with only one or two ports each. Typical GPUs are required to store the register content of a high number of threads. Often hundreds or thousands of threads per core. As each thread typically uses 16 to 128 32-bit registers, this results in a requirement of several MB or at least hundreds kB storage in the register files. The total amount

of storage in the register files of a GPU can reach more than 10 MB [40]. Typically, GPUs do not use a fixed number of architectural registers but can configure the numbers of registers per thread within a certain range such as 32 to 128 registers. While the total amount of registers per core is fixed, this flexibility allows developers to trade a higher number of registers per threads for a lower number of active threads or vice versa. It is often assumed that code with a higher number of active threads (also called occupancy) enables higher performance. However, in some applications using more registers per thread can enable code that exhibits more ILP. This can lead to a higher performance, even with a smaller number of active threads [41]. Autotunning can be used to find the optimal trade-off between the number of registers per thread and the number of concurrent threads [42].

As multi-ported memory requires large amounts of area per storage bit, GPUs simulate multi-ported memory by using several banks of memory with only one or two ports each and sequentially fetch the required operants over multiple cycles. Several possible variants of this technique are explained an NVIDIA patent [43]. An operand collector collects the operands required for each instruction over several cycles and stores them until all operands for one instruction are available. When all operands are collected, the instruction will be issued to the execution unit. In the example shown in Figure 2.4 four register file banks are used. A routing network, e.g. a crossbar, connects the register file banks to the operands collectors. The number of register file banks and the ports per register file determine, how many operands can be read and written from the register file in each cycle. This requires that the operands are evenly distributed to all register file banks. Different schemes with various advantages and disadvantages exist to map registers from the individual threads to different register file banks. As the GPU register file only simulates multi-ported memory but is not a truly multi-ported register file, all mapping schemes can yield an effective register file bandwidth significantly below the peak register file bandwidth, if the requested operands are not evenly distributed to the banks.

As the register file uses a significant part of the area and power budget of a GPU, many authors have described improvements to reduce the area and/or power consumption of the register file. Wing-Kei et al. proposed the use of a hybrid SRAM-DRAM register file [44], other authors proposed the use of STT-RAM [45] or racetrack memory [46]. Gebhart et al. proposed the use of multi-levels of compiler managed register file caches [47] and unifying the register file with the first level cache and shared memory [48]. NVIDIA's Volta architecture uses small compiler managed register caches [49]. Lee et al. proposed the use of compression to increase the effective size of the register file [50].

In the figure, two execution units are shown, an integer arithmetic unit and a floating arithmetic unit. Several common executions units are not

Figure 2.5: Fermi Datapath [39] © 2016 IEEE

shown in the figure. A load/store unit provides the interface to the memory interface, it will be discussed in Section 2.4. GPUs commonly also provide execution units, often called special function units (SFU), for more complex functions such as trigonometric functions, reciprocals or square root. These SFUs were designed for use in graphical applications and are fast but often do not provide full single precision accuracy. They are used via special intrinsics or via a -use\_fast\_math compiler flag that trades accuracy for speed. As these instructions are not used as often as basic arithmetic instructions, the throughput of these units is often significantly lower than the throughput of the regular floating point units. As GPU workloads are typically heavy in floating point operations, GPUs often offer a higher single precision floating point throughput than integer throughput. The ratio of double precision throughput to single precision varies strongly between different GPUs. Some models aimed at high performance computing offer a 1:2 ratio <sup>2</sup> while other models aimed at the graphics market offer a meager 1:32 ratio <sup>3</sup>.

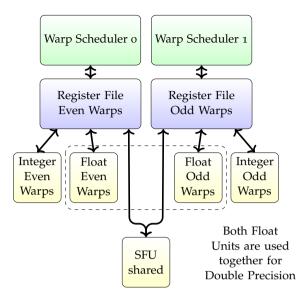

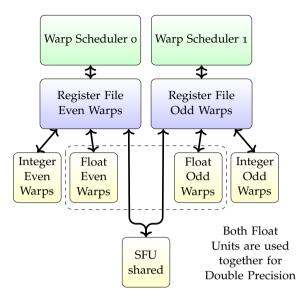

Figure 2.5 shows a simplified version of the datapath used in NVIDIA's Fermi architecture. In Fermi every core contains two warp schedulers each responsible for one-half of all warps assigned to the core. Each of the warp schedulers has its own register file and some execution units that are only usable for the warps assigned to that warp scheduler, but the SFU unit is shared between the two warp schedulers and both schedulers can submit

<sup>&</sup>lt;sup>2</sup>e.g.: Tesla P100, V100

<sup>&</sup>lt;sup>3</sup>e.g.: GTX1070, GTX1080

Figure 2.6: High-level Overview of Load/Store Unit

instructions to this shared SFU. In NVIDIA's Kepler architecture we also notice a similar kind of mix of execution units that partially shared and partially exclusive to a part of the warp. In NVIDIA's Maxwell architecture the amount of shared execution units is reduced but each core contains four warp schedulers. Shared units in Maxwell are limited to memory and texture access, which makes it easier for the compiler to schedule the instructions as it removes the non-determinism caused by the interaction of several warps schedulers sharing the same execution units. Some parallels can also be drawn to AMD's Bulldozer CPU architecture that is composed of multiple modules and each module implements two cores and shares the FPUs between two cores.

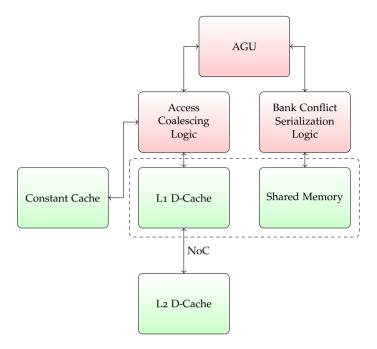

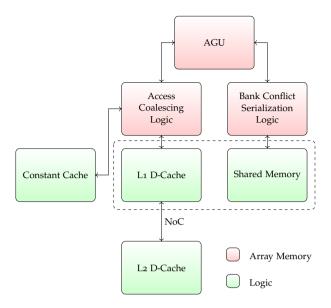

#### 2.4 MEMORY INTERFACE

A high level overview of a GPU Load/Store (LDST) unit is shown in Figure 2.6. An address generation unit (AGU) generates one address per active thread in the warp. Normal DRAM requests are sent to the address coalescing logic which tries to bundle these requests into DRAM transactions. If the threads try to access nearby accesses the number of DRAM transaction is much smaller than the number of active threads, as each DRAM transaction

typically loads or stores at least 32 consecutive bytes at a time. This depends on the width of each DRAM channel (usually 32 or 64-bit per channel) and the burst size of the employed DRAM technology. The coalesced requests are then submitted to the L<sub>1</sub> data cache within the core or a special constant cache that caches memory values that are constant during the kernel execution and can only be changed before the kernel is launched. If values are not contained in the respective local cache they are forwarded through the interconnection network to the memory controller that is responsible for the addressed part of the memory and are fetched from DRAM or L2 cache. Shared memory accesses are sent to a bank conflict serialization logic. Shared memory is a small internal memory used for exchanging data that is shared between the different threads. As the shared memory is a local part of each GPU core, it offers energy efficient, high bandwidth and low latency storage. The shared memory is local to each GPU core, so long wires are not required to connect the memory and because it can only be accessed by locally running threads and is not mapped into the address space of threads running on different cores, no cache coherency or MMU is required. Because it can only be accessed by threads running within the same core, it is only useful for facilitating intra-block cooperation of the threads. In some NVIDIA GPUs, the shared memory reuses parts of the L<sub>1</sub> cache and allows programmers to choose different configurations such as 16 KB shared memory plus 48 KB of L1, 32 KB+32 KB or 48 KB shared and 16 KB L1.

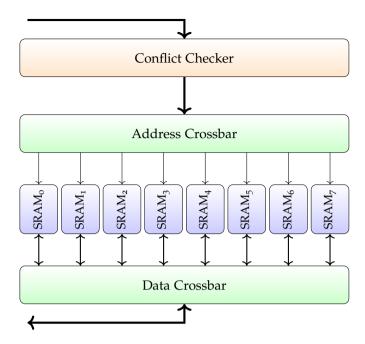

Shared memory instruction allows each thread in a warp to access a different location in the shared memory. Depending on the SIMD width of each GPU core a naive implementation would require a multi-ported memory with 8 to 32 ports. As this is not feasible within a reasonable area, a similar architecture to the register file is used: Multiple single ported banks are used and requests are serialized over several cycles if required. This is shown in Figure 2.7. A conflict checker compares the bank addresses of the incoming requests and selects a bank conflict-free subset to send to the address crossbar. If not all requests could be handled in the same cycle, this is repeated in the next cycle until the requests from all threads were executed. An address crossbar is used to direct the address from each thread to the SRAM banks. A data crossbar is used to direct the data from or to the SRAM banks to the right thread. Performance counters exposed by the NVIDIA profiler show that the generation of the additional request is implemented using a replay mechanism. Instructions are resent to the load-store unit until the requests of all active threads could be handled.

Figure 2.7: GPU Shared Memory

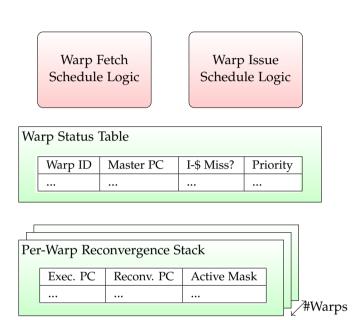

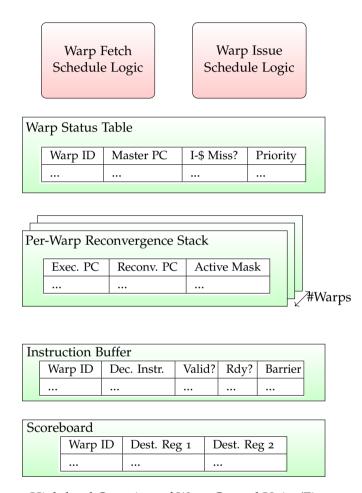

## 2.5 WARP CONTROL UNIT

The Warp Control Unit (WCU) shown in Figure 2.8 is responsible for scheduling and managing the warps. It is a key part of the GPU architecture. Within one warp, GPUs issue the instructions strictly in program order. GPUs can, however, dynamically switch between different warps. This scheme often provides a high tolerance against long memory latencies. The scheme also partly explains the large register files. Little's law, shown below, links throughput, latency and concurrency [51], [52].

# $mean\ concurrency = mean\ latency \times throughput$

A high memory throughput, together with a high latency means that many concurrent memory accesses are required. With the current GPU architecture, many concurrent memory accesses requires many concurrent threads, as every thread can only trigger a few concurrent transactions. If many concurrent threads are required, then thread context storage is also required for all of them.

The warp fetch schedule logic selects a warp with space in the instruction buffer and fetches one or multiple instructions from the instruction cache into the instruction buffer. As it only fetches the instructions but does not schedule

| Instruction Buffer |         |             |        |      |         |  |  |  |  |

|--------------------|---------|-------------|--------|------|---------|--|--|--|--|

|                    | Warp ID | Dec. Instr. | Valid? | Rdy? | Barrier |  |  |  |  |

|                    |         |             | •••    |      | •••     |  |  |  |  |

| Scoreboard |         |             |             |  |  |  |

|------------|---------|-------------|-------------|--|--|--|

|            | Warp ID | Dest. Reg 1 | Dest. Reg 2 |  |  |  |

|            |         |             |             |  |  |  |

Figure 2.8: High-level Overview of Warp Control Unit

the execution the logic does not need to evaluate whether data dependencies of the instruction are met or not. It simply looks at the instruction buffer and if a slot is empty and the warp is not yet finished, it fetches the next instruction for the warp that owns the empty slot of the instruction buffer.

The warp issue scheduler is responsible for issuing warps from the instruction buffer to the execution unit. Before the instruction is issued, the scheduler checks that the instruction is ready to be issued or if conflicts with in-flight instructions prevent the instruction from being issued at the moment. If multiple instructions are ready for issue, the warp issue scheduler can use a simple round-robin scheme or more sophisticated techniques, e.g.: some proposed schedulers optimize for better memory locality [53], [54]. Lee and Wu propose a scheduler that reduces tail effects [55]. Xu and Annavaram propose a scheduler to optimize power gating [56].

Many NVIDIA GPUs use scoreboards for checking which instructions are ready for scheduling, newer NVIDIA GPUs use a combination of scheduling hints generated by the compiler and scoreboarding for long latency operations [57]. AMD GCN GPUs also do not fully check all instruction dependency and force the compiler to insert NOPs or reorder instructions in some cases. In other cases, a special wait instruction needs to be used. It checks the number of outstanding long latency memory requests and waits if above a compiler-determined threshold [36]. These compiler-aided schemes reduce the hardware required for dependency checking and improve the energy-efficiency.

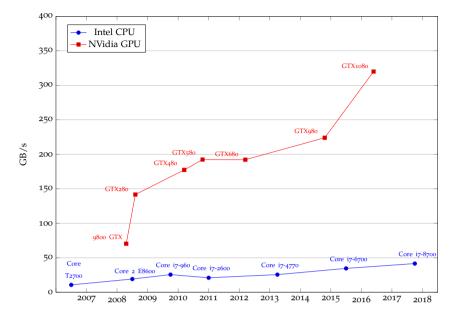

Figure 2.9: CPU vs. GPU Peak Bandwidth

#### 2.6 DRAM INTERFACE

With thousands of threads active at the same time and often very large working sets, large caches are ineffective for GPUs. GPUs also feature very high arithmetic throughput. Due to these factors GPUs need significantly higher bandwidths than CPUs. At the same time GPUs usually do not need as much memory capacity as CPUs: Rarely used data can quickly be uploaded via PCI express when required. GPU memory is typically not used to cache disk content or large databases.

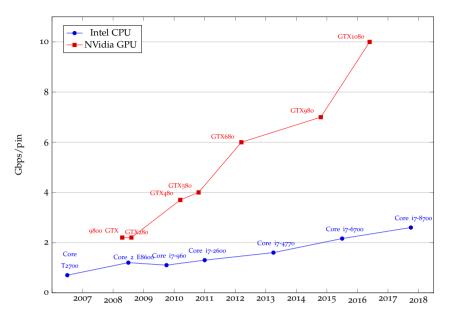

Due to these reasons GPU memory interface typically have different characteristics than CPU memory interfaces. Figure 2.9 shows the peak bandwidth of various CPU and GPU memory interfaces. The bandwidth provided by GPU is significantly higher. Even the slowest and oldest GPU provides a significantly higher memory bandwidth than the newest and fastest CPU listed in the chart. The fastest GPU in chart features almost 8 times the memory bandwidth of the fastest CPU. Figure 2.10 lists the bandwidth per data pin, it can be seen that the higher bandwidth is partly provided through the use of faster signaling standards. NVIDIA's GTX1080 uses a GDDR5X interface at 10 Gbps, while the Core i7-8600 uses DDR4 at 2.66 Gbps. The signaling employed by the GPU is almost 4 times faster.

A wider interface explains the remaining gap in the peak bandwidth: The interface used by the CPU is 128-bit wide, while the GPU uses a 256-bit

Figure 2.10: CPU vs. GPU Bandwidth per Pin

Figure 2.11: CPU vs. GPU Flops per Byte

wide interface. But the CPU memory interface also has many advantages: The CPU can use up to 64 GB of memory and memory can be extended or replaced using memory modules, while the GPU has 8 GB of GDDR5X directly soldered to the PCB and memory cannot be extended or replaced. GDDR5 [58] and GDDR5X [59] are also significantly more expensive per storage byte than DDR4 [60].

Connectors such as the DIMM sockets used by CPUs create crosstalk and EMI [61]. CPUs commonly allow the connection of multiple memory chips to each data pin, however, the resulting multi-drop bus the parasitic capacitances of connectors can distort the signal [61]. Soldering memory to the PCB instead of using sockets and using point-to-point connections instead of multi-drop bus provides a better signal quality and thus allows for higher data rates. However, it also prevents memory upgrades and high memory capacity.

However, despite the high bandwidth in absolute terms, GPU memory bandwidth is often a significant bottleneck, as we also need to consider the very high computational throughput of GPUs. Figure 2.11 shows the flops per byte for various GPUs and CPUs. For both CPUs and GPUs, peak performance is growing faster than memory bandwidth. Applications on both CPUs and GPUs must compute many floating point operations per byte to avoid being limited by memory bandwidth. NVIDIA'S GTX1080 needs to perform 25.6 or more floating point operations per byte in order to avoid being limited by memory bandwidth. Despite having only 1/8 of the memory bandwidth, the Core i7-8600 only needs 19.8 flops per byte.

To solve this bandwidth shortage some GPUs employ high bandwidth memory (HBM) [62]. HBM and its successor HBM2 use a silicon interposer and through silicon vias (TSV) to include the DRAM in the same package as the GPU and offer a very wide interface [63]. The very wide interface possible due to the interposer and TSVs allows reducing the per pin bandwidth to reduce the power consumption and simplify the required drivers, receivers and clocking circuits while still providing a bandwidth increase. AMD's Radeon R9 Fury X GPU uses a 4096-bit wide interface to provide 512 GB/s bandwidth while running at just 1 Gbps per pin. GDDR5 interface width is typically limited to a maximum of 512-bit, with 256-bit wide interfaces being more common. NVIDIA's (very expensive) Tesla V100 reaches 900 GB/s using HBM2 and a 4096-bit wide interface [64].

Beside increasing the actual memory bandwidth, compression and tile-based rendering are often used techniques for increasing the effective bandwidth, mainly for 3D rendering. Tile-based rendering was originally proposed for parallel rendering but is also highly useful for reducing the required memory bandwidth [65]. Both lossless and lossy compression techniques have been used to reduce the required bandwidth. Textures are often stored using lossy compression algorithms [66], [67]. Z-Buffers often use a hierarchical compressed storage to reduce the required bandwidth and allow the early

z-rejection of blocks of pixels [68], [69]. However, while the use of memory compression is common for 3D rendering, compression is usually not used in GPGPU applications. In a paper, co-authored by the author of this thesis, Lal et al. proposed E<sup>2</sup>MC as a memory compression technique for GPG-PUs [70]. As already mentioned above, Lee proposed a compressed register file [50], Vijaykuma et al. propose a clever hardware/software solution, where unused compute resources are used to provide memory compression [71]. Pekhimenko et al. describe a compression technique that aims to reduce the interface energy by reducing the number of bit toggles [72]. Rhu et al. propose a specialized DMA based compression for deep learning, one of the most common GPGPU applications [73].

### 2.7 SUMMARY

This chapter provided an overview about current GPU architecture. We described the programming models employed by GPGPU APIs such as CUDA and OpenCL. We explained how threads are bundled together into warps and how branching is enabled while threads are executed on SIMD execution units. We illustrated how the GPU architecture focus differs from CPU architecture by focusing on throughput instead of latency. The use of multiple warps and warp scheduling to compensate for memory and arithmetic latency was described as well as the large GPU register files, shared memory and the high bandwidth external memory interfaces used by GPUs. The next chapter provides a survey of related work for the entire thesis.

## RELATED WORK

This chapter reviews work related to this thesis. We start with additional introductions into GPU architecture in Section 3.1. Section 3.2 lists related work for GPU power measurements and Section 3.3 continues with architectural GPU power modeling. Section 3.4 takes a look at work linked to data-dependent power modeling. The second half of the chapter proceeds with literature related to the architectural enhancements proposed in Chapters 8 to 11. Section 3.5 reviews papers related to the proposed memory interface power reduction encoding. We then cover work related to our refresh power reduction technique in Section 3.6. After these two memory-related sections, the next Section continues with (Spatio-)Temporal SIMT related research. The related work chapter finishes with Section 3.8 related to Scalarization.

### 3.1 GPU ARCHITECTURE

In addition to the introduction found in Chapter 2, many books and papers provide further insight into GPU architecture. While we cannot list them all here, we selected a list of works we found especially valuable for the readers of this thesis. Kirk and Hwu's book provides a good history of GPUs as well as a great introduction into CUDA programming [74]. The 5th edition of Hennesey and Patterson's classic book was updated with an excellent chapter on "Data-Level Parallelism in Vector, SIMD, and GPU Architectures" that helps to put GPUs into perspective [75].

The GPGPU-Sim manual describes the GPU architecture modeled by the popular simulator and can be understood as a best guess description of NVIDIA's Tesla and Fermi architecture GPUs [37].

Both NVIDIA and AMD provide many white papers on the architecture of their GPUs (e.g.: [57], [76]–[78]), however, these descriptions often lack detail and target programmers instead of architects.

AMD provides many details for their GCN architecture GPUs as part of their "GPU Open" initiative and their support for open source GPU driver development. Information released by AMD includes a complete documentation of the instruction set of their latest GPUs as well as an overview of the architecture of the whole GPU and the individual GPU cores in particular [36].

### 3.2 POWER MEASUREMENT

Some related work [79], [80] employed commercial wall-plug power meters. These meters are inserted between the PC power supply and the power outlet. They measure the power consumption of the whole PC, instead of measuring only the power consumption of the GPU. Hong and Kim [79] assume the GPU power can be calculated by measuring the power of the entire PC under load and subtracting the power of the PC in idle state. This assumption yields high inaccurate results, because the power used by the remaining PC components is usually not constant and the measurement results will include power supply losses. Large bypass capacitors inside the power supply prevent the accurate measurement of power for kernels which run fewer than 50 ms.

Ma et al. [80] tried to solve the first issue by using a second ATX power supply powering only the GPU but this approach ultimately suffers partially from these issues as well because the GPU also receives parts of their power supply from the PCIe slot and these supplies are provided by the same ATX power supply that also powers the mainboard, CPUs, memory and other non-GPU components.

Other papers [81]–[83] use improved measurement methodologies but still exhibit multiple limitations. These published methodologies either fail to measure all power sources, e.g. do not measure the power provided via the graphics card slot [81], measure only current and assume constant voltages [82], or use low sampling frequencies that prevent them from measuring short-term power variations [81], [83].

Burtscher et al. explain how power sensors included in some GPUs can be used to measure the power consumption, however, these sensors lack the resolution and sampling rate of the measurement testbed presented in this thesis[84].

### 3.3 ARCHITECTURAL GPU POWER MODELING

For general GPU power modeling, the available body of previous work was rather small, when the work in Chapter 5 was initially published. On the one hand, there have been approaches such as the ones from Hong and Kim [79] or Ma et al. [83] which are based entirely on measured data. While this type of power model is able to deliver superior accuracy for the architecture it was built from, it lacks the capability to make accurate predictions about GPUs with other architectural parameters and designs. On the other hand, several researchers have built purely analytic power models, such as Ramani et al. [85]

and Wang [86]. While such approaches generally show a strong correlation between different simulated and hardware GPU architecture configurations, they typically cannot provide reasonable absolute accuracy due to the lack of either industrial or measured anchor data. Our power simulator improves upon all these prior approaches by *combining* both empirical and analytical component models to create a system that is both architecturally flexible and shows reasonable absolute accuracy. A similar approach to ours has previously been used to estimate CPU power consumption by the well-known McPAT tool [87].

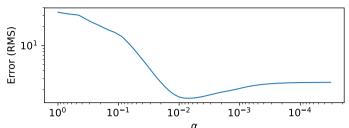

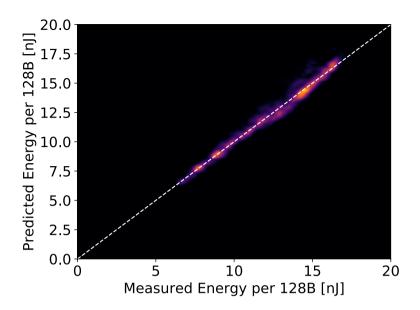

As already explained in the previous section, many GPU power modeling papers made strong assumptions about the hardware they measure, leading to inaccurate measurement methodologies. After this work was initially published, several other papers presented similar studies. Leng et al. presented their power simulator GPUWattch [88]. Just like GPUSimPow, it combines gpgpu-sim with a power model based on an extended version of McPAT. It also uses a good GPU power measurement, similar to the measurement testbed used for GPUSimPow and a clear improvement compared to the older papers listed above. GPUWattch also relies on analytical models for modeling the energy consumption of many GPU components. The two simulators differ in how they employ microbenchmarks. GPUWattch provides power models for all main GPU components based on CACTI, McPAT or Synopsys Power Compiler. It then uses microbenchmarks in a refinement stage to rescale the outputs of the power models. For increased accuracy the outputs of the analytical models are multiplied with the refinement factors estimated in the refinement stage. The use of these factors has been criticized to render results of the analytical model to be "mathematically irrelevant" [89]. GPUSimPow does not use a refinement stage but instead models some components using models calibrated with microbenchmark based measurements. Lim et al. also describe a power simulator for GPUs based on an extended McPAT and gpgpu-sim [90]. The authors list a different focus of the paper as the main difference to GPUWattch. Diop et al. describe a power model for heterogeneous processors containing GPUs [91].

Since its release, several papers have used GPUSimPow for estimating area and/or power consumption of GPUs. Libuschewski et al. used GPUSimPow inside a multi-objective energy optimization framework to estimate the energy used by a mobile GPU in a mobile biosensor application [92] as well as for design space exploration for mobile GPGPUs [93]. Sankaranarayanan et al. used GPUSimPow to evaluate the energy benefits of a modification to the GPU memory hierarchy they propose [94]. Nath et al. employed GPUSimPow to estimate the static power consumption of various GPU configurations to build a model of DVFS in GPUs [95]. Dhar and Chen used GPUSimPow for estimating the area of a GPU core and its static power consumption [96].

### 3.4 DATA-DEPENDENT POWER MODELING

Many popular architectural power simulators for CPUs and GPUs ignore the data values processed by the datapath. McPAT's CPU core power model [87], for example, counts various register reads, uses of integer and floating point ALUs, integer multiplies, register renaming, but neither the exact instruction type nor any statistics about the processed data values are used to predict the power consumption.

GPUWattch [88] and GPUSimPow [97] are power simulators for GPUs. Both simulators are based on gpgpu-sim and extend it with a McPAT-based GPU power model. These architectural simulators count activity factors for various GPU units and use them to estimate the power consumption of the GPU. Counted activities are integer or floating point instructions, register reads and writes, memory accesses, etc. None of the used activity factors measures how often datapath lines switch between 0 and 1.

One exception to ignoring data values is the original Wattch power simulator [98]. Wattch contains a DYNAMIC\_AF option in its source code that collects activity factors based on average population count of the processed values, but this is only used for some internal buses and memories but not for the ALU. In fact, the Wattch source code contains the comment: "FIXME: ALU power is a simple constant, it would be better to include bit AFs and have different numbers for different types of operations". The Wattch authors apparently recognized that this was a weak point in their simulator. For a CPU power simulator where control logic dominates the datapath, using such a simple model might still be acceptable, but accelerators such as GPUs try to keep the control logic small and simple and use large parts of their power and area budget for execution units and register files. In Chapter 6, we will show that for these accelerators more accurate power models are required.

Kim, Austin, Mudge and Grunwald [99] also recognize that architectural power simulators ignore values and memory addresses in their power estimation. They describe how an architectural simulator for CPUs that considers values could be built and developed a prototype based on SimpleScalar but did not validate their model.

Adhinarayanan measures and models the data depend interconnection power on an AMD GCN GPU with OpenCL [100]. Our work uses a NVIDIA Fermi GPU with CUDA and also measures the external interface.

Some related work exists for microprocessors. Sarta, Trifone and Ascia propose a data dependent power model for a simple DSP with a 2-stage pipeline [101]. They find that operands strongly influence the energy consumption and also employ linear least square fitting. Kerrison and Eder [102] model the energy consumption of a hardware multi-threaded microprocessor. They consider the overhead of switching from one instruction to another and the influence of data values on energy consumption.

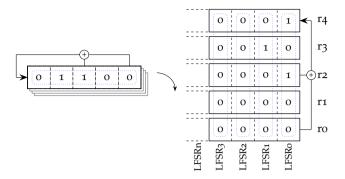

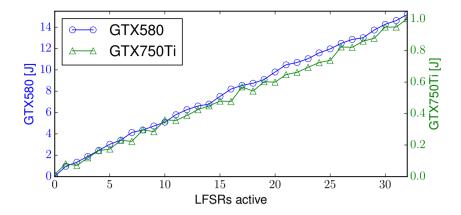

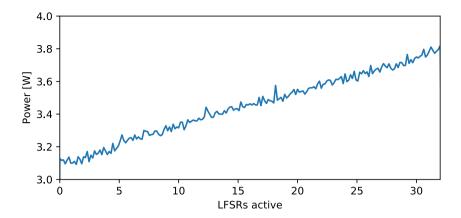

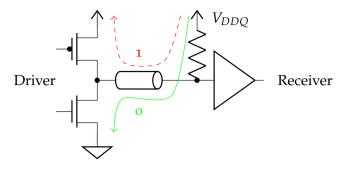

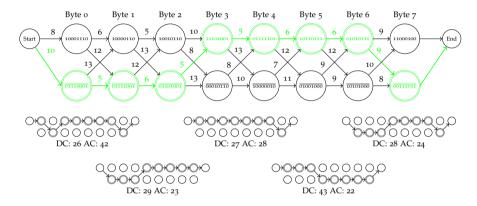

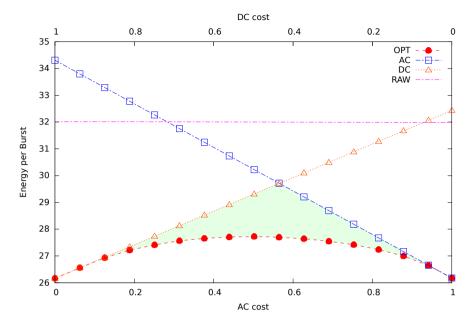

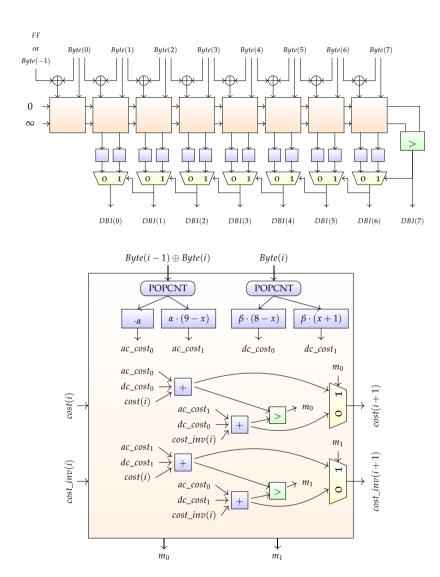

### 3.5 OPTIMAL DBI ENCODING

Hollis [103] described the DBI DC and DBI AC schemes and recognized that both the number of transmitted zeros and the number of signal transitions are important for the power consumption of the memory interface. The slight increase of the signal transitions in DBI DC and the slight increase of transmitted zeros in DBI AC was also described in the same paper. Hollis proposes to combine DBI AC and DC by switching between DBI DC and DBI AC encoding modes. The proposed DBI ACDC scheme encodes the first byte of a group of bytes using DBI DC and then encodes the remaining bytes using DBI AC. We found that this scheme indeed provides a slight improvement compared to pure DBI AC. However, the encoding proposed in this thesis outperforms the DBI ACDC scheme. In this thesis, we assume that all lines transmitted ones prior to transmitting the evaluated burst. Due to this boundary condition, DBI AC performs identically to DBI ACDC in our evaluation.

Chang et al. [104] propose schemes that aim to reduce both zeros and transitions per burst. However, instead of finding the minimal energy encoding for each burst, they propose heuristic schemes that find good but not necessary optimal encodings.

In a patent, Hollis [105] proposes a technique to target both signal transition and zeros. This technique uses additional signal lines and requires a different and more complex decoding process than regular DBI schemes.

Ihm et al. propose an analog circuit for DBI DC encoding [106]. Analog implementation could also reduce the overhead of the technique proposed in Chapter 8 and DBI encoding seems to be well suited for analog implementation as rare inaccurate encoding decision are unlikely to causes application errors.

Stan and Burleson [107] provide theoretical background on DBI encoding, however, they only consider the reduction of signal transition and do not consider the reduction of zeros.

Narayanan et al. [108] describe additional coding schemes that can reduce the number of signal transitions beyond DBI, but require an even higher number of lines and more complex encoding and decoding.

Kim et al. describe DBI DC in GDDR4 and show how it reduces simultaneous switching output noise [109].

Pekhimenko et al. describe a toggle-aware compression scheme for GPU [72]. This scheme reduces signal transition by choosing data representations with reduced toggling.

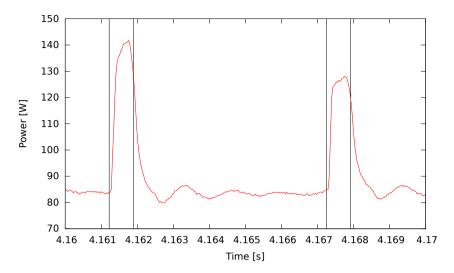

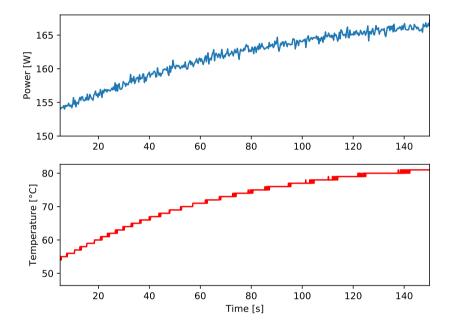

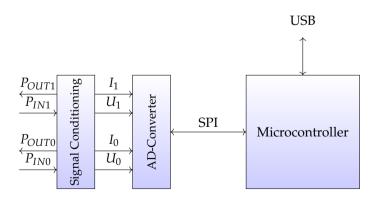

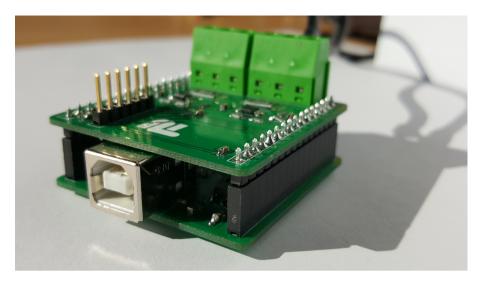

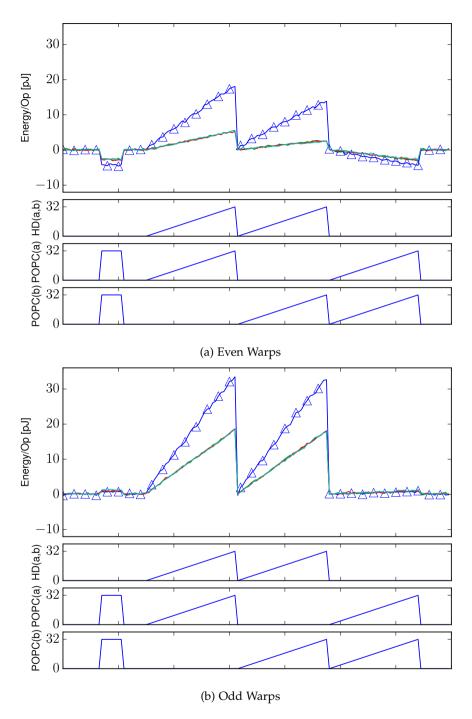

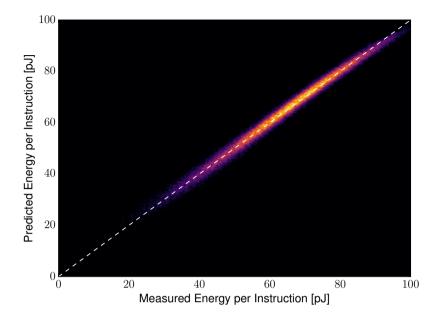

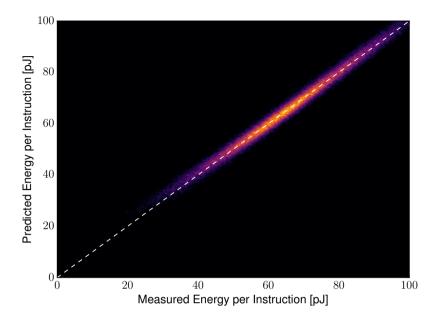

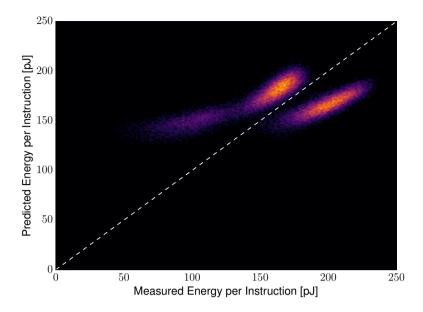

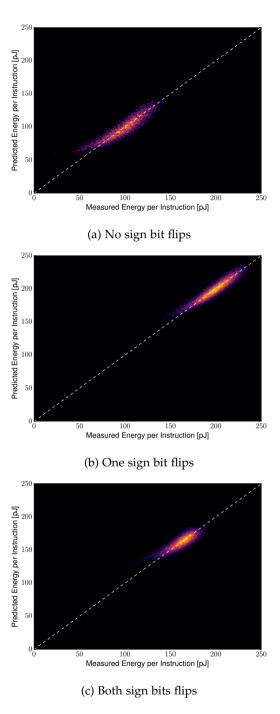

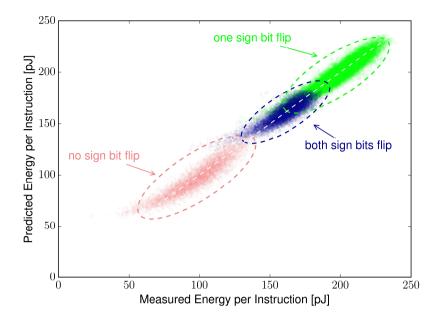

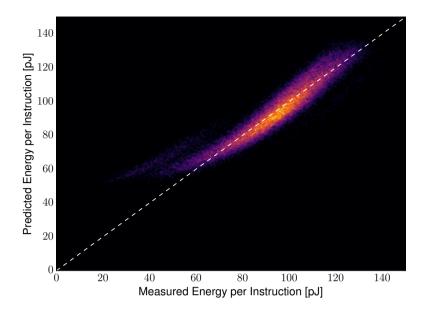

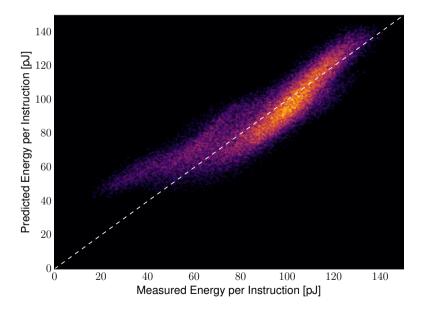

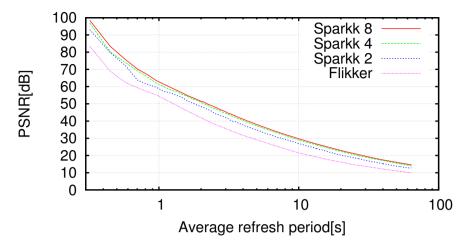

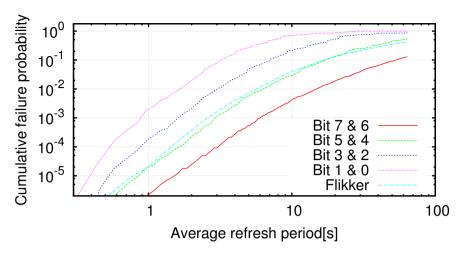

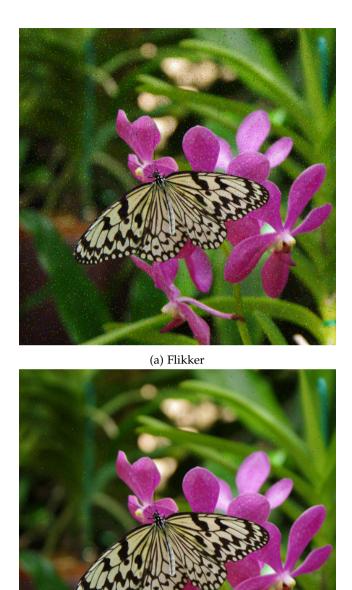

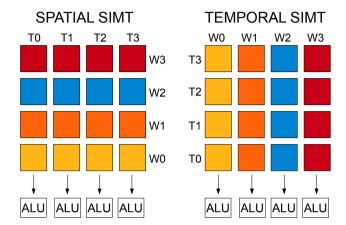

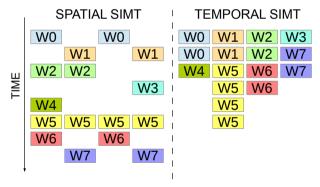

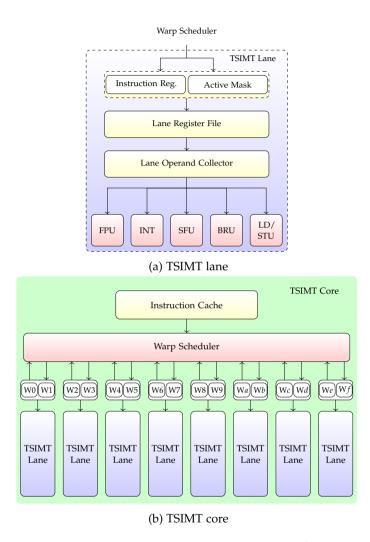

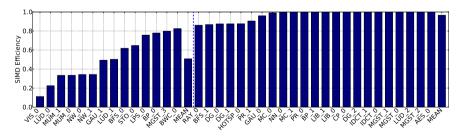

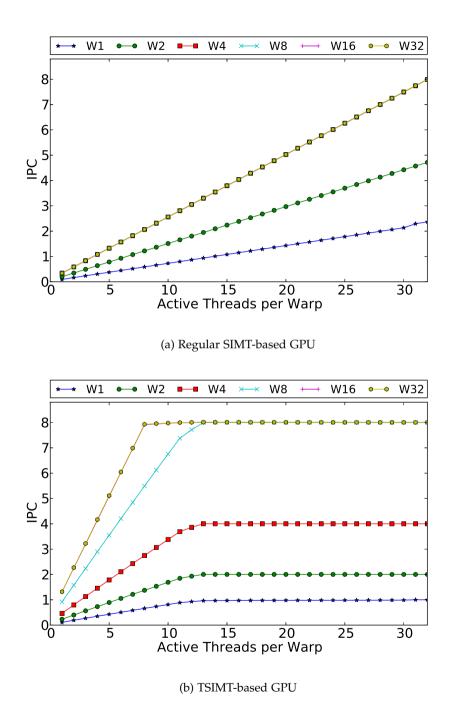

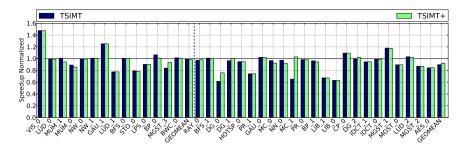

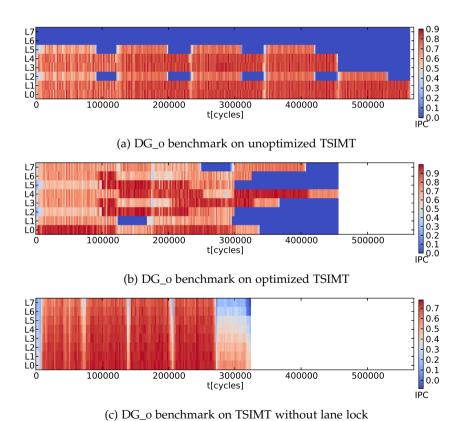

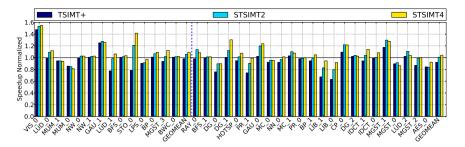

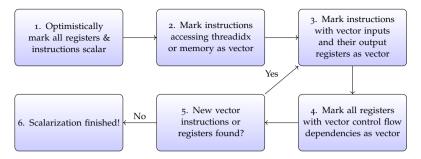

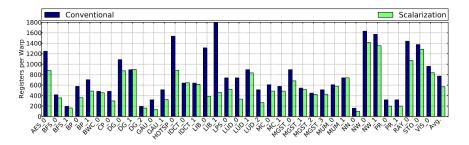

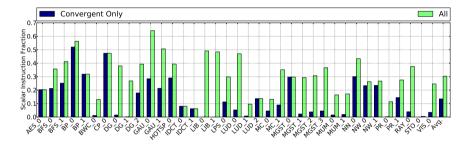

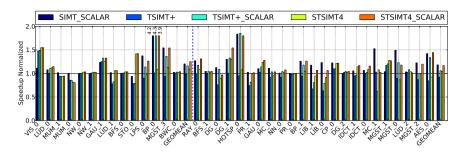

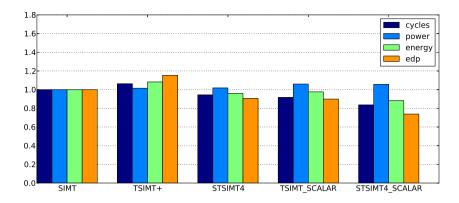

## 3.6 SPARKK