## A Framework for the Automatic Verification of Discrete-Time MATLAB Simulink Models using Boogie

vorgelegt von Robert Reicherdt, Master of Science in Computer Science geb. in Erlabrunn

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

– Dr.-Ing. –

genehmigte Dissertation

#### **Promotionsausschuss:**

Vorsitzender:Prof. Dr. Oliver Brock<br/>Technische Universität BerlinGutachterin:Prof. Dr. Sabine Glesner<br/>Technische Universität BerlinGutachter:Prof. Dr. Holger Giese<br/>Hasso-Plattner-Institut, Universität PotsdamGutachter:Prof. Dr. Odej Kao<br/>Technische Universität Berlin

Tag der wissenschaftlichen Aussprache:10. Juli 2015

Berlin, 2015

#### Abstract

MATLAB/Simulink is a widely used industrial tool for the development of embedded systems, especially for the development of embedded controller software in automotive industries. Since such embedded systems are often deployed in safety critical areas where an error may lead to severe injuries and even to death of persons, comprehensive and complete quality assurance measures are required for ensuring their correctness in all possible cases. Still, incomplete techniques like testing are favored over safe formal techniques in practice. Although there exist some formal verification approaches for MAT-LAB/Simulink models that can guarantee correctness, they are either poorly automated or suffer from scalability issues.

To overcome this problem, we present an approach for a highly automated verification framework for MATLAB/Simulink models that enables the formal verification of discrete-time controller models. Our main idea is to use inductive verification techniques in combination with an automatic extraction of verification goals for a number of important run-time error classes to provide an automatic verification flow. Furthermore, as automatic model reduction technique, we present a slicing approach for MATLAB/Simulink. With that, we increase the scalability by dividing a possibly complex verification task into a number of less complex subtasks.

To enable the automatic verification of MATLAB/Simulink models, we present a formal semantics for discrete-time models based on a mapping of the informally defined sequential simulation semantic into the formally well defined intermediate verification language Boogie2. Together with automatically generated invariants and verification goals that are automatically weaved into the formal model, this mapping enables the verification of the models using the Boogie verification framework and inductive verification techniques. To achieve a high degree of automation, we also support inductive verification over more than one simulation step (k-induction), which allows for weaker invariants that can be generated automatically at the price of decreased scalability. To overcome scalability issues for k-induction, we use our novel slicing technique for MATLAB/Simulink models to automatically reduce a model to those blocks that are relevant for a (possible) error at a particular block. Furthermore, we propose a process for the efficient use of our verification and slicing techniques.

To show the practical applicability of our framework, we have implemented our approach as the *MeMo* tool suite and applied our verification process to two industrial case studies. With that, we demonstrate the performance and the capability to automatically verify a given model for the absence of important run-time errors with our verification framework for discrete-time MATLAB/Simulink models.

$\mathbf{4}$

#### Zusammenfassung

MATLAB/Simulink ist ein weit verbreitetes Werkzeug für die Entwicklung von eingebetteten Systemen, welches vor allem in der Automobilindustrie zur Entwicklung von Steuerungssystemen benutzt wird. Da solche Systeme häufig in sicherheitskritischen Umgebungen eingesetzt werden, wo eine Fehlfunktion zu schweren Verletzungen und Todesfällen führen kann, werden umfangreiche und vollständige Qualitätssicherungsmaßnahmen benötigt um die Korrektheit der Systeme für alle möglichen Ausführungen sicher zu stellen. Trotzdem werden unvollständige Techniken wie Testen in der Praxis gegenüber den sicheren formalen Methoden bevorzugt. Obwohl es einige formale Verifikationstechniken für MATLAB/Simulink gibt, sind diese entweder kaum automatisiert oder skalieren schlecht.

Um dieses Problem zu lösen stellen wir in dieser Arbeit einen Ansatz für eine hochautomatisierte Verifikationsumgebung für MATLAB/Simulink Modelle vor, mit der zeitdiskrete Modelle für Steuerungen formal verifiziert werden können. Die Kernidee in unserem Ansatz ist hierbei eine Kombination aus induktiven Verifikationstechniken und dem automatischen Extrahieren von Verifikationszielen für bestimmte Laufzeitfehler verwenden, um einen automatisierten Verifikationsfluss zu erreichen. Außerdem stellen wir einen Ansatz für das Slicing von MATLAB/Simulink Modellen vor, der als automatisches Verfahren zur Reduzierung der Modellkomplexität verwendet wird. Mit diesem erreichen wir eine bessere Skalierbarkeit, da wir eine komplexe Verifikationsaufgabe in eine Anzahl von weniger komplexen Teilaufgaben aufspalten können.

Um die automatische Verifikation von MATLAB/Simulink Modellen zu ermöglichen, stellen wir eine formale Semantik für zeitdiskrete Modelle vor, die auf einer Abbildung der informellen, sequenziellen Simulationssemantik in die formale Verifikationszwischensprache Boogie2 basiert. Zusammen mit automatisch erzeugten und in das formale Modell eingewobenen Invarianten und Verifikationszielen, erlaubt dies die Verifikation der Modelle mit dem Boogie-Framework und induktiven Verifikationstechniken. Um einen hohen Grad der Automatisierung zu erreichen, unterstützen wir auch induktive Verifikationstechniken über mehr als einen Simulationsschritt (k-Induktion), was zwar die Verwendung von schwächeren, automatisch generierten Invarianten erlaubt, aber gleichzeitig die Skalierbarkeit reduziert. Um dem entgegenzuwirken, nutzen wir unser neuartiges Slicing-Verfahren für MATLAB/Simulink Modelle um diese automatisch auf genau die Blöcke zu reduzieren, die für einen (möglichen) Fehler an einem bestimmten Block relevant sind. Darüber hinaus schlagen wir einen Prozess für die effiziente Benutzung unserer Verifikations- und Slicing-Techniken vor.

Um die praktische Anwendbarkeit unserer Verifikationsumgebung zu zeigen, haben wir diese in unserem *MeMo*-Werkzeug implementiert und unseren Prozess auf zwei industrielle Fallbeispiele angewendet. Damit haben wir die Performanz und die Fähigkeit, die Abwesenheit von wichtigen Laufzeitfehlern in einem gegebenen Modell automatisch zu verifizieren, nachgewiesen.

#### Danksagung

Die vorliegende Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Fachgebiet "Programmierung eingebetteter Systeme". Daher möchte ich mich an dieser Stelle herzlich für die Betreuung meiner Arbeit durch Prof. Dr. Sabine Glesner bedanken. Sie hat mir die Möglichkeit gegeben in einem praxisnahen Bereich zu promovieren und mir den Freiraum gelassen, eigene Schwerpunkte zu setzen und hat durch ihre Bereitschaft zur Diskussion und ihre wertvollen Anmerkungen zum Gelingen dieser Arbeit beigetragen. Weiterhin möchte ich Herrn Prof. Dr. Giese und Herrn Prof. Dr. Kao für die Durchsicht und Begutachtung meiner Arbeit danken. Nicht zuletzt gilt mein Dank unseren Industriepartnern, der Berner und Mattner Systemtechnik GmbH und der Model Engineering Solutions GmbH, die mir durch Bereitstellung der Anwendungsfälle und Fallstudien geholfen haben, Kriterien und Anknüpfungspunkte für meine Arbeit abzuleiten.

Natürlich möchte ich mich auch bei den Kolleginnen und Kollegen in unserem Fachgebiet für die angenehme Atmosphäre und ihre Anmerkungen zu meiner Arbeit bedanken. Besonders bedanken möchte ich mich hierbei bei Dr. Paula Herber und Dr. Thomas Göthel. Beide haben mich nicht nur während meiner Promotionszeit durch ihre Bereitschaft zu wissenschaftlichen Diskussionen unterstützt, sondern auch während der Fertigstellung durch wiederholtes Korrekturlesen und hilfreiches Feedback maßgeblich zum Gelingen dieser Arbeit beigetragen haben.

Weiterhin möchte ich meiner Familie und meinen Freunden danken für ihre Unterstützung während der ganzen Zeit. Mein größter Dank gilt hierbei meiner Freundin Kerstin Knebel, die mir in der heißen Phase den Rücken freigehalten und mich immer unterstützt hat. Natürlich möchte ich auch meinen Eltern, Sabine und Lutz Reicherdt danken, die mich auch vor und während meines Studiums sowie meiner Promotionszeit unterstützt haben. Schließlich möchte ich auch meinem Sohn Nils danken, der mich zum einen durch seine anstehende Geburt zu Höchstleistungen angespornt hat, mir aber gleichzeitig genug Zeit gegeben hat, die Arbeit meinen Ansprüchen genügend fertigzustellen.

Robert Reicherdt, Dezember 2015

### Contents

| 1 | Intr | duction 13                                                                                                                  | 3 |

|---|------|-----------------------------------------------------------------------------------------------------------------------------|---|

|   | 1.1  | $Problem \dots \dots$ | 3 |

|   | 1.2  | Objectives $\ldots \ldots 14$    | 1 |

|   | 1.3  | Proposed Solution                                                                                                           | 5 |

|   | 1.4  | $Motivation \ldots 10$    | 3 |

|   | 1.5  | Main Contributions                                                                                                          | 7 |

|   | 1.6  | Context of this Work                                                                                                        | 3 |

|   | 1.7  | Overview of this Thesis                                                                                                     | 3 |

| 2 | Bac  | ground 21                                                                                                                   | L |

|   | 2.1  | Model Driven Development and Engineering                                                                                    | L |

|   |      | 2.1.1 Model Driven Engineering $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$                                        | L |

|   |      | 2.1.2 Model Driven Development                                                                                              | 3 |

|   |      | 2.1.3 Summary $\ldots$ $24$                                                                                                 | 1 |

|   | 2.2  | MATLAB/Simulink                                                                                                             | 5 |

|   |      | 2.2.1 Simulink $\ldots \ldots 20$                     | 3 |

|   |      | 2.2.2 Model Elements and Simulation Mechanics                                                                               | 7 |

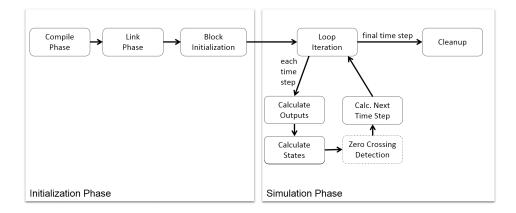

|   |      | 2.2.3 Simulation $\ldots \ldots 30$                          | ) |

|   |      | 2.2.4 Summary $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                           | 2 |

|   | 2.3  | Program Verification                                                                                                        | 3 |

|   |      | 2.3.1 Verification of the Correctness of Programs                                                                           | 3 |

|   |      | 2.3.2 Automatic and Inductive Verification with Weakest Pre-                                                                |   |

|   |      | conditions $\ldots \ldots 38$                                | 3 |

|   |      | 2.3.3 Verification with Automatic Theorem Proving 45                                                                        | 5 |

|   |      | $2.3.4  \text{Summary}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    | 7 |

|   | 2.4  | The Boogie Verification Framework                                                                                           | 7 |

|   |      | $2.4.1  \text{Boogie2}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    | 3 |

|   |      | 2.4.2 The Boogie Verifier $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 52$                               | 2 |

|   |      | 2.4.3 Summary                                                                                                               | 3 |

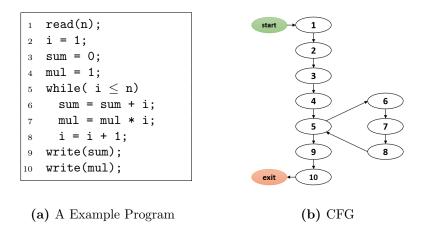

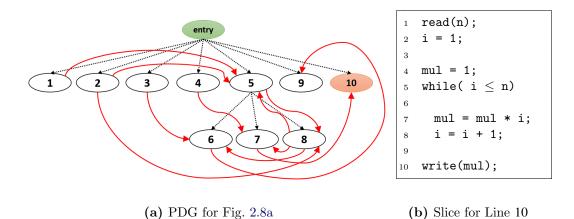

|              | 2.5             | Slicing                                                     | 53 |  |  |  |  |

|--------------|-----------------|-------------------------------------------------------------|----|--|--|--|--|

|              |                 | 2.5.1 The Program Dependence Graph                          | 54 |  |  |  |  |

|              |                 | 2.5.2 Static Slicing with Program Dependence Graphs         | 56 |  |  |  |  |

|              | 2.6             | Summary                                                     | 57 |  |  |  |  |

| 3            | Related Work    |                                                             |    |  |  |  |  |

|              | 3.1             | Verification of Simulink Models                             | 59 |  |  |  |  |

|              |                 | 3.1.1 Verification of Hybrid Simulink Models                | 59 |  |  |  |  |

|              |                 | 3.1.2 Verification of Discrete Simulink Models              | 60 |  |  |  |  |

|              | 3.2             | Slicing of Simulink Models                                  | 62 |  |  |  |  |

|              |                 | 3.2.1 Slicing of State-based Models                         | 63 |  |  |  |  |

|              |                 | 3.2.2 Slicing of Synchronous Models                         | 65 |  |  |  |  |

|              | 3.3             | Summary                                                     | 65 |  |  |  |  |

| 4            | Aut             | omatic Verification Approach                                | 67 |  |  |  |  |

|              | 4.1             | Verification Idea                                           | 68 |  |  |  |  |

|              | 4.2             | Verification Framework Architecture                         | 69 |  |  |  |  |

|              | 4.3             | Verification Process                                        | 71 |  |  |  |  |

|              | 4.4             | Summary                                                     | 72 |  |  |  |  |

| 5            | Slic            | ing of Simulink Models                                      | 73 |  |  |  |  |

|              | 5.1             | Assumptions                                                 | 74 |  |  |  |  |

|              | 5.2             | Dependence Analysis                                         | 75 |  |  |  |  |

|              |                 | 5.2.1 Data Flow and Data Dependence                         | 75 |  |  |  |  |

|              |                 | 5.2.2 Control Flow in Simulink                              | 76 |  |  |  |  |

|              |                 | 5.2.3 Conditional Execution Contexts and Control Dependence | 79 |  |  |  |  |

|              |                 | 5.2.4 Calculation of Control Dependence                     | 81 |  |  |  |  |

|              |                 | 5.2.5 Summary                                               | 86 |  |  |  |  |

|              | 5.3             | Slicing of Simulink Models                                  | 86 |  |  |  |  |

|              |                 | 5.3.1 Building the Dependence Graph                         | 86 |  |  |  |  |

|              |                 | 5.3.2 Computing the Simulink Slice                          | 87 |  |  |  |  |

|              |                 | 5.3.3 Example                                               | 88 |  |  |  |  |

|              | 5.4             | Increasing the Precision of Slices                          | 90 |  |  |  |  |

|              |                 | 5.4.1 Routing-aware Dependence Analysis                     | 91 |  |  |  |  |

|              |                 | 5.4.2 Routing-aware Dependence Graph                        | 95 |  |  |  |  |

|              | 5.5             | Summary                                                     | 97 |  |  |  |  |

| 6            | Tra             | nsformation of Discrete-Time Simulink Models to Boogie      | 99 |  |  |  |  |

| 6.1 Overview |                 |                                                             |    |  |  |  |  |

|              | 6.2 Assumptions |                                                             |    |  |  |  |  |

|   | 6.3                                                         | A For                                                                                                                                          | mal Model for Simulink                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                             | 6.3.1                                                                                                                                          | Modeling Blocks                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                             | 6.3.2                                                                                                                                          | Modeling Signals                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                             | 6.3.3                                                                                                                                          | Block States and Intermediate Results                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                             | 6.3.4                                                                                                                                          | Initialization                                                                                                                                                                                                                                                                                                                                                                                                                      |

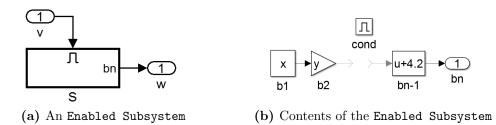

|   |                                                             | 6.3.5                                                                                                                                          | Modeling Control Flow                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                             | 6.3.6                                                                                                                                          | Data Types                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 6.4                                                         | Calcu                                                                                                                                          | lation of the Control Flow Graph $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 109$                                                                                                                                                                                                                                                                                                                                             |

|   |                                                             | 6.4.1                                                                                                                                          | How Simulink calculates the Sorted Order                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                             | 6.4.2                                                                                                                                          | Calculating the Sorted Order                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 6.5                                                         | Mapp                                                                                                                                           | ing of Simulink Blocks to Boogie2                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                                             | 6.5.1                                                                                                                                          | Sources Block Set                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                                             | 6.5.2                                                                                                                                          | Math Operations Block Set                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                             | 6.5.3                                                                                                                                          | Logic and Bit Operations                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                             | 6.5.4                                                                                                                                          | Ports & Subsystems Block Set                                                                                                                                                                                                                                                                                                                                                                                                        |

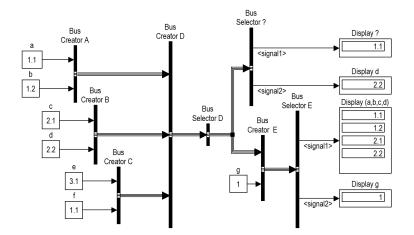

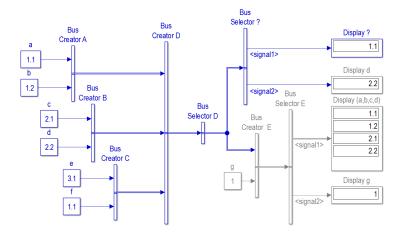

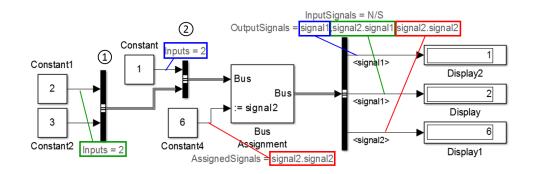

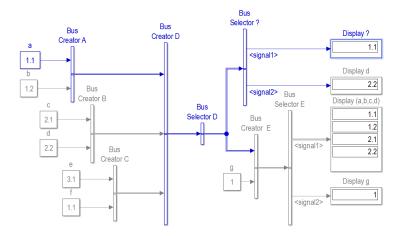

|   |                                                             | 6.5.5                                                                                                                                          | Signal Routing Block Set                                                                                                                                                                                                                                                                                                                                                                                                            |

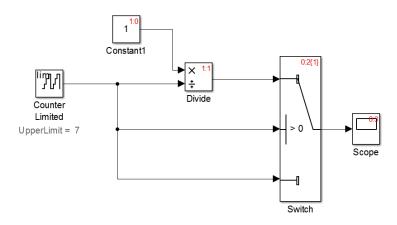

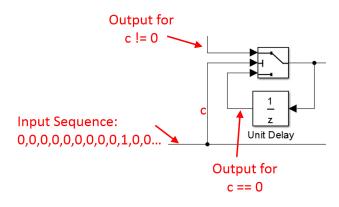

|   |                                                             | 6.5.6                                                                                                                                          | Discrete Block Set                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                             | 6.5.7                                                                                                                                          | User-defined Functions Block Set                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                             | 6.5.8                                                                                                                                          | Sinks Block Set                                                                                                                                                                                                                                                                                                                                                                                                                     |

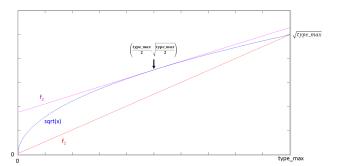

|   |                                                             | 6.5.9                                                                                                                                          | Implicit Casts and Mechanisms for Multiple Block Types 130                                                                                                                                                                                                                                                                                                                                                                          |

|   | C C                                                         | Summ                                                                                                                                           | nary                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 6.6                                                         | Summ                                                                                                                                           | iai y                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7 |                                                             |                                                                                                                                                | Inductive Verification of Simulink Models 133                                                                                                                                                                                                                                                                                                                                                                                       |

| 7 |                                                             | omatic                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7 | Aut                                                         | omatic                                                                                                                                         | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications                                                                                                                                                                                                                                                                                                                               |

| 7 | Aut                                                         | omatic<br>Auton<br>7.1.1                                                                                                                       | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications                                                                                                                                                                                                                                                                                                                               |

| 7 | Aut                                                         | omatic<br>Auton<br>7.1.1<br>7.1.2                                                                                                              | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications                                                                                                                                                                                                                                                                                                                               |

| 7 | <b>Aut</b><br>7.1                                           | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing                                                                                                   | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications                                                                                                                                                                                                                                                                                                                               |

| 7 | <b>Aut</b><br>7.1<br>7.2                                    | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing                                                                                                   | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications       133         Inductive Invariant Checking       134         k-Induction       136         g for k-Induction       138                                                                                                                                                                                                    |

| 7 | <b>Aut</b><br>7.1<br>7.2                                    | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton                                                                                          | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications       133         Inductive Invariant Checking       134         k-Induction       136         g for k-Induction       138         natic Generation of Verification Goals       139                                                                                                                                           |

| 7 | <b>Aut</b><br>7.1<br>7.2                                    | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1                                                                                 | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications       133         Inductive Invariant Checking       134         k-Induction       136         g for k-Induction       138         natic Generation of Verification Goals       139         Encoding Over- and Underflow Checks       141                                                                                     |

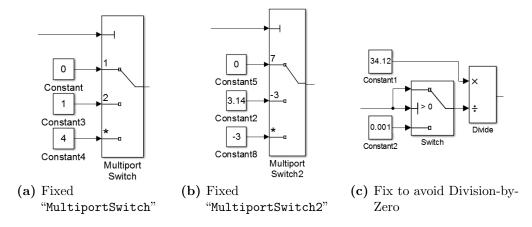

| 7 | <b>Aut</b><br>7.1<br>7.2                                    | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2                                                                        | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications       133         Inductive Invariant Checking       134         k-Induction       136         g for k-Induction       138         natic Generation of Verification Goals       139         Encoding Over- and Underflow Checks       141         Encoding Division-by-zero Checks       141                                  |

| 7 | <b>Aut</b><br>7.1<br>7.2                                    | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4                                                      | Inductive Verification of Simulink Models       133         natic Generation of Formal Specifications       133         Inductive Invariant Checking       134         k-Induction       136         g for k-Induction       138         natic Generation of Verification Goals       139         Encoding Over- and Underflow Checks       141         Encoding Division-by-zero Checks       142                                  |

| 7 | <b>Aut</b><br>7.1<br>7.2<br>7.3                             | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4                                                      | Inductive Verification of Simulink Models133natic Generation of Formal Specifications133Inductive Invariant Checking134k-Induction136g for k-Induction138natic Generation of Verification Goals139Encoding Over- and Underflow Checks141Encoding Division-by-zero Checks142Other Verification Goals143                                                                                                                              |

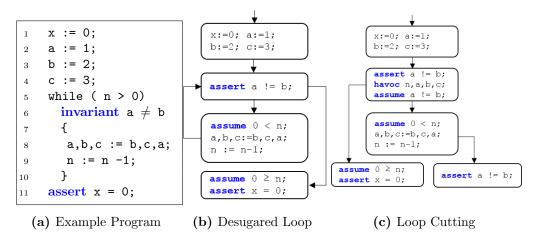

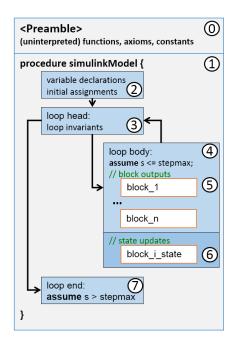

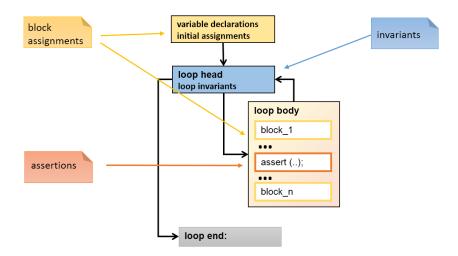

| 7 | <b>Aut</b><br>7.1<br>7.2<br>7.3                             | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>Loop                                              | Inductive Verification of Simulink Models133natic Generation of Formal Specifications133Inductive Invariant Checking134k-Induction136g for k-Induction138natic Generation of Verification Goals139Encoding Over- and Underflow Checks141Encoding Division-by-zero Checks141Encoding Range Violation Checks142Other Verification Goals143Invariants143                                                                               |

| 7 | <b>Aut</b><br>7.1<br>7.2<br>7.3                             | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>Loop 1<br>7.4.1<br>7.4.2                          | Inductive Verification of Simulink Models133natic Generation of Formal Specifications133Inductive Invariant Checking134k-Induction136g for k-Induction138natic Generation of Verification Goals139Encoding Over- and Underflow Checks141Encoding Division-by-zero Checks142Other Verification Goals143Invariants143Automatically Generated Invariants144                                                                            |

| 8 | <b>Aut</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5               | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>Loop 1<br>7.4.1<br>7.4.2                          | Inductive Verification of Simulink Models133natic Generation of Formal Specifications133Inductive Invariant Checking134k-Induction136g for k-Induction138natic Generation of Verification Goals139Encoding Over- and Underflow Checks141Encoding Division-by-zero Checks141Encoding Range Violation Checks142Other Verification Goals143Invariants143Automatically Generated Invariants145nary146                                   |

|   | <b>Aut</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5               | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>Loop<br>7.4.1<br>7.4.2<br>Summ                    | Inductive Verification of Simulink Models133natic Generation of Formal Specifications133Inductive Invariant Checking134k-Induction136g for k-Induction138natic Generation of Verification Goals139Encoding Over- and Underflow Checks141Encoding Division-by-zero Checks141Encoding Range Violation Checks142Other Verification Goals143Invariants143Automatically Generated Invariants145nary146                                   |

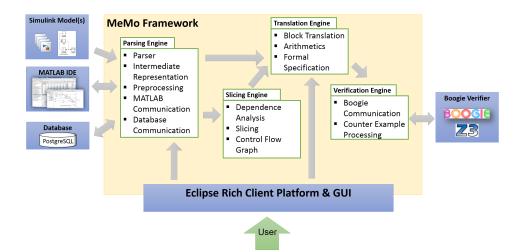

|   | <b>Aut</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br><b>Imp</b> | omatic<br>Auton<br>7.1.1<br>7.1.2<br>Slicing<br>Auton<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>Loop<br>7.4.1<br>7.4.2<br>Summ<br>lement<br>The M | Inductive Verification of Simulink Models133natic Generation of Formal Specifications133Inductive Invariant Checking134k-Induction136g for k-Induction138natic Generation of Verification Goals139Encoding Over- and Underflow Checks141Encoding Division-by-zero Checks141Encoding Range Violation Checks142Other Verification Goals143Invariants143Automatically Generated Invariants144Manually Specified Invariants146ration147 |

|                  |                 | 8.2.2    | Enhancement with Run-time Information                                                                |   |   | 149 |

|------------------|-----------------|----------|------------------------------------------------------------------------------------------------------|---|---|-----|

|                  |                 | 8.2.3    | Preprocessing                                                                                        |   |   | 150 |

|                  |                 | 8.2.4    | Persisting the Parsed Model                                                                          |   |   | 151 |

| 8                | 3.3             | Slicing  | Engine                                                                                               |   |   | 151 |

| 8                | 3.4             | Transla  | ation Engine                                                                                         |   |   | 151 |

|                  |                 | 8.4.1    | BlockTranslatorFactory                                                                               |   |   | 152 |

|                  |                 | 8.4.2    | ${\rm ArithmeticsMapping}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ |   |   | 152 |

|                  |                 | 8.4.3    | BoogieModel                                                                                          |   |   | 152 |

| 8                | 3.5             | Verifica | ation Engine                                                                                         |   |   | 153 |

| 8                | 8.6             | Graphi   | ical User Interface of the MeMo Tool                                                                 |   |   | 153 |

| 8                | 8.7             | Summa    | ary                                                                                                  | • |   | 154 |

| 9 E              | -<br>Vali       | uation   |                                                                                                      |   |   | 155 |

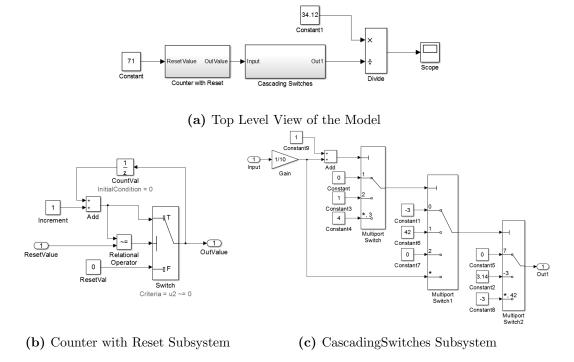

|                  | ).1             |          | $tudies \ldots \ldots$         |   |   |     |

| 0                | • •             | 9.1.1    | TestModel Design                                                                                     |   |   |     |

|                  |                 | 9.1.2    | Odometer                                                                                             |   |   |     |

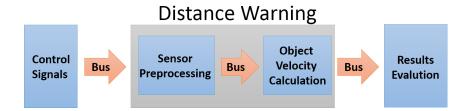

|                  |                 | 9.1.3    | Distance Warning (DistWarn)                                                                          |   |   |     |

|                  |                 | 9.1.4    | Additional Models for Slicing Evaluation                                                             |   |   |     |

| 9                | 0.2             |          | Evaluation                                                                                           |   |   |     |

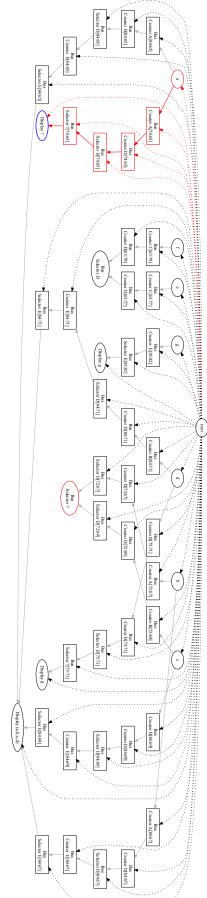

|                  |                 | 9.2.1    | Evaluation of Our Basic Slicing Technique                                                            |   |   |     |

|                  |                 | 9.2.2    | Evaluation of the Routing-aware Slicing Technique .                                                  |   |   |     |

| 9                | .3              | Verifica | ation Evaluation                                                                                     |   |   |     |

|                  |                 | 9.3.1    | TestModel                                                                                            |   |   | 165 |

|                  |                 | 9.3.2    | Odometer                                                                                             |   |   | 168 |

|                  |                 | 9.3.3    | DistWarn                                                                                             |   |   | 169 |

| 9                | .4              | Summa    | ary                                                                                                  |   |   | 171 |

| 10 0             | Conc            | clusion  | and Future Work                                                                                      |   |   | 173 |

|                  |                 |          | S                                                                                                    |   |   |     |

|                  |                 |          | sion                                                                                                 |   |   |     |

|                  |                 |          | $\mathbf{k}$                                                                                         |   |   |     |

| List             | of I            | Figures  |                                                                                                      |   | - | 181 |

|                  |                 | •        |                                                                                                      |   |   | 100 |

| List             | ot /            | Algorith | nms                                                                                                  |   |   | 183 |

| List             | of <sup>-</sup> | Tables   |                                                                                                      |   |   | 185 |

| List of Acronyms |                 |          |                                                                                                      |   |   |     |

| Bibliography     |                 |          |                                                                                                      |   |   |     |

## 1 Introduction

Nowadays, Model Driven Development (MDD) is a widely used software development technique, in particular for embedded systems. By enabling the specification of (software) systems using domain specific languages, both domain specialists and software engineers can work on the same model of a system. This reduces the development effort and avoids misunderstanding between these two groups. Furthermore, MDD enables the iterative refinement of models down to the implementation level while the models are executable (e.g., by simulation) in each design stage. This enables testing of the models in the early development stages where removing errors is much cheaper than in late stages of the development process. However, it is practically impossible to perform exhaustive testing for real world systems and, hence, testing is always incomplete. Moreover, embedded systems are often deployed in safety critical areas like in automotive or avionics industries, where an error may lead to severe injuries and even to death of persons. As a consequence, comprehensive and *complete* quality assurance measures are required for ensuring the correctness of such systems. Formal verification techniques are complete since they show the correctness of a model for all possible inputs and all possible scenarios. Hence, formal verification techniques that are applicable on models, in particular in early stages of the process, offer a great opportunity to increase the benefit of MDD, namely the early detection of errors, even more.

#### 1.1 Problem

In this thesis, we address the problem of automatically verifying discrete-time MATLAB/Simulink models that are used for the specification and development of embedded controllers. MATLAB/Simulink [Mat14a] is a de-facto standard for the development of embedded systems, especially in the automotive industry. Over the last decades, more and more functionality, e. g., assistant systems, were added to cars. Also, functionality previously implemented in hardware has been moved to the software level. Both led to an increase in the complexity of embedded systems and the controller software. Since this software is developed using models, the size of such models have increased accordingly. Existing automatic formal verification approaches like model checking suffer of

the state space explosion problem. In contrast, existing verification approaches that scale well with large state spaces are often less automated or rely heavily on user-given annotations.

#### 1.2 Objectives

In this thesis, we aim at providing an automated formal verification framework for discrete time MATLAB/Simulink models. Since the simulation semantics of MATLAB/Simulink is only informally defined in [Mat14b], a formal representation for MATLAB/Simulink models is required. This formal representation enables the use of formal verification methods to verify properties of the model, e.g., the absence of certain error classes like *run-time errors*. Both, the transformation as well as the verification of certain properties should be done automatically. Overall, we require our framework to fulfill the following criteria:

- Automation To reach a high degree of automation, the transformation of MATLAB/Simulink models into the formal specification has to be done fully automatically. This means that the translation should not require any user supplied annotations.

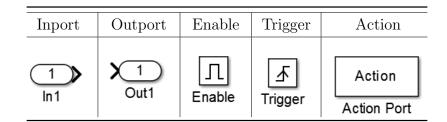

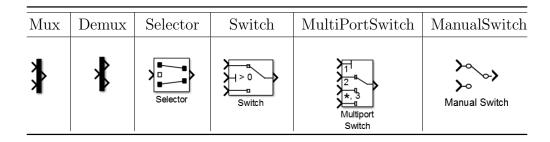

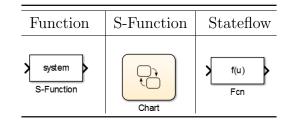

- Coverage Most of the frequently used blocks from the MATLAB/Simulink standard block library have to be supported by the transformation and verification. This mainly comprises blocks from the following block sets: Discrete, Logic and Bit Operations, Math Operations, Ports & Subsystems, Signal Routing, Sources and Sinks. The set of blocks should be extensible such that translation rules for further blocks can be easily added in the future.

- Verification Goals Verification goals have to be extracted automatically from the model for certain important error classes. Examples are *division-by-zero*, *range violations* and *over-* and *underflows*.

- Scalability Translation and verification should be possible on a standard computer system within time bounds acceptable for practical use. Hence, the verification technique that is used shall scale with possibly unbounded state spaces and large models.

- **Comprehensibility** The framework has to preserve the structural information of the original MATLAB/Simulink model. This is crucial to present verification results (like counterexamples) in a human-readable way.

- **Practicability** The framework should be applicable to real world industrial models.

#### **1.3 Proposed Solution**

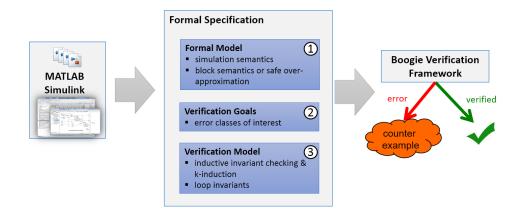

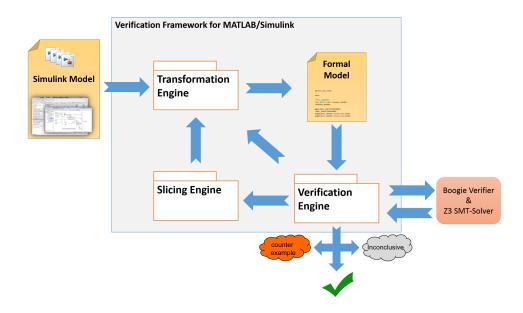

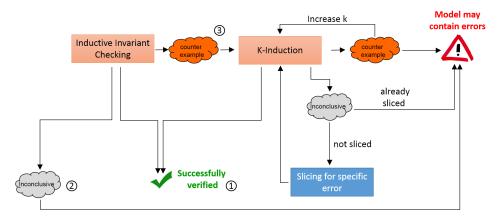

To achieve the objectives defined in the previous section, we propose a novel automatic verification framework for MATLAB/Simulink models. The key idea of our framework is a combination of *inductive invariant verification* using *automatic theorem proving*, more precisely the *Boogie verification framework* [BCD<sup>+</sup>06], and *slicing* to automatically verify properties of a given model.

In contrast to other automatic verification approaches like model checking or abstract interpretation, inductive verification techniques are less prone to the state space explosion problem since they do not explore state space from an initial state. Instead, the verification is done for a finite number of state transitions from an arbitrary start state. Moreover, the Boogie approach is based on *proof by contradiction* exploiting the power of modern, automatic theorem provers in finding a satisfying assignment. Hence, this technique is less prone to scalability issues and well suited to deal with large and even unbounded state spaces. Furthermore, we use automatic model reduction techniques to reduce the complexity and, hence, the state space of a model to achieve a higher scalability. To this end, we propose a *static slicing* method to reduce the model for a given point of interest, namely a block, and run the verification on the resulting slice.

A prerequisite for the application of formal verification and, hence, for automatic theorem proving, is the existence of a formal specification. Since the semantics of MATLAB/Simulink models as given in [Mat14b] is informal, we propose a transformation from MATLAB/Simulink into the *Boogie verification language (Boogie2)*. Boogie2 is semantically well defined and also serves as the input language to the Boogie verification framework. We use the sequential simulation semantics of MATLAB/Simulink according to a fixed-step discrete solver for our transformation, which matches the sequential semantics of the Boogie verification language. Due to the limitations of Boogie and the underlying theorem prover, some arithmetic operations as well as floating point numbers have to be over-approximated. However, the Boogie verification language is expressive enough to represent most of the block behavior and arithmetics in MATLAB/Simulink.

For both, the transformation as well as the slicing, it is necessary to calculate the data and control dependences in a MATLAB/Simulink model. For the transformation, these dependences are required to calculate the execution order of the blocks within a model according to the simulation semantics. For slicing, these dependences are used to determine the blocks that are part of a slice of a model. Hence, we propose a dependence analysis for MATLAB/Simulink models

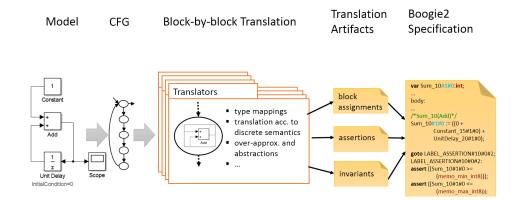

To achieve a high degree of automation, both the transformation and the verification of the MATLAB/Simulink models have to be fully automated. To meet this requirement, we introduce an automatic transformation engine that automatically calculates the block order of a MATLAB/Simulink model and translates the model block-wise into the Boogie verification language. For

the most common block types and their common parameter combinations, translation templates and rules are specified. In addition to the translation of blocks, we automatically create verification goals for the error classes *divisionby-zero*, *range violations* and *over-* and *underflows* depending on the type of the blocks. This enables the automatic verification for the absence of errors from these error classes using the Boogie verification framework. The translation is extensible to further properties.

In summary, we propose a verification method for MATLAB/Simulink which is both: *highly scalable* due to the use of inductive verification techniques and automatic model reduction techniques, and *highly automated* due to the automatic transformation of MATLAB/Simulink models into a formal model in the Boogie verification language and the automatic generation of verification goals. To show the practical applicability, we have developed our *MeMo tool suite*[HWS<sup>+</sup>11]. Besides parsing and slicing of the models, it also provides a fully automatic *push-button* verification of MATLAB/Simulink models. We evaluate our framework and our tool on a number of case studies supplied by our industrial partners.

#### 1.4 Motivation

The world is smart nowadays. There are smart phones, smart homes, smart watches, smart refrigerators, smart TVs and many more. All these devices are smart due to small integrated computing units and optionally, sensors, actuators and communication interfaces. They contain *embedded systems*.

Embedded systems are everywhere. Besides TVs, mobile phones or refrigerators, where they are used to increase our quality of living, they are also part of cars, trains, aircrafts, traffic management systems and other critical infrastructure. But, in contrast to a TV, a malfunction in a car, a plane or a traffic light control system may lead to costly damages, severe injuries and even to the loss of human lives. The latter class of embedded systems are *safety critical* systems. To ensure the correct functionality of these systems, comprehensive quality assurance methods have to be applied. In practice, this is mostly done by following a well-defined development process and guidelines and by testing.

A widely spread technique for the development of embedded systems, especially in automotive and avionic industries, is *model driven development*. In this technique, models are used as artifacts during all refinement phases of the development process and often, code is generated from the models by automatic code generators. These models are specified in a Domain-specific Modeling Language (DSML) that is tailored to the application domain and to a specific design phase. Often, these models are executable and enable the simulation of the models, which in turn, renders the testing of the models in all stages of the design process possible. With that, errors can be detected in the early design phases, which is usually less costly than in the late phases of the development.

MATLAB/Simulink is an integrated development environment widely used in industry for the development of embedded systems. Almost every big automaker and their external suppliers are using MATLAB/Simulink<sup>1</sup>. It provides the graphical DSML Simulink, which is tailored to the development of dynamical systems. The DSML is sufficient to model multiple steps of the design process. Simulation and testing of Simulink models is possible for every stage in the development process.

However, to show the absence of errors using testing, *exhaustive testing* (for all possible inputs) would be necessary. Thus, testing is incomplete. In contrast, formal verification techniques are well suited to *guarantee* the absence of errors. But this guarantee comes for a price: Formal verification techniques require a formal representation of the system and they either require a high degree of manual effort and scale well, or they are automated but are subject to scalability issues. This trade-off makes formal verification less attractive for practical use.

In this thesis, we present a formal verification framework that provides an automatic and scalable verification technique for MATLAB/Simulink models and enables the detection of errors in Simulink models, even in the early phases of the design process.

#### 1.5 Main Contributions

The main contributions of this thesis are:

- A dependence analysis and a slicing approach for MATLAB/Simulink models. This approach enables the static forward and backward slicing of MATLAB/Simulink models for a point of interest in the model, the *slicing criterion*. The approach uses a block as slicing criterion and the calculation of the slices is conservative and sound. Hence, it can be used as an automatic model reduction technique to split the verification problem into smaller sub-problems. We have published this approach in [RG12]

- A formal semantics for a subset of Simulink defined by a transformation into the Boogie verification language. This enables the use of the Boogie verification framework for the verification of MATLAB/Simulink models. The transformation is fully automatic and additionally to the semantically equivalent Boogie program, verification goals for common run-time errors are generated during the translation for all block types prone to these specific classes of errors. We have published this approach in [RG14a].

- An automatic verification framework for MATLAB/Simulink with tool support that shows the practical applicability of our approach and is integrated in our *MeMo tool suite*[HWS<sup>+</sup>11, RG14b].

<sup>&</sup>lt;sup>1</sup>http://www.mathworks.de/automotive/userstories.html

• A demonstration that our framework can be **applied to** automatically verify a number of **industrial case studies**. These case studies are an *odometer* and a *distance warning* system.

#### **1.6 Context of this Work**

This work has taken place in context of the  $MeMo^2$  project [HWS<sup>+</sup>11], which was funded by the Investitionsbank Berlin within the subsidy program for research, innovation and technology (Pro FIT). The project was carried out by the chair of Software Engineering for Embedded Systems and two industrial partners: Berner & Mattner Systemtechnik GmbH and Model Engineering Solutions GmbH. Within this project we have developed novel methods and analyses to ensure and asses the quality of MATLAB/Simulink models. Both companies are operating in the automotive area and offer consulting and quality assurance services to automakers and external suppliers. The key idea of the MeMo project was to provide both, analytical as well as constructive methods to ensure the quality of MATLAB/Simulink models. As a prerequisite, we have developed a parsing framework and a generic intermediate representation that serves as a basis for all further analyses. To improve the scalability of the analyses, we have developed a novel slicing approach [RG12] for MAT-LAB/Simulink models. As analytical method, we have developed a method for the automatic detection of certain error classes: a verification framework for MATLAB/Simulink using the Boogie verification framework [RG14a]. As constructive method, a quality model and metrics have been developed [HLW12] for MATLAB/Simulink.

#### **1.7** Overview of this Thesis

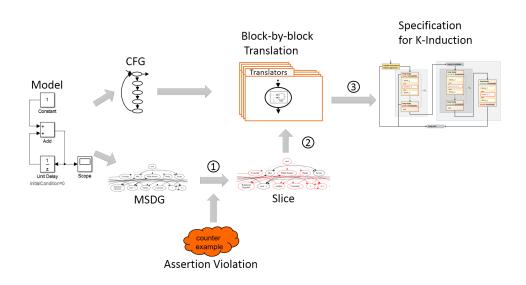

This thesis is structured as follows: In Chapter 2, we provide an overview of the background of this thesis. We start with an introduction of the general concepts of Model Driven Development and give a brief introduction into the MATLAB/Simulink tool suite and modeling notation. Then, we introduce the weakest precondition predicate transformer that, together with inductive techniques and automatic theorem proving, is used for the automatic verification of programs. Furthermore, we describe the Boogie verification framework that provides a formal language and a tool that we use in our approach. Finally, we briefly introduce program slicing. In Chapter 3, we discuss the related work of this thesis. In Chapter 4, we present our approach for the automatic formal verification of discrete-time MATLAB/Simulink models that is based on an automatic transformation of MATLAB/Simulink models into the Boogie2 verification language and uses slicing as an automatic model reduction technique to improve the scalability. In Chapter 5, we present our slicing approach for MATLAB/Simulink models based on dependence graphs constructed

<sup>&</sup>lt;sup>2</sup>Methods of Model Quality

using our dependence analysis. In Chapter 6, we present our transformation of discrete-time MATLAB/Simulink models into our formal model in the Boogie2 verification language where we also use the the dependence analysis to calculate the control flow graph for a model. In Chapter 7, we present our automatic verification approach based on inductive techniques and verification goals and invariants that we automatically generated during the translation of models. In Chapter 8 we give a brief overview of our implementation of the framework before we present our experimental results in Chapter 9 where we have applied our framework to some case studies. In Chapter 10, we conclude this thesis and discuss further directions for future work.

# 2 Background

In this chapter, we give background information regarding the languages and techniques used in this thesis and briefly introduce the tools used in our automatic verification framework for discrete-time MATLAB/Simulink models. First, we briefly introduce the paradigm of Model Driven Development in Section 2.1. Then we briefly describe the MATLAB/Simulink tool chain and the Simulink graphical modeling notation as an industrially used Model Driven Development approach in Section 2.2. Furthermore in Section 2.3, we give an overview to program verification with predicate transformers and introduce efficient techniques for the verification of programs using the weakest precondition predicate transformer and automatic theorem proving. Subsequently, we introduce the verification tool and language used in our approach. We give an introduction to the Boogie verification language and Boogie tool in Section 2.4. Finally, we give a brief introduction into static slicing techniques in Section 2.5.

#### 2.1 Model Driven Development and Engineering

In software development, models are used for various purposes. Models provide an abstraction of the reality with respect to some specific properties of interest. They are well suited to support communication between domain and software specialists or to enable the (partial) specification of a system or its behavior. In software engineering, models are traditionally used to describe certain features of a system like the architecture, the behavior, the components or the interfaces. However, models are not a driving element in the traditional software development process.

#### 2.1.1 Model Driven Engineering

In Model Driven Engineering (MDE) [Ken02, Sch06], models are used as a central element in the development process. MDE is a generalization of Model Driven Architecture (MDA)[MM<sup>+</sup>01]. MDA was introduced by the Object

Management Group (OMG)<sup>1</sup>. With MDA, the OMG defined an approach for the platform-independent specification of IT-systems based on the OMGecosystem of modeling languages (e.g., Unified Modeling Language (UML),) and middle-ware solutions. MDA separates models into three levels of abstraction:

- Computation Independent Model (CIM) The CIM is the layer for the domain practitioner and does not contain any information about the underlying IT-system.

- Platform Independent Model (PIM) The PIM is the layer that includes information about the underlying IT-system. However, the model is general enough to be applicable to any possible IT-architecture.

- Platform Specific Model (PSM) The PSM is the layer where specific information about a particular IT-architecture is included and used.

Furthermore, transformations are defined for refinement and abstraction between the layers (e.g.,  $PIM \rightarrow PSM$ ,  $PIM \rightarrow PIM$ , etc.).

More generally as proposed by Kent [Ken02], MDE-approaches have to specify

- (1) modeling languages and models,

- (2) transformations between models (and languages) and

- (3) a process that supports and coordinates the construction as well as the evolution of the models.

- (4) Furthermore, an adequate tooling needs to be present for a specific MDE approach

The tools have to support the correct syntactical use of the modeling languages, the transformation between models, the process in general and model-based testing, e.g., using the model to specify the inputs to the system. Finally, the tools have to support the working with instances of models, e.g., by simulation.

#### **Domain Specific Modeling Languages**

Since different application domains require models and processes that are especially tailored to the specific constraints and characteristics of the domain, Domain-specific Modeling Languages (DSMLs) are used to model the systems. DSMLs are either textual or graphical languages that, in contrast to *General Purpose Languages*, offer specialized features for their particular domain, but are of limited use for modeling systems outside the domain.

<sup>&</sup>lt;sup>1</sup>http://www.omg.org

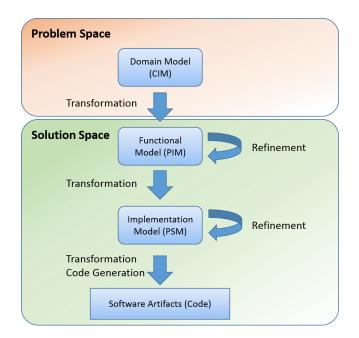

Figure 2.1: The MDD Process

#### 2.1.2 Model Driven Development

Model Driven Development (MDD) is a software development technique where models are the central artifacts in the software development process. The key idea of MDD is a process where, starting from an abstract model, model transformations are iteratively applied to the model. Finally, the implementation is generated from the models. In [BCW12], MDA is classified as a particular instance of MDD (for the OMG-ecosystem). MDD is a subset of MDE since MDE enables more general engineering than only for software.

#### The MDD Process

The generic process of MDD is depicted in Figure 2.1. Here, we differentiate between the *problem space* where a specific problem exists in its natural domain, and the solution space where the problem is mapped to a computational solution, e.g., a software system. In the problem space, the problem is modeled in its particular domain. The resulting model (CIM) is a physical or mathematical model of the system, e.g., a differential equation, usually designed by a domain specialist. Then, the model is transformed into a functional model (PIM) where a particular (computational) approach is chosen to solve the problem, e.g., an approximation technique for the differential equa-With this transformation, the solution space is entered. The PIM then tion. may undergo a number of refinement (e.g., refinement of the approximation technique) and abstraction (e.g., different views of the system) steps. However, at this point the model does not contain any implementation details and the model (and the modeling language used) is focused on functional aspects of the system. Subsequently, the model is transformed into an implementation model (PSM) where platform and implementation specific details are set. Again, on the PSM-layer, refinement and abstraction steps are possible to model different aspects of the system. Finally, the implementation model is transformed into source code and other artifacts. Transformation steps are either performed manually or automatically depending on the tool support. In practice, automatic code generators are widely used for the last transformation step.

Besides the process that describes the iterative refinement of models from CIM to PSM, MDD also enables quality assurance techniques (especially testing) in the early development stages.

#### Simulation, Testing and Verification

Besides syntactical checks, editing support and the automation of transformations between or within the modeling languages, MDD tools need to be able to execute the models. Selic [Sel03] names the executability of models as an important factor for the success of MDD since it enables understanding the system by experimentation. Furthermore, the tools need to provide a run-time environment where the simulation of the models can be started, stopped or resumed and steered with input sequences to the models.

The ability to simulate models with specific inputs or input sequences results in an important benefit of MDD: *The models are testable*. The correct functionality of a system can be tested at early stages in the development process. Moreover, the test cases (e.g., input sequences for the models) may be reused in later refinement stages. If the simulation environment supports the integration of (legacy) code, it can be reused even for testing the final software artifacts. Many testing techniques transferred from programing languages can be applied to the model level. Tests and test sequences showing the *correct functionality* of the model can be derived from the requirements specification. The input vectors can be tested systematically using techniques like *equiva lence partitioning* and *boundary value analysis*. Furthermore, the models can be tested for run-time errors and domain specific errors. Even *agile* development techniques like *test-driven modeling* [Zha04] are possible where tests are created prior to the actual modeling of the system.

However, testing mostly covers the possible inputs for a model only partially and, hence, it is inherently incomplete. To show the absence of run-time errors or safety properties, complete techniques like formal verification are needed. However, due to the fact that different MDD approaches consider different modeling languages with different execution semantics, formal verification approaches have to be especially tailored to particular modeling languages.

#### 2.1.3 Summary

In this section, we have briefly introduced Model Driven Development as a subset of Model Driven Engineering. Furthermore, we have presented the

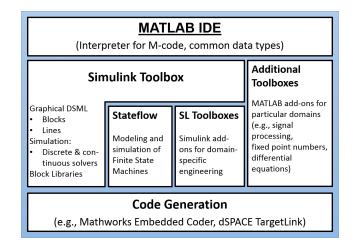

Figure 2.2: The MATLAB Architecture

generic process of MDD and the different levels (and views) of abstraction. Finally, we have presented the benefits of MDD especially for quality assurance in the early stages of the development process and motivated the need for verification techniques tailored to the specific modeling languages. In the next section, we introduce the MDD tool MATLAB/Simulink. It provides both, the graphical modeling notation *Simulink* and the MATLAB/Simulink tool that enables the editing and simulation of Simulink models.

#### 2.2 MATLAB/Simulink

MATLAB by Mathworks<sup>2</sup> is a tool that enables numerical computing and visualization of mathematical problems. The core features of the MATLAB tool are matrix manipulations, numerical simulations, plotting of functions and data, programming and development of algorithms and even the development of user interfaces. The name MATLAB originates from the first: *MATrix LAB*oratory. For the development of algorithms and user interfaces, a programming language MATLAB Code (M-code) is provided and interpreted by the MAT-LAB environment. However, MATLAB also offers interfaces or native support for other programming languages like C/C++ or Java.

The functionality of MATLAB can be extended by add-ons, which are called *toolboxes*. Toolboxes exist for various purposes (e.g., image processing, statistics, finance, biology, control systems) and offer functions, user-interface elements and data types for the particular domain. Figure 2.2 shows the architecture of the MATLAB environment. These toolboxes either extend the functionality of the MATLAB tool or further extend a certain toolbox. For example, the *Simulink* toolbox extends MATLAB by editing and simulation facilities while the *Stateflow* toolbox extends Simulink. Finally, there exists a number of toolboxes for automatic code generation. In the following sec-

<sup>&</sup>lt;sup>2</sup>http://www.mathworks.de/products/matlab/

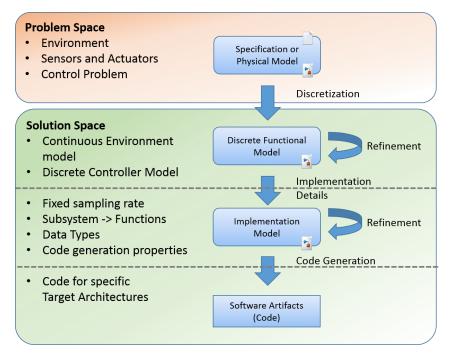

Figure 2.3: The MDD Process in Simulink

tion we introduce the Simulink toolbox and notation which provides an MDD environment for the domain of embedded controllers.

#### 2.2.1 Simulink

MATLAB/Simulink [Mata, Matb] is a particular toolbox that enables the graphical modeling and simulation of synchronous reactive embedded systems. The Simulink toolbox provides the graphical DSML Simulink, an editing framework for the Simulink models and a simulation engine that is able to simulate the model with sampling or different numeric techniques.

The DSML Simulink is a data flow oriented block diagram notation which consists of blocks and lines. Blocks represent either some kind of functionality, like mathematical or logical functions, or are used for structuring the model. Lines are used to represent signal flow between blocks.

MATLAB/Simulink provides a block library of about 300 predefined blocks. Further toolboxes for MATLAB/Simulink extend these libraries by adding blocks for particular domains, e. g., the *Aerospace Blockset* or the *SimHydraulics* toolboxes. Moreover, the *Stateflow* toolbox adds a whole event- and state-based modeling language to MATLAB/Simulink, which enables the modeling of complex decision logic in Simulink models using finite state machines.

MATLAB/Simulink can be used to model both, *discrete* embedded controllers as well as *continuous* physical environments the controller is deployed on. It enables the model driven development for the software of embedded controllers. Figure 2.3 depicts the MDD process for MATLAB/Simulink. Analogously to the generic MDD process, the control problem is specified in its particular domain. To this end, MATLAB/Simulink offers a number of blocks representing common (continuous) functions from control engineering and blocks for modeling (or approximate) the continuous time environment and sensors. Then, the model is refined using discretized blocks representing the discrete version of the functions from control engineering. Note that MATLAB/Simulink is always able to simulate continuous and discrete parts of the model together. With subsequent refinement steps, discrete sampling rates are defined for the controller and more implementation details are added to the controller. Finally, code is generated for the refined model.

In the next two sections we give a brief introduction to the model elements and the simulation of models in Simulink. Note that a more detailed discussion about block semantics and simulation semantics is given in Chapter 6.

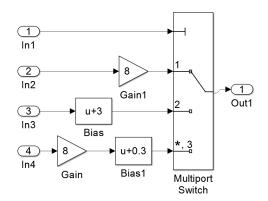

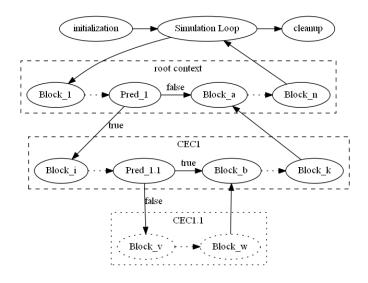

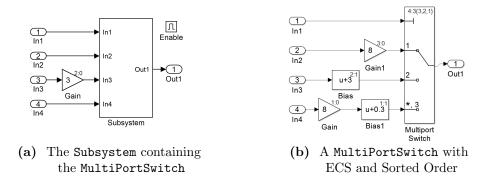

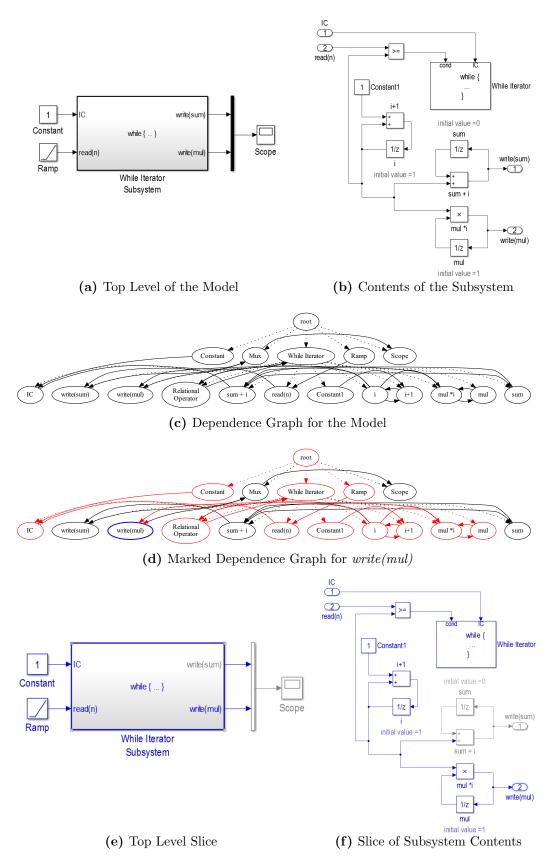

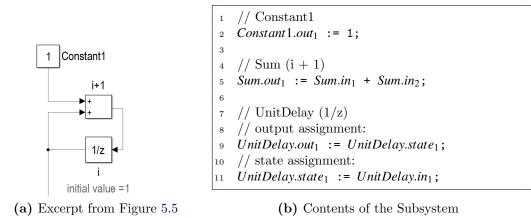

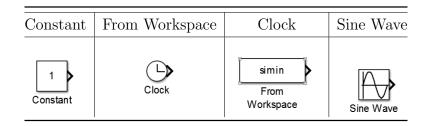

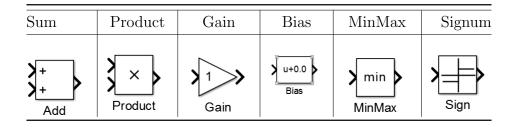

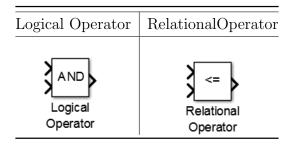

#### 2.2.2 Model Elements and Simulation Mechanics