Fakultät für Elektrotechnik und Informatik Institut für Softwaretechnik und Theoretische Informatik Lehrstuhl für Security in Telecommunications

## On the Physical Security of Physically Unclonable Functions

vorgelegt von Shahin Tajik (M.Sc.) geb. in Teheran, Iran

von der Fakultät IV- Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) genehmigte Dissertation

#### **Promotionsausschuss:**

Vorsitzender: Prof. Dr.-Ing. Sebastian Möller, Technische Universität Berlin Gutachter: Prof. Dr. Jean-Pierre Seifert, Technische Universität Berlin Gutachter: Prof. Mark M. Tehranipoor, Ph.D., University of Florida

Gutachter: Prof. Patrick Schaumont, Ph.D., Virginia Tech

Tag der wissenschaftlichen Aussprache: 18. August 2017

Berlin 2017

# Declaration of Authorship

Ich versichere an Eides statt, dass ich diese Dissertation selbständig verfasst und nur die angegebenen Quellen und Hilfsmittel verwendet habe.

| Signed: |  |  |  |

|---------|--|--|--|

|         |  |  |  |

| Date:   |  |  |  |

Dedicated to my family

The primary results of this work have been presented in the following publications:

- Tajik, S., Nedospasov, D., Helfmeier, C., Seifert, J.-P., Boit, C.: *Emission Analysis of Hardware Implementations*. In Proceedings of 17<sup>th</sup> Euromicro Conference on Digital System Design (DSD), IEEE, 2014, Verona, Italy

- Tajik, S., Dietz, E., Frohmann, S., Seifert, J.-P., Nedospasov, D., Helfmeier, C., Boit, C., Dittrich, H.: *Physical Characterization of Arbiter PUFs*. In Proceedings of 16<sup>th</sup> International Workshop on Cryptographic Hardware and Embedded Systems CHES 2014, Busan, South Korea

- Tajik, S., Lohrke, H., Ganji, F., Seifert, J.-P., Boit, C.: Laser Fault Attack on Physically Unclonable Functions. In Proceedings of Workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC), IEEE, 2015, St. Malo, France

- Lohrke, H., **Tajik**, **S.**, Boit, C., Seifert, J.-P.: No Place to Hide: Contactless Probing of Secret Data on FPGAs. In Proceedings of 18<sup>th</sup> International Conference on Cryptographic Hardware and Embedded Systems CHES 2016, Santa Barbara, USA

- Tajik, S., Dietz, E., Frohmann, S., Dittrich, H., Nedospasov, D., Helfmeier, C., Seifert, J.-P., Boit, C., Hübers, H.W.: *Photonic Side-channel Analysis of Arbiter PUFs*. Journal of Cryptology, Springer-Verlag, 2017

- Tajik, S., Fietkau, J., Lohrke, H., Seifert, J.-P., Boit, C.: *PUFMon: Security Monitoring of FPGAs using Physically Unclonable Functions*. accepted for 23<sup>rd</sup> IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS), IEEE, 2017, Thessaloniki, Greece

Additionally, Shahin Tajik has authored the following publications:

- Helfmeier, C., Nedospasov, D., Tajik, S., Boit, C., Seifert, J.-P.: Physical Vulnerabilities of Physically Unclonable Functions. In Proceedings of Design, Automation, and Test in Europe Conference and Exhibition DATE 2014, Dresden, Germany

- Ganji, F., **Tajik, S.**, Seifert, J.-P.: Why Attackers Win: On the Learnability of XOR Arbiter PUFs. In Proceedings of 8<sup>th</sup> International Conference on Trust and Trustworthy Computing TRUST 2015, Heraklion, Greece

- Ganji, F., **Tajik**, **S.**, Seifert, J.-P.: Let me prove it to you: RO PUFs are provably learnable. In Proceedings of 18<sup>th</sup> Annual International Conference on Information Security and Cryptology (ICISC), 2015, Busan, South Korea

- Ganji, F., Krämer, J., Seifert, J.-P., Tajik, S.: Lattice Basis Reduction Attack against Physically Unclonable Functions. In Proceedings of 22<sup>nd</sup> ACM Conference on Computer and Communications Security – CCS 2015, Denver, USA

- Ganji, F., **Tajik**, **S.**, Seifert, J.-P.: *PAC learning of arbiter PUFs*. Journal of Cryptographic Engineering, Springer-Verlag, 2016

- Boit, C., Tajik, S., Scholz, P., Amini, E., Beyreuther, A., Lohrke, H., Seifert, J.-P.: From IC Debug to Hardware Security Risk: The Power of Backside Access and Optical Interaction. In Proceedings of 23<sup>rd</sup> International Symposium on the Failure Analysis of Integrated Circuits IPFA 2016, Marina Bay Sands, Singapore

- Ganji, F., **Tajik, S.**, Fäßler, F., Seifert, J.-P.: Strong Machine Learning Attack Against PUFs with No Mathematical Model. In Proceedings of 18<sup>th</sup> International Conference on Cryptographic Hardware and Embedded Systems CHES 2016, Santa Barbara, USA

- Lohrke, H., Tajik, S., Scholz, P., Boit, C., Seifert, J.-P.: Automated Detection of Fault Sensitive Locations for Reconfiguration Attacks on Programmable Logic. In Proceedings of 42<sup>nd</sup> International Symposium for Testing and Failure Analysis – ISTFA 2016, Fort Worth, USA

- Ganji, F., Tajik, S., Fäßler, F., Seifert, J.-P.: Having No Mathematical Model May Not Secure PUFs. Journal of Cryptographic Engineering, Springer-Verlag, 2017

#### Abstract

Reconfigurable hardware is the primary component of electronic embedded devices employed in several applications ranging from wireless communication to cloud computing. Due to their significant role these modern platforms are targets of intellectual property (IP) piracy and tampering. Cloning of a design or manipulation of its content is carried out by conducting physical attacks (e.g., side-channel analysis and fault attacks) against these devices. Although different countermeasures against physical attacks have been integrated into the modern reconfigurable hardware, a proper protection mechanism on these platforms against semi-invasive attacks conducted from the chip backside is still missing. The main and foremost reason that the chip backside protection is ignored by the vendors is the misconception that semiinvasive attacks cannot be scaled to the very latest nanoscale technologies without further effort and cost. Moreover, it is assumed that integrating novel hardware intrinsic-based solutions for key storage, such as Physically Unclonable Functions (PUFs), make the conventional semi-invasive memory readout techniques virtually impossible.

In this work, we investigate the susceptibility of Intrinsic PUF implementations on reconfigurable hardware to optical semi-invasive attacks from the chip backside. We conduct different classes of optical attacks, particularly photonic emission analysis, laser fault injection, and optical contactless probing. By applying these techniques, we demonstrate that the secrets generated by a PUF can be predicted, manipulated or directly probed without affecting the behavior of the PUF. We further discuss the cost and feasibility of launching such attacks against the very latest hardware technologies in a real scenario. We discuss why PUFs are not tamper-evident in their current configuration, and therefore, PUFs alone cannot raise the security level of key storage, as one would expect in the first place. Moreover, we review the potential and already realized countermeasures, which can remedy the security-related shortcomings of the PUFs and make them resistant to optical side-channel and optical fault attacks. Finally, by making a few modifications in the functionality of an existing PUF architecture, we present a prototype of a tamper-evident sensor for detection of optical contactless probing attempts.

### Zusammenfassung

Rekonfigurierbare Hardware ist die primäre Komponente von elektronischen Embedded-Geräten, die in mehreren Anwendungen eingesetzt werden. Aufgrund ihrer bedeutenden Rolle sind diese modernen Plattformen Ziele des geistigen Eigentums (IP) Piraterie und Manipulationen. Das Klonen eines Entwurfs oder Manipulations seines Inhalts wird durch das physikalischer Angriffe (z. B. Seitenkanalanalyse und Fehlerangriffe) gegen diese Chips durchgeführt. Obwohl verschiedene Gegenmaßnahmen gegen physikalische Angriffe in die moderne rekonfigurierbare Hardware integriert wurden, fehlt noch ein richtiger Schutzmechanismus auf diesen Plattformen gegen semiinvasive Angriffe, die von der Chip-Rückseite durchgeführt werden. Der wichtigste Grund dafür, dass der Chip-Rückseite-Schutz von den Herstellern ignoriert wird, ist der Missverständnis, dass semi-invasive Angriffe nicht auf die neuesten nanoskaligen Technologien ohne weitere Anstrengungen und Kosten skaliert werden können. Darüber hinaus wird davon ausgegangen, dass die Integration von neuartigen Hardware-intrinsischen Lösungen für Speicherung von Schlüsseln, wie Physically Unclonable Functions (PUFs), die konventionelle semi-invasive Speicherauslesungstechniken praktisch unmöglich macht.

In dieser Arbeit untersuchen wir die Anfälligkeit von Intrinsic PUF-Implementierungen auf rekonfigurierbare Hardware auf optische semiinvasive Angriffe von der Chip-Rückseite. Wir führen verschiedene Klassen von optischen Angriffen, insbesondere Photonenemissionsanalyse, Laserfehlerinduktion und optische kontaktlose Untersuchung durch. Durch die Anwendung dieser Techniken zeigen wir, dass die von einer PUF erzeugten Geheimnisse vorhergesagt, manipuliert oder direkt untersucht werden können, ohne das Verhalten der PUF zu beeinträchtigen. Wir diskutieren weiter über die Kosten und die Machbarkeit der Durchführung solcher Angriffe gegen die neuesten Hardwaretechnologien in einem realen Szenario. Wir diskutieren, warum PUFs in ihrer aktuellen Konfiguration nicht manipulationssicher sind, und deshalb können PUFs alleine die Sicherheitsstufe der Schlüsselspeicherung nicht erhöhen, wie man es an erster Stelle erwarten würde. Darüber hinaus prüfen wir die potenziellen und bereits realisierten Gegenmaßnahmen, die die sicherheitsrelevanten Mängel der PUFs beheben und gegen optische Seitenkanal- und optische Fehlerangriffe resistent machen können. Schließlich präsentieren wir einen Prototyp eines manipulationssicheren Sensors zur Erkennung optischer kontaktloser Untersuchung, indem wir einige Änderungen an der Funktionalität einer bestehenden PUF-Architektur vornehmen.

# Contents

| D            | eclar | ation of Authorship                  | iii                    |

|--------------|-------|--------------------------------------|------------------------|

| $\mathbf{A}$ | bstra | $\operatorname{\mathbf{ct}}$         | vii                    |

| Zι           | ısam  | menfassung                           | ix                     |

| Li           | st of | Figures                              | $\mathbf{x}\mathbf{v}$ |

| Li           | st of | Tables                               | vii                    |

| Li           | st of | Abbreviations                        | xix                    |

| 1            | Intr  | oduction                             | 1                      |

|              | 1.1   | Motivation and Background            | 1                      |

|              |       | 1.1.1 Reconfigurable Hardware        | 1                      |

|              |       | 1.1.2 Physical Attacks               | 2                      |

|              |       | 1.1.3 Physically Unclonable Function | 3                      |

|              | 1.2   | Problem Statement                    | 4                      |

|              | 1.3   | Scientific Contribution              | 6                      |

|              | 1.4   | Thesis Structure                     | 6                      |

| <b>2</b>     | Bac   | kground                              | 9                      |

|              | 2.1   | Physically Unclonable Functions      | 9                      |

|              |       | 2.1.1 Arbiter PUF                    | 10                     |

|              |       | 2.1.2 Ring-Oscillator PUF            | 12                     |

|              |       | 2.1.3 Are PUFs Tamper-Evident?       | 13                     |

|              | 2.2   | Reconfigurable Hardware              | 13                     |

|              |       | 2.2.1 Security during Configuration  | 14                     |

|              |       | 2.2.2 PUF Implementations on FPGAs   | 16                     |

|              | 2.3   | Semi-Invasive Attacks                | 17                     |

|              |       | 2.3.1 Photonic Emission Analysis     | 17                     |

|              |       | 2.3.2 Laser Fault Injection          | 17                     |

|              |       | 2.3.3 Optical Contactless Probing    | 18                     |

|              | 2.4   | Related Work                         | 19                     |

| 3            | Exp   | erimental Setup                      | 21                     |

|              | 3.1   | Devices under Test                   | 21                     |

|   |     | 3.1.1 Intel/Altera MAX V CPLD 2                           | 21      |

|---|-----|-----------------------------------------------------------|---------|

|   |     | 3.1.2 Intel/Altera Cyclone IV FPGA 2                      | 1       |

|   | 3.2 | Hardware Implementations                                  | 23      |

|   |     | 3.2.1 Standalone PUF Implementations 2                    | 23      |

|   |     | 3.2.2 Red Key Calculation                                 | 24      |

|   |     |                                                           | 25      |

|   | 3.3 |                                                           | 25      |

|   |     |                                                           | 25      |

|   |     |                                                           | 26      |

|   |     |                                                           | 31      |

| 4 | Pho | conic Side-Channel Analysis 3                             | 3       |

|   | 4.1 | Attack Scenario                                           | 3       |

|   |     | 4.1.1 Characterization of Multiplexer-based Arbiter PUF 3 | 5       |

|   |     | 4.1.2 Characterization of Inverter-based Arbiter PUF 3    | 37      |

|   | 4.2 | Results                                                   | 8       |

|   | 4.3 |                                                           | 0       |

|   |     |                                                           | 0       |

|   |     |                                                           | 1       |

|   |     | =                                                         | 2       |

|   |     |                                                           | 13      |

| 5 | Las | r Fault Injection 4                                       | 7       |

|   | 5.1 |                                                           | 17      |

|   |     |                                                           | 17      |

|   |     | 8                                                         | 1       |

|   | 5.2 | 9                                                         | 1       |

|   | 5.3 |                                                           | 3       |

|   |     |                                                           | 3       |

|   |     | · ·                                                       | 4       |

|   |     |                                                           | 55      |

| 6 | Opt | cal Contactless Probing 5                                 | 7       |

|   | 6.1 |                                                           | 8       |

|   |     | 6.1.1 Key Extraction                                      | 8       |

|   |     |                                                           | 60      |

|   | 6.2 |                                                           | 61      |

|   | 0.2 |                                                           | , i     |

|   |     | v                                                         | 3       |

|   | 6.3 |                                                           | 54      |

|   | 0.0 |                                                           | 54      |

|   |     | •                                                         | 55      |

|   |     | v v                                                       | ,.<br>6 |

|   | 6.4 |                                                           | 7       |

|   |     |                                                           |         |

| 37 | <b>T</b> 7 |

|----|------------|

| Λ  | v          |

|         | 6.4.2<br>6.4.3<br>6.4.4 | Requirements for PUFs as Sensors | 68<br>69<br>70<br>71 |  |

|---------|-------------------------|----------------------------------|----------------------|--|

| 7<br>Bi | 0.12.0                  | and Future Work                  | 75<br>78             |  |

# List of Figures

| 2.1  | Schematic of an Arbiter PUF                                                      | 10 |

|------|----------------------------------------------------------------------------------|----|

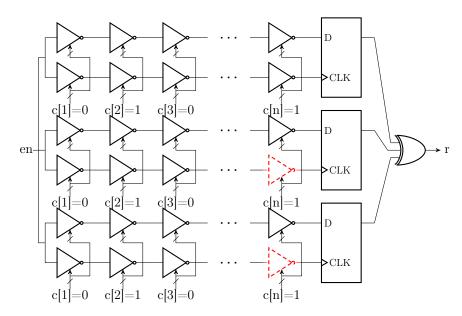

| 2.2  | Schematic of an XOR Arbiter PUF                                                  | 11 |

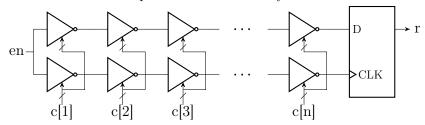

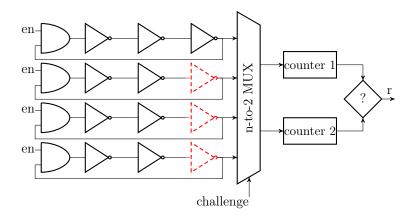

| 2.3  | Schematic of an RO PUF                                                           | 12 |

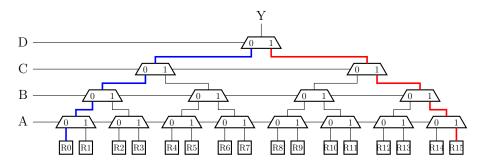

| 2.4  | Schematic of a 4-input Lookup Table                                              | 14 |

| 2.5  | Bitstream encryption                                                             | 15 |

| 2.6  | Fault injection into LUT configuration                                           | 18 |

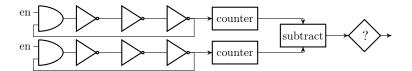

| 2.7  | Simplified illustration of LVP signal acquisition                                | 19 |

| 3.1  | Devices under Test                                                               | 22 |

| 3.2  | Realization of Arbiter PUF in reconfigurable hardware                            | 22 |

| 3.3  | Realization of Arbiter PUF stage in a LUT                                        | 23 |

| 3.4  | A ring-oscillator pair in the RO PUF construction                                | 24 |

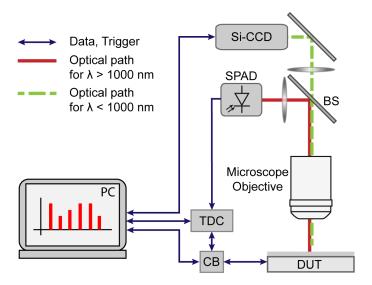

| 3.5  | Schematic of Photonic Emission Setup                                             | 26 |

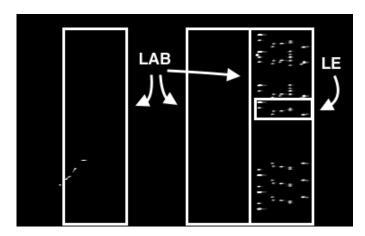

| 3.6  | Backside reflectance image of the CPLD                                           | 27 |

| 3.7  | Schematic of laser fault injection setup                                         | 29 |

| 3.8  | The sensitive regions of an LE to the LFI                                        | 29 |

| 3.9  | LFI against AND and XOR gates                                                    | 30 |

| 3.10 | Schematic of Laser Voltage Probing setup                                         | 31 |

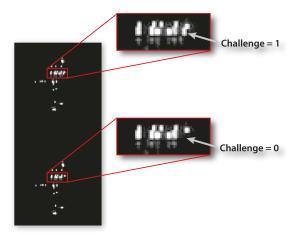

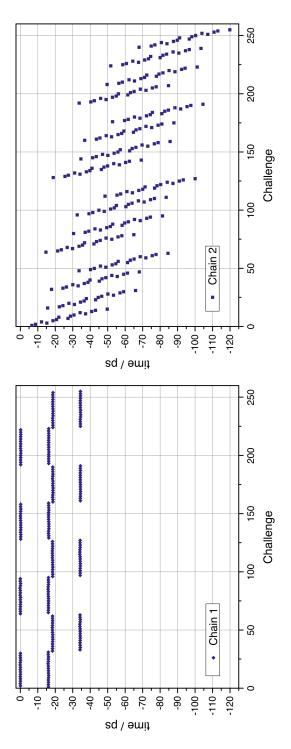

| 4.1  | Timing difference of two different challenges                                    | 34 |

| 4.2  | Optical emission of Arbiter PUF                                                  | 36 |

| 4.3  | Emission image of challenge bits                                                 | 37 |

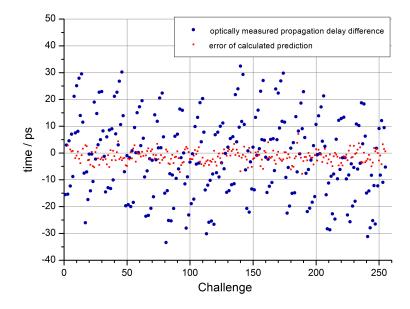

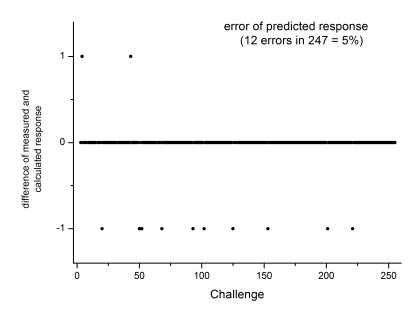

| 4.4  | Optical measurement of delays                                                    | 39 |

| 4.5  | Error of response prediction                                                     | 40 |

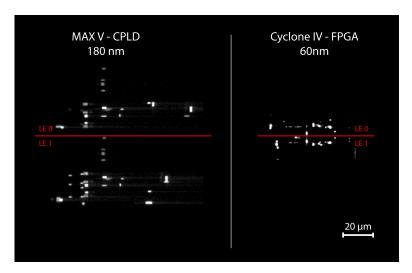

| 4.6  | Comparison of emission images in $180 \text{ nm}$ and $60 \text{ nm}$ chips $$ . | 42 |

| 4.7  | Electrical measurement of delays                                                 | 45 |

| 5.1  | Potential targets in an XOR Arbiter PUF                                          | 48 |

| 5.2  | Potential targets in an RO PUF                                                   | 50 |

| 5.3  | Photonic emission image of a ring-oscillator                                     | 52 |

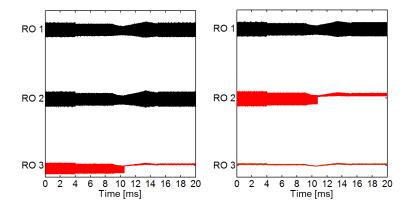

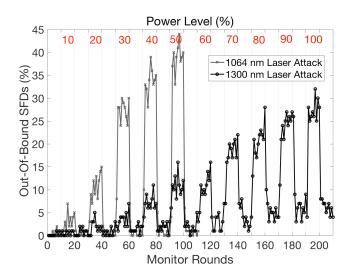

| 5.4  | Results of the LFI attack against RO PUF                                         | 53 |

| 5.5  | Results of the LFI attack against XOR Arbiter PUF                                | 54 |

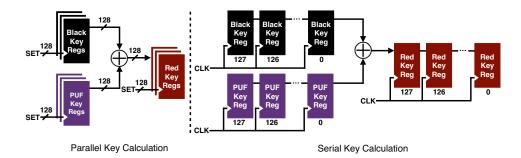

| 6.1  | Red key generation                                                               | 58 |

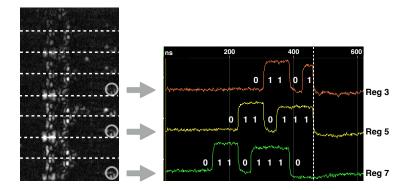

| 6.2  | Waveforms of key registers                                                       | 59 |

| 6.3  | Using LVI to extract the red key                                                 | 61 |

| 6.4  | Using LVP to extract the red key                                                 | 62 |

### xviii

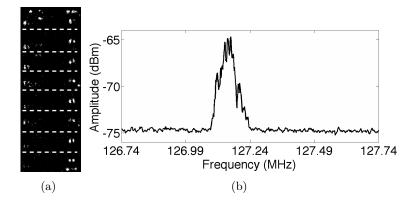

| 6.5 | Ring-oscillator localization and characterization | 63 |

|-----|---------------------------------------------------|----|

| 6.6 | Distributed RO sum PUF on FPGA                    | 68 |

| 6.7 | Performing LVI on RO sum PUF                      | 72 |

# List of Tables

| 4.1 PUF characterization result |  |

|---------------------------------|--|

|---------------------------------|--|

## List of Abbreviations

AES Advanced Encryption Standard

AI Artificial Intelligence APD Avalanche Photodiode

ASIC Application-Specific Integrated Circuit

BBRAM Battery-Backed Random Access Memory

BGA Ball Grid Array

BR Bistable Ring

BS Beam Splitter

CB Control Box

CCD Charged-Coupled Device CED Concurrent Error Detection

CMOS Complementary Metal-Oxide-Semiconductor

CPLD Complex Programmable Logic Device C-RAN Centralized-Radio Access Network

CRP Challenge Response Pair

**DUT** Device under Test

DPA Differential Power AnalysisDWC Duplication with Comparison

EM Electromagnetic

FFT Fast Fourier Transform

FIB Focused Ion Beam

FPGA Field Programmable Gate Array

FSBL First Stage Boot Loader

IC Integrated Circuit

IDE Integrated Development Environment

IoT Internet of ThingsIP Intellectual PropertyJTAG Joint Test Action Group

LE Logic Element

LAB Logic Array Block

LFI Laser Fault Injection

LSB Least Significant Bit

LSM Laser Scanning Microscope

LUT Lookup Table

LVI Laser Voltage Imaging

LVP Laser Voltage Probing

ML Machine Learning

MOS Metal-Oxide-Semiconductor

MSB Most Significant Bit NA Numerical Aperture

$\begin{array}{ll} \mathbf{nm} & \mathbf{nanometer} \\ \mathbf{NIR} & \mathbf{Near\text{-}Infrared} \end{array}$

NVM Non-Volatile Memory

PAC Probably Approximately Correct

PCB Printed Circuit Board

PEM Photonic Emission Analysis

PLD Programmable Logic Device

PLS Photoelectric Laser Stimulation

PoC Proof of Concept

PRNG Pseudo-Random Number Generator

ps picosecond

PUF Physical(ly) Unclonable Function

rms root mean square

RO Ring-Oscillator

RoT Root of Trust

SCASide-Channel AnalysisSEESingle Event Effects

SEM Scanning Electron Microscope SDN Software Defined Network

SoC System on Chip

SDR Software Defined Radio

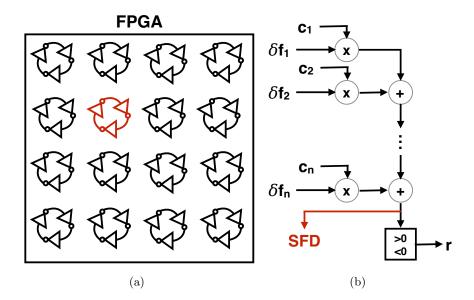

SFD Summation of the Frequency Differences

SPADSingle-Photon Avalanche DiodeSRAMStatic Random Access MemoryTDCTime-to-Digital ConverterTLSThermal Laser StimulationTMRTriple Modular Redundancy

TRNG True Random Number Generator

TQFP Thin Quad Flat Package

XOR Exclusive Or

## Chapter 1

## Introduction

### 1.1 Motivation and Background

Modern electronic embedded devices have become indispensable parts of our daily lives. End user devices, such as smartphones, smartwatches, and smart home appliances, gather data in an unprecedented way and make ubiquitous computing feasible. Moreover, industrial internet of things (IoT) consisting of robots, industrial controllers, and smart grids is the essential part of our modern infrastructure. More data accumulations at the edge are meaningless without deep learning and analysis of them in the cloud. Needless to say that devices at the edge communicate with data centers over a low-latency and high-speed telecommunication infrastructure comprised of routers and switches. While benefits of ubiquitous computing in our lives are indisputable, there are several concerns regarding the security of deployed electronic embedded devices in all parts of this huge network. A wide variety of utilized embedded devices in consumer, industrial and military applications are targets of reverse-engineering and Intellectual Property (IP) piracy. The primary motivation behind reverse-engineering is to get access to the stored secrets and utilized IPs on the integrated circuits (ICs) to counterfeit and overbuild the target products [91, 86]. Consequently, a great deal of attention has to be paid to protect the employed secrets and IPs on the embedded devices.

#### 1.1.1 Reconfigurable Hardware

Embedded systems can be developed either by software or hardware implementations. While in the former case the desired functionality is realized by running software on a microprocessor, in the latter case it is realized by application-specific integrated circuits (ASICs). Although developing software for a microprocessor is faster, updatable and less expensive in comparison to designing ASICs, the performance and the power efficiency of

microprocessors are inferior to ASICs. A third alternative for developing embedded systems is reconfigurable hardware, which combines the advantages of both software and hardware implementations. Complex Programmable Logic Devices (CPLDs) and Field Programmable Gate Arrays (FPGAs) are the most popular instances of reconfigurable hardware. These platforms can realize circuits from hundreds to millions of Boolean gates. CPLDs contain fewer configurable logic resources than FPGAs, and therefore, are preferred for realizing of lightweight applications. FPGAs, on the other hand, include conventionally more resources and are employed for applications, which require substantial processing powers. Furthermore, to get even more powerful platforms, FPGA vendors have made programmable System on Chips (SoCs), in which microprocessors are integrated into the FPGA fabrics.

Digital signal processing, software-defined radios (SDRs), and cryptography are a few examples of standard FPGA applications. Programmable SoCs are now integrated into the switches of software-defined networks (SDNs) to keep pace with changes in standards and protocols. Furthermore, they are considered as the core of centralized radio access network (C-RAN) in the 5G cellular networks. Embedded vision is another application of these platforms, which is helpful in autonomous cars, medical imaging, and video surveillance. More recently, internet giants start to integrate FPGAs and programmable SoCs into their cloud computing platforms to adapt their designs continuously to new artificial intelligence (AI) algorithms [1, 56].

Desired functionalities are configured and reconfigured on CPLDs, and FP-GAs by a binary data called bitstream. In contrast to CPLDs, most FPGAs do not contain any non-volatile memory (NVM) inside their packages. Due to the lack of an internal NVM inside most of these devices, they cannot store the bitstream internally. Hence, a bitstream has to be kept in an external NVM and sent to the FPGA in an untrusted field upon each power-on. The transmission of a bitstream in an adversarial environment can expose the design if no protection is provided. Bitstream encryption is a conventional countermeasure provided by the FPGA vendors to keep the design confidential [88]. In this case, available Battery Backed RAMs (BBRAMs) and eFuses on the FPGAs can be used to store the secret key for the decryption of the bitstream.

#### 1.1.2 Physical Attacks

To reverse-engineer a running application on a reconfigurable hardware, the attacker needs to reconstruct the implemented design. However, in a real attack scenario, the attacker might have access to neither the hardware description language (HDL) code nor the gate level netlist of application. Furthermore, the bitstream is not available to the attacker, since either the

bitstream is transferred encrypted between NVM and FPGA or it is kept in the internal NVM of the CPLDs and flash-based FPGAs. Thus, to get access to the design, the attacker needs to launch physical attacks.

Side-channel analysis (SCA) [52], fault injection attacks [9], and microprobing of the secret [33] are a few examples of the physical attacks, which can be conducted against embedded devices. SCA exploits the leakage of information during a cryptographic operation or key generation to extract the secret key. Power analysis and Electromagnetic (EM) analysis are examples of SCA methods, in which the attacker measure the electrical current and EM radiations from the chip, respectively. In the case of fault injection attacks, the attacker attempts to observe a faulty cryptographic operation or key generation by feeding the chip with faulty data or forcing it to operate in a non-valid condition. For instance, by varying the supplied voltage (i.e., voltage glitching), altering the frequency of the clock signal (i.e., clock glitching), or flipping bits in the memory with a laser beam (i.e., laser fault injection) the attacker can cause an erroneous operation of the target device.

A set of SCA and fault injection attacks can be carried out in a non-invasive way, i.e.; it is not required to remove the package of the IC under attack and only access to the pins of the device is required, which makes these attacks inexpensive. On the contrary, the first step to conducting an invasive attack is to remove the plastic or metallic package of the IC. Microprobing attacks enable the attacker to make a direct physical contact with the transistors and wires to extract the secrets. In this case, additional to the depackaging the barriers for a physical contact, namely the metal layers on the frontside of the IC or part of the silicon substrate on the IC backside, must be removed. Hence, these attacks are considered as fully-invasive techniques. However, to perform optical attacks, such as photonic emission analysis (PEM) or laser fault injection (LFI), no physical contact with the transistors is necessary. Although in principle semi-invasive attacks can be carried out from both frontside and backside of the IC, the existing multiple interconnected layers on the frontside of the modern ICs obstruct the optical paths from transistors to the surface of the device. This fact makes the analysis of the target IC from its backside more attractive to the attacker. In this fashion, if the proper photon wavelengths are deployed, thinning or polishing of the silicon substrate is not necessary anymore. Hence, these techniques are considered as semi-invasive.

#### 1.1.3 Physically Unclonable Function

Physically Unclonable Functions (PUFs) [66, 28] are introduced to mitigate the vulnerabilities of common key storage and key generation technologies to physical attacks on integrated circuits (ICs). On the one hand, PUFs exploit

the existing manufacturing process variations on the chips to create virtually unique fingerprints, which can be utilized for the device authentication, and consequently, preventing the counterfeiting. On the other hand, these variations can be used as an entropy source to generate keys for cryptographic primitives. In general, PUFs can be thought of as mappings, which produce a response for a given challenge. Using PUFs eliminate the need for an NVM, since no secret key is required to be permanently stored on the chip. In other words, a secret key or signature is generated by feeding the PUF with a set of challenges and activating it.

Among different classes of the PUFs, *Intrinsic* PUFs [48] can be effectively implemented on reconfigurable hardware without any extra manufacturing costs using the existing resources on these platforms. Bistable PUFs and delay-bases PUFs are the two main categories of Intrinsic PUFs. While the former group exploits the metastability of the bistable circuits (e.g., SRAM cells) as a fingerprint or an entropy source, the latter group utilizes the propagation delay differences of the symmetrically designed circuits on the chip to generate randomness and unique signatures.

An ideal PUF must have several features [48], including unclonability, unpredictability, and tamper-evidence (see chapter 2.1 for more details). While unclonability deals with the assumption that the behavior of a PUF is neither physically nor mathematically clonable, unpredictability deals with the inability of the attacker to predict the response of the PUF by observing a set of challenge-response-pairs (CRPs). Moreover, tamper-evidence means that if the attacker launches a semi- or fully-invasive attack against a PUF, the challenge-response behavior of the PUF is altered with a high probability leading to the destruction of PUF and loss of secret key or fingerprint.

PUFs can be employed on reconfigurable hardware to generate a key for decryption of an encrypted bitstream and bind it to a unique hardware. Besides, it can be used as the fingerprint of the reconfigurable hardware for authenticate purposes. The designers can deploy PUFs for their security applications as well, by including a PUF configuration in the bitstream.

#### 1.2 Problem Statement

It has been demonstrated that the bitstream encryption of different series of FPGAs are vulnerable to the SCA, and therefore, the secret key can be successfully recovered [60, 38, 61]. If no proper integrity checking mechanism is implemented for the encrypted bitstreams, bitstreams are vulnerable to fault injections as well, as the adversary can flip any arbitrary bits of the bitstream to inject a fault into the computation of the application [80]. Moreover, BBRAMs and eFuses of SRAM-based FPGAs, as well

as flash memory of CPLDs and flash-based FPGAs could be vulnerable to semi- and fully-invasive attacks [88]. Side-channel resistant decryptors, key rolling techniques, and asymmetric authentication schemes have been implemented on the most recent generations of FPGAs to assure the confidentiality and integrity of the bitstream against side-channel and fault injection attacks [67, 47]. Additionally, proprietary soft security monitoring IPs provided by FPGA vendors utilize the dedicated sensors inside the FPGAs to monitor the integrity of the device during runtime [92, 58]. However, a proper physical protection on the backside of these modern platforms is still missing to prevent semi- and fully-invasive attacks.

There are good reasons for reconfigurable hardware vendors to be less concerned about the security of the IC backside. First, the latest generations of the SRAM-based FPGAs are manufactured with 16 and 14 nm process technologies [32, 19]. It is believed that the conventional invasive attacks from the IC backside have limited resolution and cannot be scaled efficiently along with the trend of shrinking transistor technologies. However, in parallel to shrinking size of transistors high-resolution techniques have been developed in the failure analysis to debug the nanoscale technologies. This novel techniques can be deployed to mount an attack against the modern ICs.

Second, it is believed that PUFs raises the security level of the key storage on the reconfigurable hardware against invasive attacks [57, 67, 46] since no secret key is permanently stored on the chip to be read out by the attacker. Furthermore, it is assumed that PUFs are tamper-evident and any invasive attempt to characterize the PUF or probe the PUF responses destroys the PUF, which leads to the loss of the secret. The latter assumption is proved to be invalid since a set of attacks in the literature has been reported, which could break the security of a set of PUF architecture by semi-invasive and fully-invasive attacks [54, 34, 64].

Finally, it is assumed that semi-invasive attacks are much more expensive than other classes of attacks regarding equipment's cost and the required time for reverse-engineering Hence, vendors do not consider these attacks as a real threat to their products. While it is true that these attacks are more expensive than other conventional attacks, their cost is generally overestimated. In the literature different semi-invasive experimental setups have been demonstrated, whose costs are affordable for small-scale organizations. It is worth to mention the required setup can be rented from failure analysis labs or universities with an operator with a few hundred dollars per hour. Accordingly, these types of equipment are not necessarily to be possessed by the attacker.

#### 1.3 Scientific Contribution

The aim of this work is to demonstrate that only replacing the NVMs (i.e., flash memories, eFuses, and BBRAMs) with PUFs does not raise the security level of the reconfigurable hardware being vulnerable to semi-invasive attacks from the IC backside. In this work, we evaluate the security of different PUF instances in two separate scenarios: (i) a PUF instance is designed by the user in HDL as a part of a larger application and configured in the reconfigurable hardware via bitstream, (ii) a PUF is deployed either by the vendor or the user inside the FPGA to store part of a secret key, which is utilized to decrypt the encrypted bitstream. In the former scenario, we assume that the adversary has access to an open interface, where she can feed arbitrary challenges to the PUF and read out the responses of it non-invasively, In the latter scenario, no electrical and non-invasive access to the challenges and responses of the PUF is available to the attacker.

For the first scenario, we present two attacks against delay-based PUFs applying PEM and LFI techniques. First, we deploy the PEM technique to characterize and predict the behavior of a delay-based PUF. Next, we demonstrate how the LFI technique can be employed to launch a modeling attack against a delay-based PUF, which is resistant to modeling attacks. Besides, we show how an attacker can adversely affect the entropy of the responses of a PUF with the help of LFI. For the second scenario, we present an attack based on optical contactless probing, which enables the attacker to probe the responses of an arbitrarily chosen PUF. We evaluate the feasibility of all attacks by conducting them against Proof-of-Concept (PoC) PUF implementations in different reconfigurable hardware.

Based on the achieved results, we review possible protection schemes against the mounted attacks. Fortunately, in response to our presented PEM and LFI attacks effective countermeasures have been proposed and realized in the literature to protect the PUF. Moreover, we discuss why PUFs, in their current shapes, cannot be deployed as anti-tamper sensors against semi-invasive attacks. Hence, we propose a small modification to one of the existing Intrinsic PUF architectures to make it tamper-evident against optical contactless probing.

#### 1.4 Thesis Structure

This thesis is organized as follows: Chapter 2 presents background information on the PUFs, reconfigurable hardware, and semi-invasive attacks. Moreover, the related work is reviewed. In chapter 3, the utilized experimental setups for different experiments are presented. Chapter 4 introduces

7

the PEM attack against the delay-based PUFs. Chapter 5 presents the LFI attack against the delay-based PUFs. In chapter 6 an attack on PUFs based on optical contactless probing is introduced. Furthermore, the prototype of a PUF-based sensor for detection of optical probing attacks is presented. Finally, in chapter 7 we conclude the thesis and provide insights for future work.

## Chapter 2

# Background

In this chapter, we first review the definition of an ideal Physically Unclonable Function (PUF) and explore the functionality of two popular delay-based PUFs, namely Arbiter PUF and ring-oscillator (RO) PUF. Second, we study the internal architecture of reconfigurable hardware and discuss the security issues of FPGAs during configuration. Moreover, we survey the PUF implementations on these platforms. Afterward, we review the optical semi-invasive techniques, which are used in this work to attack PUF implementations on reconfigurable hardware. Finally, we review the related work in the literature. All provided background information in this chapter is previously presented in [85, 82, 84, 81, 45, 83].

## 2.1 Physically Unclonable Functions

Here we briefly describe the essential characteristics of an *ideal PUF*, and for a formal foundation and the formalization of the security of PUFs, we refer the reader to [8].

**Definition 1** Let  $C = \{0,1\}^n$  and  $\mathcal{Y} = \{0,1\}$  be the set of challenges and the set of responses, respectively. A PUF can be represented by the function  $f_{PUF}: C \to \mathcal{Y}$  where  $f_{PUF}(c) = y$ , cf. [50]. Note that  $f_{PUF}$  is not a one-to-one mathematical function. Ideally,  $f_{PUF}$  aims to provide the following security-related properties.

- 1. Evaluable:  $f_{PUF}$  can be evaluated in polynomial time.

- 2. Unique: for a given PUF instance, the mapping  $f_{PUF}$  is instance-specific.

- 3. Reproducible: applying same challenges to  $f_{PUF}$  results in "close" responses with respect to a chosen distance metric.

- 4. Unclonable: for a given PUF  $f_{PUF}$  it is (almost) impossible to construct another mapping (i.e., physical entity)  $g_{PUF}$  so that " $g_{PUF} \approx f_{PUF}$ ".

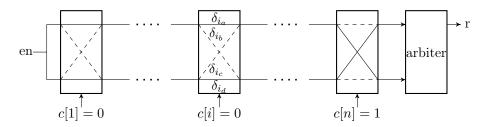

FIGURE 2.1: Schematic of an Arbiter PUF

- 5. Unpredictable: for a given set  $U = \{(c_i, y_i) \mid y_i = f_{PUF}(c_i)\}$ , it is (almost) impossible to predict a response  $y_r = f_{PUF}(c_r)$ , where  $c_r$  is a random challenge and  $(c_r, y_r) \notin U$ .

- 6. One-way: for a given random PUF instance  $y = f_{PUF}(c)$ , where c is drawn from a uniform distribution on  $\{0,1\}^n$ , we have

$$\Pr[\mathcal{A}(f_{PUF}(c)) = c] < 1/p(n),$$

where  $p(\cdot)$  is any positive polynomial. In other words, it is hard to find c, if the respective response of a random instance of the PUF family is known, and the adversary can evaluate the PUF a polynomial number of times [48].

7. Tamper evident: physical altering or modifications of the physical entity embedding  $f_{PUF}$  transforms it to  $f'_{PUF}$  such that with high probability  $f'_{PUF} \neq f_{PUF}$ .

The current types of PUFs can only partially fulfill the requirements mentioned above. Many different PUF architectures have been proposed in the literature. *Intrinsic* PUFs [48] are one of the primary and popular classes of the PUFs since they can be effectively implemented on the embedded devices without any additional manufacturing processes. Intrinsic PUFs can generally be classified into two distinct classes: bistable PUFs and delay-based PUFs [48]. The former is based on bistable circuits such as SRAM memory cells, while the latter relies on intrinsic differences in propagation delays of symmetrically designed wires and transistors on the chip. Arbiter PUF and RO PUF are two widely deployed delay-based PUFs in the reconfigurable hardware.

#### 2.1.1 Arbiter PUF

Arbiter PUF families exploit the slight delay differences of two symmetrically designed paths on the chip to generate binary responses [41]. A single Arbiter PUF consists of multiple serially connected stages and an Arbiter at the end of the chain, see Fig. 2.1. Each stage in this architecture contains two signal

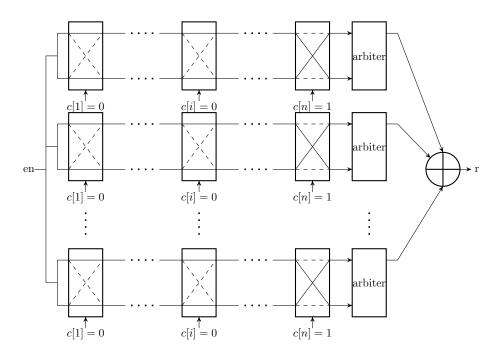

FIGURE 2.2: Schematic of an XOR Arbiter PUF

outputs, two signal inputs, and a single challenge input. The inputs of the first stage of the Arbiter PUF are connected to a common enable signal. By giving an electrical pulse as an enable signal, two signals propagate on two similar paths to the end of the chain. The signal propagates through the crossed paths inside a stage if the challenge input is set to 1. Otherwise, the direct paths are utilized. Although the nominal delays of direct paths and crossed paths are equal (i.e.,  $\delta_{i_a}=\delta_{i_d}$  and  $\delta_{i_b}=\delta_{i_c}$ ) the propagation delay on one of the paths can be longer or shorter due to imperfections on the chip. Hence, different challenges result in different propagation delays at the outputs of the last stage. Finally, regarding the arrival time of the signals on the outputs of the final stage, the Arbiter generates a binary response. The primary physical security assumption of an Arbiter PUF is that an attacker cannot measure the internal delays within the stages of the Arbiter PUF without destroying the PUF itself, i.e., changing its challengeresponse behavior. In this case, the attacker can only try challenges from an exponential space and observe the respective responses.

Due to its relatively large challenge space, Arbiter PUFs are considered promising candidates for authentication protocols [20]. However, it is known that Arbiter PUFs are vulnerable to machine learning (ML) attacks [41]. An attacker can model the internal delays of an Arbiter PUF by applying an ML algorithm to a set of CRPs. As a countermeasure, the XOR Arbiter PUF has been introduced to impair the effectiveness of ML attacks [79]. An XOR Arbiter PUF has k parallel Arbiter chains, each with n stages and an

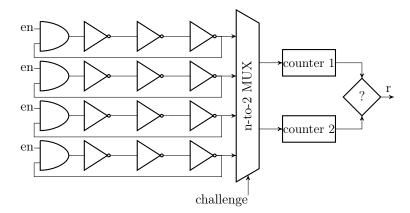

FIGURE 2.3: Schematic of an RO PUF

Arbiter, see Fig. 2.2. The joint binary response is generated by XOR-ing the responses of all individual Arbiter chains. In this case, only the joint response is available, and the responses of each single Arbiter PUF are hidden from the attacker. XOR Arbiter PUFs cannot be learned in a polynomial time if the number of Arbiter PUFs in this architecture are larger than a threshold [25].

#### 2.1.2 Ring-Oscillator PUF

RO PUFs [79] are another delay-based PUFs exploiting the intrinsic timing differences on the chip. A ring-oscillator circuit consists of an odd number of inverters gates and optionally an AND gate to activate or deactivate the circuit. An RO PUF consists of n independent ring-oscillators with the same number of gates, where all ring-oscillators are connected to an n-to-2 multiplexer, see Fig. 2.3. Although all ring-oscillators have the same lengths, their oscillation frequencies are slightly different due to the manufacturing process variations on the chip. By applying challenges to the multiplexer, a ring-oscillator pair is selected, and their outputs will be connected directly to the clock inputs of 2 binary counters. The counters count the number of the rising edges of the signals at the outputs of the ring-oscillators. Because of a difference in frequencies, counters deliver different values after a predefined period. Finally, a comparator compares the states of the counters and generate a binary response. The central physical security assumption of an RO PUF is that an attacker cannot precisely measure the oscillation frequencies of ring-oscillators and predict the outputs of the PUF.

#### 2.1.3 Are PUFs Tamper-Evident?

PUFs are believed to be tamper-evident against invasive attacks. tamper-evident against fully-invasive attacks have been experimentally verified for optical and coating PUFs [68, 89]. However, they cannot be integrated into most platforms without additional manufacturing steps, and therefore, they are not considered as Intrinsic PUFs [48]. Unfortunately, for Intrinsic PUFs, limited information on tamper-evidence is available in the literature. Fortunately, results on effects of semi-invasive analysis on circuits similar to delay-based PUFs can be found in the literature related to the failure analysis. It has been shown that mechanical stress from depackaging and substrate thinning have negligible effects on the absolute and relative frequencies of ring-oscillators [14]. In another experiment, it has been reported that removing most of the bulk silicon, down to the bottom of the n-wells, does not alter the delays of the inverter chains [74]. Moreover, different successful semi-invasive attacks have been reported on silicon intrinsic PUF instances without affecting the challenge-response behavior of the PUFs [54, 34, 64]. On the other hand, PUF developers do their best to mitigate the noisy responses of the PUF by different error correction techniques [49, 37]. Hence, if the physical tampering changes a few CRPs, they will be corrected by error correction methods. Consequently, semi-invasive attacks do not destroy the Intrinsic PUFs.

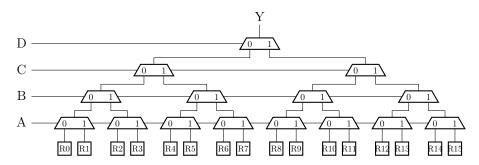

### 2.2 Reconfigurable Hardware

Programmable Lookup Tables (LUTs), registers, and routing switches are the basic components of programmable logic devices. Several LUTs, each with multiple inputs and one output, are responsible for the configuration of combinatorial logic functions. A 4-input LUT, which contains 16 SRAM cells can be seen in Fig. 2.4. The inputs of the LUT can be regarded as the addresses of SRAM cells, which access the stored values by multiple multiplexers. To realize sequential logic functions dedicated programmable registers can be utilized. Furthermore, routing of different signals between LUTs and registers is configured by programmable switches on the chip. CPLDs and FPGAs are popular popular instances of reconfigurable hardware. The architectures of modern CPLDs and FPGAs are virtually similar. However, the main architectural differences between these two devices are related to their logical sizes, routing complexities and dedicated peripherals. Generally, CPLDs contain less logical resources than FPGAs, and hence, are preferred for less complex computing applications.

Figure 2.4: Schematic of a 4-input Lookup Table

Reconfigurable hardware is programmed and configured by a bitstream, which is generated by an application designer. While CPLDs and flash-based FP-GAs have internal NVM to store configuration data in the same package, SRAM-based FPGAs do not contain any NVM inside the package, and therefore, are not capable of storing the bitstream [88]. Therefore, the bitstream has to be stored in an external NVM and loaded into the SRAM-based FP-GAs upon each power-on in an adversarial environment. Even if the firmware of CPLDs and flash-based FPGAs require updates, their upgraded bitstream has to be transmitted from an external NVM to the device in an untrusted field. Transferring bitstreams in plaintext can divulge the designs and IPs to an adversary. As a result, bitstreams have to be kept confidential.

#### 2.2.1 Security during Configuration

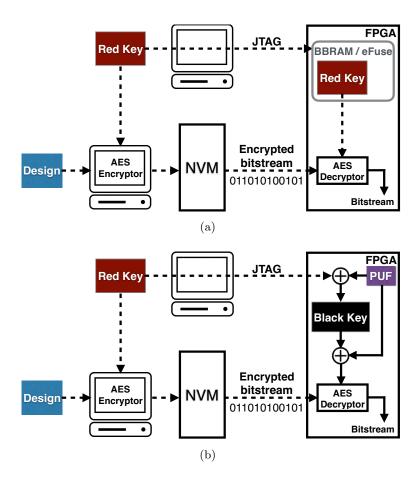

Bitstream encryption is a conventional solution to prevent the IP piracy during FPGA configuration. To enable the bitstream encryption a secret red key (i.e., an unencrypted key) is transferred to the FPGA in a safe environment, see Fig. 2.5(a). This key will be stored either in the BBRAM or eFuses inside the FPGA. At the same time, the application design is encrypted in the integrated development environment (IDE) software by the red key and stored in an external NVM. Each time the FPGA is powered up in the untrusted field, the encrypted bitstream is transmitted to the chip, and it will be decoded by a decryption core and the stored red key inside the chip. Although this technique raises the security of the bitstream transmission against interception, it has been demonstrated that the decryption cores on different FPGAs are vulnerable to EM and differential power analysis (DPA) [60, 38, 61]. Moreover, the key storage technologies on FPGAs such as eFuses are susceptible to semi-invasive attacks and can be read out with a scanning electron microscope (SEM) [88].

Utilizing updatable protected soft decryption cores, asymmetric authentication, and key rolling can defeat non-invasive side-channel attacks, such as DPA and EM analysis [67]. Moreover, PUFs [28, 66] can remedy the

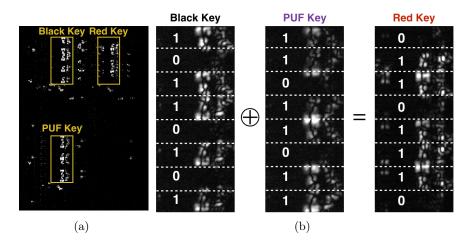

FIGURE 2.5: (a) Bitstream encryption and decryption using a red key [88]. (b) Bitstream encryption and decryption using a black key, PUF key and red key [67].

shortcomings of insecure storage in modern FPGAs [88]. PUFs can be used for secure key generation and key obfuscation in an untrusted environment, where the adversary has access to the device and is able to mount a physical attack. Additionally, PUFs can be deployed as unique identifiers to prevent cloning and spoofing [77, 29, 30, 47, 96]. In the latter case, the used IPs in the application design can be coded to operate only on a specific device.

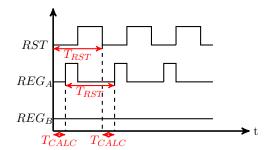

PUF and DPA-resistant decryptors can be realized either by dedicated logic inside the FPGA in the form of ASIC (i.e., hard cores) or by configuring the FPGA logic cells (i.e., soft cores). Although the principle of using PUFs for key obfuscation and DPA-resistant decryptors to defeat SCA are similar among different FPGA vendors, the implementation details differ. In this work, we explain the red key wrapping technique using soft PUFs and soft decryptors, which is deployed by Xilinx SoCs [67]. In the trusted field a boot loader containing the red key and a soft PUF IP is transferred into the

volatile configuration SRAM of the FPGA. After the boot loader is loaded, the PUF is configured on the programmable logic of the device, and its responses are used in conjunction with the red key to generate the *black key* [67], see Fig. 2.5(b). The black key generated in this way can only be converted back to the red key with the correct, chip-specific, internal-only PUF response (i.e., PUF key). Hence, the black key can then be stored safely in an insecure NVM, and the red key will only exist as volatile, internal-only data.

In the untrusted field, an encrypted first stage boot loader containing the black key, the same soft PUF IP, and a DPA-resistant decryption IP core is loaded into the device. The chip-specific PUF response is then used to unwrap the black key and generate the red key on the fly. In the second phase, the encrypted configuration bitstream is transferred to the device and will be decrypted by the red key inside the FPGA. In this case, the decryption IP core can be updated against future side-channel analysis threats. Furthermore, the soft PUF in conjunction with the black key provides volatile, internal-only and updatable key storage, and therefore, the red key is in memory only during the configuration of the device.

### 2.2.2 PUF Implementations on FPGAs

Current FPGA market leaders, namely Xilinx, Intel/Altera and Microsemi, have already started to integrate PUFs into their latest products [57, 67, 46]. Hard SRAM PUFs from Intrinsic-ID Inc. have been integrated into the Microsemi SmartFusion2, IGLOO2 and PolarFire FPGAs [57, 59]. A similar SRAM PUF from Intrinsic-ID Inc. is implemented on Intel/Altera Stratix 10 SoCs and FPGAs [46]. Recently, Verayo Inc., a delay-based PUF developer company, announced that it will provide Xilinx Ultrascale+ SoCs and FPGAs with their PUF technology [90]. Since Xilinx has patented previously a key generation technique based on hard RO PUFs [87], most probably the PUF will be an RO PUF variant. Currently, the Xilinx Zynq-7000 SoCs enables the user to implement soft PUF IP cores as well as DPA-resistant soft decryptor IPs to protect the red key during configuration [67]. Furthermore, selected Microsemi flash-based SmartFusion2 and IGLOO2 FPGAs can be utilized as a Root of Trust (RoT) to transfer soft PUF IP cores to target SRAMbased FPGAs for secure authentication [47]. Soft PUFs can be purchased from third-party developers, such as Verayo Inc. [4], Intrisic-ID Inc. [3], and Helion Technology Limited. [2].

# 2.3 Semi-Invasive Attacks

### 2.3.1 Photonic Emission Analysis

Complementary metal-oxide semiconductor (CMOS) ICs consist of individual n-type and p-type metal-oxide semiconductor (MOS) transistors connected to realize different logic gates. In any logical state of such a CMOS gate, the static current consumption is minimized because at least one transistor on the path between VDD and GND is in off region. Only during switching events, transistors pass through saturation for a short period. In saturation, MOS transistors emit photons due to carriers traveling through the space charge region near the drain diffusion [13]. The emission intensity depends on the applied voltages, conducted current, and time spent in saturation. Due to the different characteristics of holes and electrons, n-type transistors emit significantly more photons at the same conditions in comparison to p-type transistors. Hence, only changes in the logic state of n-type transistors will usually be visible during PEM.

In modern IC designs, multiple interconnect layers obstruct the optical path from the transistors drain region to the surface of the device. Hence, it is nearly impossible to observe photon emissions from the frontside of the chip. Nevertheless, photon emissions can also be observed through the silicon substrate of the IC backside. However, silicon is highly absorptive for the photons with higher energy than the bandgap energy, and therefore, near infrared (NIR) photons only will remain for analysis.

#### 2.3.2 Laser Fault Injection

Generating electron-hole pairs by passing a laser beam through silicon is called the photoelectric effect. This phenomenon is occurred only by photons, whose energies are greater than the silicon band-gap energy. However, similar to other optical attacks, the LFI attacks are preferred to be carried out from the IC backside through the silicon substrate. Hence, the laser wavelength must be chosen from the NIR spectrum.

Depending on the laser power and its spot location on the IC, the generated electron-hole pairs might be recombined and leave only a negligible effect on the behavior of the target IC [69]. However, if the right location and power are selected, they can cause a Single Event Effects (SEE) and create an electrical current [69]. In this fashion, having a laser shot at specific regions of a SRAM cell can flip the stored value in it.

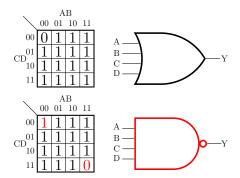

An attacker can use this principle to attack the SRAM-based LUTs of CPLDs and FPGAs. Inside the reconfigurable hardware the *n*-input SRAM-based

FIGURE 2.6: Fault injection into LUT configuration.

LUTs store  $2^n$  binary configuration values to realize n-input combinational logic functions, see Fig. 2.4. Thus, one can implement  $2^{(2^n)}$  different combinational logic functions within each LUT. It is clear that any changes in the state of the configuration bits of a LUT lead to a different logic function. An attacker can alter the logical function of a gate by inducing a fault into one or more SRAM cells of a target LUT. For instance, a 4-input OR gate is realized by storing 0xFFFE in the SRAM cells of a LUT [44], see Fig. 2.6. Inducing a fault into the cells 0 and 15 of the SRAM results in obtaining a NAND gate.

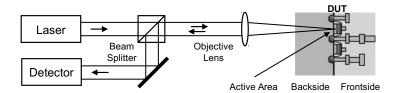

# 2.3.3 Optical Contactless Probing

Laser Voltage Probing (LVP) and Laser Voltage Imaging (LVI) techniques have been introduced in the field of failure analysis to debug the nanoscale transistors from the backside of the chip in a contactless way. Therefore, they are referred to optical contactless probing techniques. While LVP can be used to directly probe the electrical signals on the transistors, LVI can be employed to create an activity map of active circuits. In both cases, the laser photons with NIR wavelengths pass through the silicon substrate from the IC backside to reach the transistors, which leads to a partial absorption and a partial reflection of the laser beam. In the case of LVP, the reflected light is modulated based on the electrical signal on a node, and it can be fed to an optical detector to measure its intensity, see Fig. 2.7. In this way, the data passing through a node can be probed. Since the light modulation is insignificant, the signal should be measured several times and averaged by running the device in a triggered loop. In this case, a sufficient signal to noise ratio can be achieved.

For performing the LVI, on the other hand, the reflected light is fed to a spectrum analyzer with a narrow band frequency filter while the laser scans the device. In this case, the detector signal is not averaged. The laser beam is scanned across the Device under Test (DUT) using galvanometric x/y

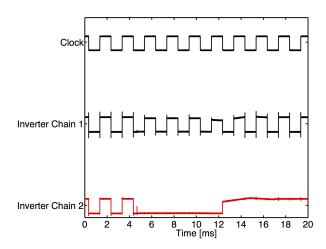

FIGURE 2.7: Simplified illustration of LVP signal acquisition.

mirrors, and the filter output of the spectrum analyzer is sampled for every scanned pixel. Subsequently, a control PC is used to assemble the sampled frequency filter values into a 2D image using a grey-scale representation. If an electrical node operates at the frequency of interest, it will modulate the light reflected with the same frequency, which will be able to pass through the frequency filtering spectrum analyzer. As a result, the nodes with a switching frequency equal to the frequency filter show up as white spots in the LVI image leading localization of them on the chip.

# 2.4 Related Work

Although unclonability and unpredictability are the essential requirements for the PUFs [8], previous work in the literature has demonstrated how different PUFs can be attacked and cloned. Bistable PUFs, such as SRAM PUFs, can be read out by photonic emission analysis and physically cloned by a Focused Ion Beam (FIB) circuit edit [34]. Moreover, it has been shown that SRAM PUFs can be read out by laser stimulation [64]. Besides, SRAM PUFs are also vulnerable to remanence decay in volatile memories [65]. Finally, the vulnerabilities of the SRAM PUFs in general as a replacement for non-volatile memory are reviewed in [35].

In contrast to settling-state-based PUFs, delay-based PUFs (e.g., Arbiter PUF and RO PUF families) are believed to be resistant to physical cloning, due to their more complex and interconnected structures. The main assumption of timing-based PUFs is that only fully-invasive techniques enable an attacker to measure the individual delays within the PUF structure. This kind of attacks might alter the physical properties of the silicon substrate, which leads to undesirable changes in the CRP behavior of the PUF. However, they can still be characterized by various means. For instance, RO PUFs are vulnerable to the EM side-channel attacks [55, 54, 53] and modeling attack [24]. Arbiter PUFs have been a target for mathematical modeling attacks. Thus, the known attacks in the literature try to simulate the CRP behavior of the PUF and build a mathematical clone of it. Modeling attacks require a subset of CRPs to create a model on that and predict the PUF

responses for all possible challenges [41]. It has been reported that an Arbiter PUF under the Deterministic Finite Automata (DFA) representation can be Probably Approximately Correct (PAC) learned with a given level of accuracy and confidence [26].

The modeling attacks become more difficult by introducing non-linearities to the PUF delays and responses. Two example of non-linear PUFs are Feed-forward Arbiter PUFs [42] and XOR Arbiter PUFs [79]. However, a successful modeling attack on XOR Arbiter PUFs with a limited number of Arbiter chains using logistic regression (LR) algorithm is reported [70]. In another attempt, by PAC learning the XOR Arbiter PUF with the Perceptron algorithm, a theoretical limit as a function of the number of PUF stages and the number of chains for pure modeling attack could be found [25]. Although pure modeling attacks fail to learn larger XOR Arbiter PUFs, a combined modeling attack based on a higher number of CRPs with timing and power side channel information can successfully break XOR Arbiter PUFs up to 14 Arbiter chains [72]. In another approach, the noise in the response of the Arbiter PUF was exploited as a side channel information to model the CRP behavior of the single Arbiter PUF [21]. The idea of using noise as a helper information to enhance modeling attacks is further developed by changing the temperature [22] and supply voltage of the chip [11] to induce more noise in the PUF responses. Furthermore, it has been shown that individual chain of an XOR Arbiter PUF can be separately learned by using the noise information in the CMA-ES algorithm [10].

# Chapter 3

# Experimental Setup

In this chapter, we present the deployed reconfigurable hardware and PoC PUF implementations on them for our experiments. Afterward, we introduce the electrical and optical setups used for PEM, LFI, and LVP/LVI. All presented experimental setups in this chapter are previously presented in [85, 82, 84, 81, 45, 83].

# 3.1 Devices under Test

# 3.1.1 Intel/Altera MAX V CPLD

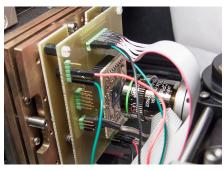

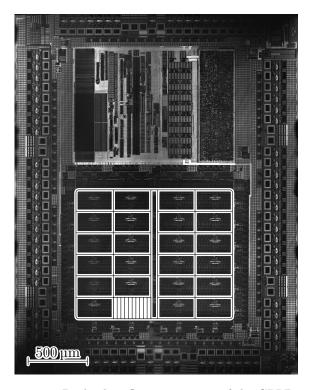

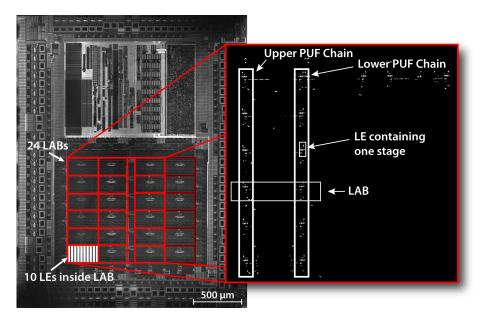

The first group of deployed devices under test were Intel/Altera MAX V CPLDs with part number 5M80ZT100C5N manufactured in a 180 nm process [5]. These samples were used in the PEM and LFI experiments. In this sample all Logic Elements (LE) contain 4-input LUTs and a dedicated register. The LEs in this device are arranged in groups of 10 inside a Logic Array Block (LAB). A 100 pin TQFP package was selected to simplify the sample preparation. All samples were prepared using an Ultratec ASAP-1 polishing machine. This approach allows selective die thinning of packaged samples without the need for re-bonding the samples. The samples were thinned to approximately 30 µm in substrate thickness and were inversely soldered to a custom PCB, see Fig. 3.1(a). Altera MAX V CPLD contains an internal NVM to store the configuration. A JTAG connection was used to write the configuration into the NVM.

# 3.1.2 Intel/Altera Cyclone IV FPGA

The second groups of deployed devices under test were Intel/Altera Cyclone IV FPGAs with part number EP4CE6E22C8N manufactured in a 60 nm process [6]. We chose the Cyclone IV since it is similar in architecture to the MAX V. This enables us to utilize the same PUF implementations, which

(a) Altera MAX V

(b) Altera Cyclone IV

FIGURE 3.1: Devices under Test: (a) A MAX V CPLD in 180 nm process manufactured by Altera. (b) A Cyclone IV FPGA in 60 nm process manufactured by Altera.

FIGURE 3.2: Implementation of an Arbiter PUF by two independent inverter chains. Each challenge bit is connected to all *don't-care* inputs of the utilized LUT.

allows us a direct comparison. These samples were used in the PEM and  ${\it LVP/LVI}$  experiments.

In this sample, all LEs contain 4-input LUTs and a dedicated register. The device contains 6272 LAB with 16 LEs each. We chose the 144 pin TQFP package in order to simplify the sample preparation. The first step of preparation was the removal of the exposed ground pad on the backside of the package. The samples were then thinned by an Ultratec ASAP-1 polishing machine to a remaining silicon thickness of 25 µm. In the second step, the prepared samples were inversely soldered to a custom PCB, see Fig. 3.1(b). Bond wires originally leading to the exposed ground pad were then reconnected using silver conductive paint. Since Intel/Altera Cyclone IV is an SRAM-based FPGA, no internal NVM in the chip package is available. Hence, a JTAG connection was used for configuring the FPGA after each reboot.

FIGURE 3.3: A LUT is realized by multiple multiplexers, which are controlled by the data inputs. The output of the LUT is loaded from the existing SRAM cells inside the LUT. By connecting *don't-care* inputs A, B and C to a single bit challenge and connecting the input D to the output of previous stage, only two routes can be selected based on the challenge value.

# 3.2 Hardware Implementations

# 3.2.1 Standalone PUF Implementations

For the PEM and LFI experiments in chapters 4 and 5, standalone PUFs, namely Arbiter PUFs and RO PUFs, have been realized on the CPLDs and FPGAs. In the case of Arbiter PUF, each stage can be realized by two digital multiplexers on the chip. Although this design can be implemented in an optimal way on an ASIC, it causes delay imbalances for upper and lower PUF chains on an FPGA. Moreover, the effect of the routing between the LUTs on the PUF response is more influential than the effect of intrinsic delay differences on the individual devices [63]. A better Arbiter PUF design, which is more suited for FPGAs, can be realized by two independent buffer or inverter chains as proposed in [51], see Fig. 3.2. In this case, each stage requires two LUTs. One input of each LUT is configured as the input for the incoming signal from the previous stage and all other don't-care inputs are connected together to a single challenge bit, see Fig. 3.3. As a result, by applying a challenge bit, two different routes inside the LUT can be involved. Each stage is placed manually in a way to make the total timing of PUF chains as symmetric as possible.

The arbiter can be implemented by dedicated registers inside the CPLD or FPGA. However, if the delay differences between upper and lower chains are less than the precision of the register, the arbiter will be in a meta-stable condition. Moreover, the propagation delays of data and clock lines inside the registers are different, and consequently, the delay differences of the upper and lower chains will be biased at this point. Thus, for our experiment we read out the response of the PUF directly by measuring the overall delays

FIGURE 3.4: A simplified schematic of a ring-oscillator pair in the RO PUF construction. After a predefined period of oscillation, the states of both counters are compared to each other to generate a binary response.

of both chains with the help of a Time-to-Digital converter (TDC) by either capturing photons from the transistors terminating the Arbiter PUF chain or measuring directly the arrival of the electrical signals at the outputs of the final stage.

In the case of RO PUF, ring-oscillators can be implemented as a logic circuit comprised of an odd number of LUTs, which are configured as inverters, connected in series to form a ring. The output of the last LUT is fed back to the input of the first LUT. Due to the odd number of inverters, as long as the circuit is powered up, every inverter-configured LUT continuously oscillates between 0 and 1. For the LFI experiments, ring-oscillators with five inverters plus one logical AND gate for enabling and disabling the ring have been implemented. The entire circuit of each ring-oscillator was placed within a single LAB, and each inverter was placed in an individual LE within the LAB.

Binary counters using dedicated registers of the CPLD or FPGA can measure the frequency of the individual ROs in a predefined interval. However, to have a higher precision, we measured the frequency of all ring-oscillators directly by oscilloscope and spectrum analyzer. In this case, the outputs of the ring-oscillators were connected directly to the pins of the chip for a direct electrical measurement.

# 3.2.2 Red Key Calculation

For the LVP and LVI experiments in chapters 6 we have implemented an RO PUF and a red key (see chapter 2.2.1.) calculation on the FPGA. To make the design less complex, we have connected the outputs of the ROs directly to individual counters, see Fig. 3.4. Each ring-oscillator in our design has been realized with 21 inverters. All components of the ROs and the counters have been placed manually inside the FPGA using the Altera Quartus II integrated development environment. The LEs in every ring-oscillator were placed as close as possible, directly next to each other. We have emulated the rebooting and configuration of the FPGA by adding a reset signal to our implementation. The black key and PUF key in our design have 8-bit length. As discussed in Sect. 6.1, unwrapping the black key can be carried

out either in a parallel or serial way. Hence, for the first scenario, we have implemented the red key generation by XORing all values of the black key with the PUF key in parallel, see chapter 6.1.1. For the second scenario, we have realized two shift registers for the black key and PUF key, where those values are shifted serially to an XOR gate and the result is shifted into the red key registers.

#### 3.2.3 PUF-based Sensor

To design a PUF-based sensor for LVP and LVI detection in chapters 6 we implemented a 16-bit RO sum PUF comprised of 32 ROs on the FPGA. Each RO in our design comprised of 5 inverters. The ROs were placed manually and distributed all over the FPGA silicon area, which utilized about 15% of FPGA resources. The frequencies of ROs are measured by 16-bit counters. The challenges are transmitted from a laptop via the UART protocol to the FPGA and the generated responses are sent back on the same channel to the laptop.

# 3.3 Optical Setup

# 3.3.1 Photonic Emission Analysis Setup

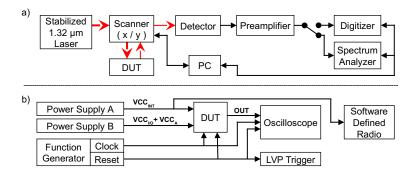

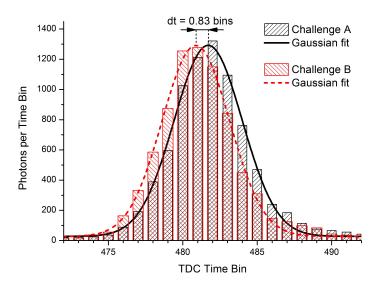

The experimental setup consists of an optimized infrared microscope equipped with a Si-CCD camera and an InGaAs avalanche diode as detectors for spatial and temporal analysis [75], see Fig. 3.5. The Si-CCD is cooled down to  $-70\,^{\circ}$ C to minimize dark current. This allows long exposure times to accumulate enough photons from the weak hot carrier emission. Since the integration time of CCD camera is several seconds and the readout speed of its sensor is limited, the Si-CCD camera is used for spatial photonic emission analyses only. Hence, a very fast infrared detector is required for the temporal photonic emission analysis. A free-running InGaAs avalanche detector in Geiger Mode (SPAD) can fulfil this requirement and be used to detect single photons. The sensitivity of SPAD covers a wavelength range between 1 to 1.6  $\mu$ m. A computer controls the DUT via a control box (CB), which provides the trigger pulse, i.e., enable signal, for the implemented Arbiter PUF and a time reference signal for the FPGA-based TDC. The emitted photons from the DUT are collected by the microscope objective with an NA = 0.6and divided into two optical paths by a short-pass beam splitter (BS). While short-wavelength photons below 1  $\mu$ m are transmitted to the Si-CCD camera, the long-wavelength photons are reflected onto the InGaAs-SPAD. This configuration allows spatial and temporal photonic emission analysis simultaneously. An incoming photon from the DUT causes the avalanche breakdown

FIGURE 3.5: Schematic of Photonic Emission Setup

of the SPAD and the resulting electrical pulse is registered by the TDC. The TDC register the time of each occurring event with a resolution of 81 picoseconds. In this case both the enable signal of the Arbiter PUF and the detected photons from the transistor terminating the chain are time tagged allowing a direct calculation of their delay. The overall time uncertainty for a single photonic event is 190 ps rms. This is due to the jitter in the response time of the SPAD and electrical jitter in the CB and TDC. However, an accumulation of multiple photonic events is used to increase the time resolution by computing the mean value of the Gaussian-like distribution of the delay time histogram. This technique enhances the time resolution significantly beyond the 81 ps granularity of the TDC and allows measurements of timing differences at the end of the PUF chain for two different challenges. As a result, the accuracy of our time-resolved measurement setup is limited by drifts in the electronics to 6 ps rms. The setup contains a custom made holding of the DUT to a 3-dimensional moving stage and electronics to control and communicate with the DUT.

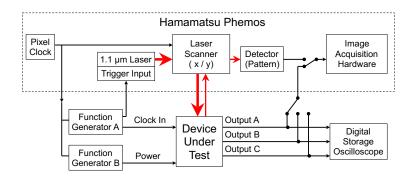

#### 3.3.2 Laser Fault Injection Setup

A Hamamatsu PHEMOS 1000 photon emission and laser scanning microscope was used for LFI experiments conducted in this work (see chapter 5). The system is a commercially available instrument for failure analysis of semiconductor devices. A silicon CCD sensor is used to capture the photonic emission of transistors. The sensor is cooled down thermo-electrically to  $-50\,^{\circ}\mathrm{C}$  to minimize dark current and noise.

FIGURE 3.6: Backside reflectance image of the CPLDs used throughout this work. The framed area contains the programmable logic cells. The grid corresponds to the placement of 4 by 6 LABs. Each LAB contains 10 LEs (only shown for one LAB).

There are two different laser sources with the wavelengths 1064 nm or 1319 nm available on the system. The laser beam is scanned in a zigzag pattern across the DUT, and the reflected light signal is sampled at constant intervals. The individual samples of the reflected light signal are then assembled digitally, corresponding to the laser beam position, and consequently to their physical location on the DUT. In this way, it is possible to acquire a pixel-by-pixel image of the reflected light pattern of the DUT, which can then be used for navigation. Fig. 3.6 shows an acquired reflectance image of an Altera MAX V CPLD from the backside. An array of 4 by 6 blocks can be identified, corresponding to the 24 LABs each containing 10 LEs. The non-volatile memory responsible for storing the configuration data, as well as the programming circuitry and additional hard-macros available to the user, can be observed in top half of the reflectance image. Along the perimeter of the device, the I/O pads are clearly visible.

In the LFI experiments, 20x/0.4 NA Mitutoyo objective lens was utilized for long distance navigation. For fault injection attempts and short distance navigation, a 50x/0.76 NA Hamamatsu objective lens was used. In our LFI

experiments, only the laser with 1064 nm wavelength was deployed. This laser source can operate high power impulse mode and low power mode. The low power mode is used for navigation only, and the high power impulse mode is used for fault injection. In low power mode, the maximum laser power at the laser source is 200 mW. In impulse mode, the maximum power at the source is 2 W with a pulse duration of 200 ns. The laser power can be adjusted from 2% to 100% in 0.5% steps.

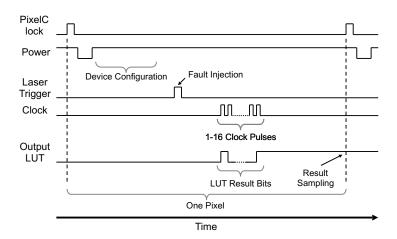

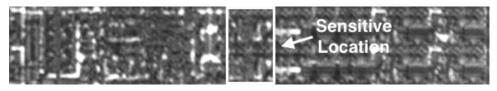

After finding the target LEs by spatial photonic emission analysis, the electrical setup assists us to find the sensitive locations of an LE for LFI in an automated way. In this setup, the laser source scans across the device, and the laser is shot once for every pixel in high power mode. Following the laser shot, the device is first examined for changes in configuration. Afterward, the laser beam moves on to the next pixel position to repeat the same procedure. The obtained configuration changes are then assembled into an image which represents the response to the laser pulse across the examined LE area.

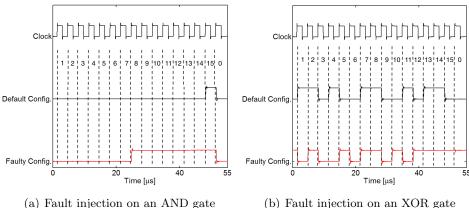

To realize a proper electrical setup, a set of requirements has to be met. First, since we aim to reconfigure the LUTs by injecting faults into the configuration SRAM cells, we need to assure that the DUT is properly reconfigured after each laser shot. Therefore, the DUT has to rebooted for every pixel to trigger the reconfiguration of the LUT SRAM cells. Second, the configuration of DUT has to be tested in a certain time after the laser shot. This step is required because we are only interested in semi-permanent changes (i.e., the faults are permanent as long as the FPGA is powered on or not rebooted) in the device behavior rather than temporary changes, which are only present during laser irradiation. In conjunction with this, after the fault injection, we have to guarantee that the device is still functioning properly and has not entered into an entirely dysfunctional state. Based on these requirements, a setup as shown in Fig. 3.7 should be assembled.