# Contact resistance effects in thin film solar cells and thin film transistors

by

### Marko Marinkovic

A Thesis submitted in partial fulfillment

of the requirements for the degree of

### **Doctor of Philosophy**

in Electrical Engineering

Approved Dissertation Committee

Prof. Dr. Dietmar Knipp Chair, Jacobs University Bremen

Prof. Dr. Veit Wagner Member, Jacobs University Bremen

Prof. Dr. Werner Bergholz Member, Jacobs University Bremen

Prof. Dr. Helmut Stiebig External, Universität Bielefeld

Date of Defense: 27.05.2013

### School of Engineering and Science

# **Table of Content**

| Chapter | 1 Introduction                                                      | 7  |

|---------|---------------------------------------------------------------------|----|

| 1.1     | This thesis                                                         | 9  |

| 1.2     | References                                                          | 10 |

| Chapter | 2 Metal-semiconductor electrical contacts in thin film devices 1    | 11 |

| 2.1     | Lateral current transport in thin film devices                      | 11 |

| 2.2     | Metal-semiconductor electrical contacts                             | 16 |

| 2.3     | References                                                          | 21 |

| Chapter | 3 Thin film solar cells                                             | 23 |

| 3.1     | Materials for thin film solar cells2                                | 25 |

| 3.2     | From individual solar cells to solar modules2                       | 27 |

| 3.3     | Power losses in solar cells                                         | 29 |

| 3.4     | Contributors to series resistance of thin film solar cell           | 33 |

| 3.5     | References                                                          | 37 |

| Chapter | 4 Front electrical contacts of thin film solar cells                | 39 |

| 4.1     | Transmission line method                                            | 39 |

| 4.1.    | 1 Three electrodes measurement technique – Enhanced TLM method. 4   | 40 |

| 4.2     | Screen printing technique for making electrical contacts            | 43 |

| 4.3     | Requirements for front side metallization                           | 45 |

| 4.4     | References                                                          | 49 |

| Chapter | 5 Front electrical contact on CIS solar cells in substra            | te |

| configu | ration                                                              | 50 |

| 5.1     | Fabrication process of chalcopyrite CIS solar cell                  | 50 |

| 5.2     | Electrical contacts on indium tin oxide and zinc oxide smooth films | 52 |

| 5.3     | Screen printed electrical contacts on CIS solar cells               | 55 |

| 5.4     | Electrical contacts on textured ZnO films                           | 56 |

|         |                                                                     |    |

| 5.6                                                                                                                     | Nanoparticle silver pastes                                                      | 61                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.7                                                                                                                     | Summary                                                                         | 67                                                                                                                                                                                              |

| 5.8                                                                                                                     | References                                                                      | 67                                                                                                                                                                                              |

| Chapter                                                                                                                 | 6 Degradation effects of electrical contacts in thin film solar cells.          | 70                                                                                                                                                                                              |

| 6.1                                                                                                                     | Experimental                                                                    | 70                                                                                                                                                                                              |

| 6.2                                                                                                                     | Degradation effects of semiconductor thin films                                 | 70                                                                                                                                                                                              |

| 6.3                                                                                                                     | Degradation of electrical contacts on sputtered zinc oxide films                | 75                                                                                                                                                                                              |

| 6.4                                                                                                                     | Degradation of electrical contacts on CIS solar cells                           | 79                                                                                                                                                                                              |

| 6.5                                                                                                                     | Degradation effects of solar cells parameters                                   | 84                                                                                                                                                                                              |

| 6.6                                                                                                                     | Summary                                                                         | 90                                                                                                                                                                                              |

| 6.7                                                                                                                     | References                                                                      | 91                                                                                                                                                                                              |

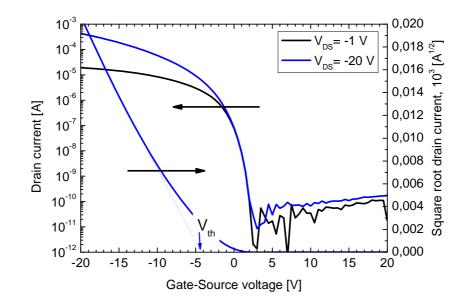

| Chapter                                                                                                                 | 7 Introduction to thin film transistors                                         | 93                                                                                                                                                                                              |

| 7.1                                                                                                                     | Basic principle of operation of thin film transistor                            | 93                                                                                                                                                                                              |

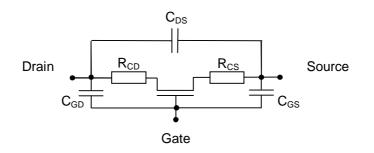

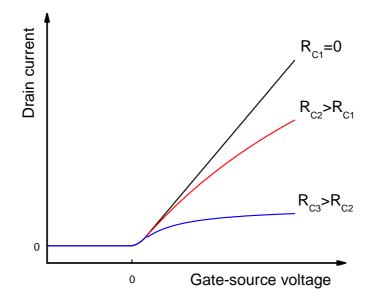

| 7.2                                                                                                                     | Parasitic effects in thin film transistors                                      | 97                                                                                                                                                                                              |

| 7.3                                                                                                                     | Thin film transistors materials                                                 | 100                                                                                                                                                                                             |

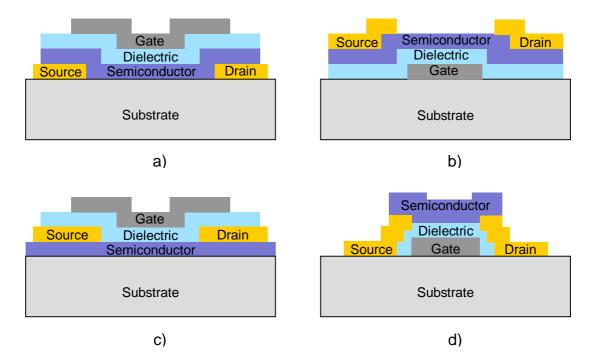

| 7.4                                                                                                                     | Different configurations of thin film transistors                               | 101                                                                                                                                                                                             |

| 7.5                                                                                                                     | References                                                                      | 104                                                                                                                                                                                             |

|                                                                                                                         | Telefoloco                                                                      |                                                                                                                                                                                                 |

| Chapter                                                                                                                 |                                                                                 |                                                                                                                                                                                                 |

| Chapter                                                                                                                 |                                                                                 | hin                                                                                                                                                                                             |

| Chapter                                                                                                                 | 8 Channel potential distribution in poly-3- hexylthiophene based t              | hin<br>107                                                                                                                                                                                      |

| Chapter<br>film trar                                                                                                    | 8 Channel potential distribution in poly-3- hexylthiophene based t              | <b>hin</b><br>1 <b>07</b><br>108                                                                                                                                                                |

| Chapter<br>film trar<br>8.1                                                                                             | 8 Channel potential distribution in poly-3- hexylthiophene based to<br>sistors  | <b>hin</b><br>1 <b>07</b><br>108                                                                                                                                                                |

| Chapter<br>film trar<br>8.1<br>8.2                                                                                      | 8 Channel potential distribution in poly-3- hexylthiophene based to<br>nsistors | <b>hin</b><br>1 <b>07</b><br>108<br>112<br>113                                                                                                                                                  |

| Chapter<br>film tran<br>8.1<br>8.2<br>8.3                                                                               | 8 Channel potential distribution in poly-3- hexylthiophene based to<br>sistors  | hin<br>107<br>108<br>112<br>113<br>116                                                                                                                                                          |

| Chapter<br>film tran<br>8.1<br>8.2<br>8.3<br>8.4                                                                        | 8 Channel potential distribution in poly-3- hexylthiophene based to a sistors   | hin<br>107<br>108<br>112<br>113<br>116<br>124                                                                                                                                                   |

| Chapter<br>film tran<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                                 | 8 Channel potential distribution in poly-3- hexylthiophene based to asistors    | hin<br>107<br>108<br>112<br>113<br>116<br>124<br>130                                                                                                                                            |

| Chapter<br>film tran<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                                          | 8 Channel potential distribution in poly-3- hexylthiophene based to asistors    | hin<br>107<br>108<br>112<br>113<br>116<br>124<br>130<br>131                                                                                                                                     |

| Chapter<br><b>film tran</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Chapter                                 | 8 Channel potential distribution in poly-3- hexylthiophene based to asistors    | hin<br>107<br>108<br>112<br>113<br>116<br>124<br>130<br>131<br>0n                                                                                                                               |

| Chapter<br><b>film tran</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Chapter                                 | 8 Channel potential distribution in poly-3- hexylthiophene based to<br>sistors  | <ul> <li>hin</li> <li>107</li> <li>108</li> <li>112</li> <li>113</li> <li>116</li> <li>124</li> <li>130</li> <li>131</li> <li>on</li> <li>135</li> </ul>                                        |

| Chapter<br>film tran<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Chapter<br>small m                             | 8 Channel potential distribution in poly-3- hexylthiophene based the sistors    | <ul> <li>hin</li> <li>107</li> <li>108</li> <li>112</li> <li>113</li> <li>116</li> <li>124</li> <li>130</li> <li>131</li> <li>on</li> <li>135</li> <li>135</li> </ul>                           |

| Chapter<br><b>film tran</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Chapter<br><b>small m</b><br>9.1        | 8 Channel potential distribution in poly-3- hexylthiophene based to<br>sistors  | <ul> <li>hin</li> <li>107</li> <li>108</li> <li>112</li> <li>113</li> <li>116</li> <li>124</li> <li>130</li> <li>131</li> <li>on</li> <li>135</li> <li>135</li> <li>136</li> </ul>              |

| Chapter<br><b>film tran</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>Chapter<br><b>small m</b><br>9.1<br>9.2 | 8 Channel potential distribution in poly-3- hexylthiophene based to sistors     | <ul> <li>hin</li> <li>107</li> <li>108</li> <li>112</li> <li>113</li> <li>116</li> <li>124</li> <li>130</li> <li>131</li> <li>on</li> <li>135</li> <li>135</li> <li>136</li> <li>137</li> </ul> |

| 9.6                   | Contact resistance model for charge carrier mobility | 153 |

|-----------------------|------------------------------------------------------|-----|

| 9.7                   | Summary                                              | 155 |

| 9.8                   | References                                           | 155 |

| Conclusions 1         |                                                      | 159 |

| Acknowledgement       |                                                      | 163 |

| List of publications1 |                                                      | 165 |

### Chapter 1

### Introduction

Thin film technology is the keystone in the modern applied science and it has been used for several decades in making electronic devices, optical coatings, decorative parts, etc. A thin film stands for a layer of material deposited on a metal, semiconductor or ceramic base. The base, the substrate, of the thin film device, is mostly used as a mechanical support for thin films. Usual thickness of such layers never exceeds several microns, and they can be with conductive or dielectric properties. Thin film materials and deposition techniques have been summarized at [1]. In early 1960s, the first thin film transistor was proposed [2], and in the 1970s several novel thin film devices were proposed, including the thin film surface acoustic wave (SAW) devices [3], the integrated thin film bulk acoustic wave (BAW) devices [4], and thin film integrated optics [5]. Technological improvements and outstanding material science research has paved the way for today's thin films to be utilized in high precision resistors, SAW devices, optical disks, sensors, active matrices for liquid crystal TVs, to name but a few. As a result of increasingly higher demands for more energy and more cost effective electrical devices, the utilization of thin films has additionally been expanded to other industries, such as a usage in photovoltaics, printable electronics, and organic electronic devices. In recent decades, researches on various thin film solar cells and organic electronic devices have pioneered improvements in performance and miniaturization. As devices further miniaturize, performance of thin film transistors suffers as a result of high electrical Ohmic losses which occur. In thin film devices, such as solar cells, radio frequency identification tags (RFIDs) and thin film transistors, the main contributor to high parasitic losses is the contact resistance between metal electrodes and active semiconductor materials.

### Introduction

Further performance improvements in these devices are only possible by reducing the contact resistance.

Contact resistance occurs every time two or more bodies are in contact, and as a result of contact resistance, the system will perform with losses in electrical, thermal and mechanical properties. Elements that affect electrical contacts properties are: contact surface topography, apparent and real contact areas, and materials that comprise the junction.

The surfaces of materials in devices are not inherently smooth due to manufacturing operations and/or the nature of the material. Surface roughness may incur higher contact resistance, and may be responsible for variable growth of material layers deposited at a later time.

The contact between two rough materials often exhibits higher contact resistance, often because the real contact area between the materials is smaller than the apparent contact area. By improving the surface roughness, or perhaps by reducing the number of surface voids on the contact interface, one may lower contact resistance.

Finally, the contact resistance differs in cases where bulk materials are utilized in devices, as in the case when devices and contacts are formed between thin films. The current transport in these types of devices occurs in different manners that may incur gradients in the contact resistance.

Contact resistance effects in electrical devices are undesirable, but unavoidable. The minimization of these effects on a device's functionality has drawn the attention of many researchers from various fields.

In the classical c-Si photovoltaic industry, contact effects are not a prominent issue due to the high processing temperatures utilized in the fabrication steps. On the other hand, in thin-film photovoltaic industry, the process temperature is one of the limiting parameters for the formation of electrical contacts, especially in the case of devices manufactured on plastic substrates. Due to the high contact resistance, conversion efficiency of the thin film solar cells may be affected.

Furthermore, transistors have been the engine of the electronic revolution. As new areas of thin film devices continue to expand, new and different materials have been under investigation for the manufacturing of thin film transistors. On account of miniaturizing devices, contact effects have become a prominent factor on a device's

8

### Introduction

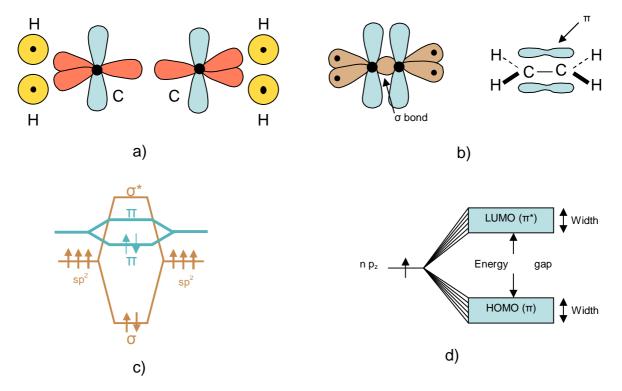

performance. Contact effects may reduce the charge carrier mobility of the devices, as well as the switching frequency in thin film transistors [6]. Lastly, in the past two decades, organic materials have been in vogue with respect to thin film research, particularly in organic electronics. Daily improvements in material properties are increasing the mobility of devices, but with further miniaturization the contact effects may be the limiting factor towards practical implementation of organic electronic devices.

### 1.1 This thesis

This thesis deals with the electrical contact effects in two different types of thin film devices: thin film solar cells and thin film transistors. Although they are operating on different principles, due to the lateral transfer of electrical current in these devices, the contact effect problem is similar for both types of devices. The basic principle of lateral current transport and the general electrical properties of metal-semiconductor contacts are presented in Chapter 2.

The first part of the thesis deals with the contact effect in thin film solar cells, particularly chalcopyrite based solar cells. The basic principles of the solar cells are introduced in Chapter 3, together with the influence of the parasitic effects on their performance, specifically the influence caused by the series and the contact resistance. Chapter 4 deals with measurement techniques to determine the contact resistance of the front electrical contacts on the thin film solar cells. Chapter 5 focuses on the process parameters for fabrication of screen printed electrical contacts for CIS solar cells. Chapter 6 studies the degradation effects of solar cells, as well as the degradation of the electrical contacts caused by aging.

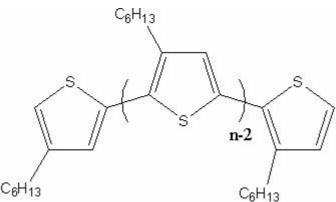

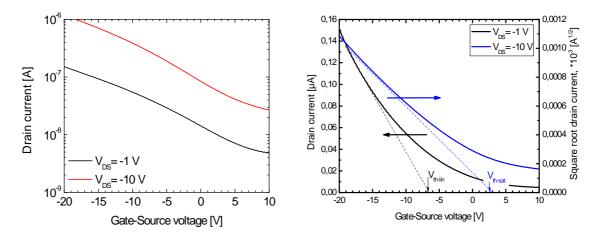

In the second part of this thesis, the contact effects in organic based thin film transistors are examined. Chapter 7 provides the general overview of thin film transistors. Chapter 8 overviews the electronic transport in the organic semiconductors, together with the experimental study of the contact effects in poly-3-hexylthiophene based thin film transistors. Additionally, a new method for determining the contact resistances at the individual electrical contacts of the thin film transistor is presented; a method based on the potential mapping of the transistor

9

### Introduction

channel. Finally, Chapter 9 focuses on the theoretical model of the contact effects in thin film transistors. This model is applicable for devices designed in both transistor configurations, the coplanar and the staggered configuration.

### 1.2 References

- A. Elshabini-Riad, F. D. Barlow, "Thin film technology handbook", McGraw-Hill Professional, 1998.

- [2] P. K. Weimer, "The TFT a new thin-film transistor", Proceedings of the IRE, 1962, Vol. 50, pp. 1462-1469

- [3] G. S. Kino, R. S. Wagers, "Theory of inter digital couplers on nonpiezoelectric substrates", Journal of Applied Physics, 1973, Vol. 44, pp. 1480-1488

- [4] K. M. Lakin, J. S. Wang, "Acoustic bulk wave composite resonators", Applied Physics Letters, 1981, Vol. 38, pp. 125-127

- [5] P. K. Tien, "Light waves in thin films and integrated optics", Applied Optics, 1971, Vol. 10, pp. 2395-2413

- [6] M. Marinkovic, E. Hashem, K.-Y. Chan, A. Gordijn, H. Stiebig, D. Knipp, "Microcrytalline silicon thin film transistors operating at very high frequencies", Applied Physics Letters 97, 073502, 2010.

### Chapter 2

# Metal-semiconductor electrical contacts in thin film devices

### 2.1 Lateral current transport in thin film devices

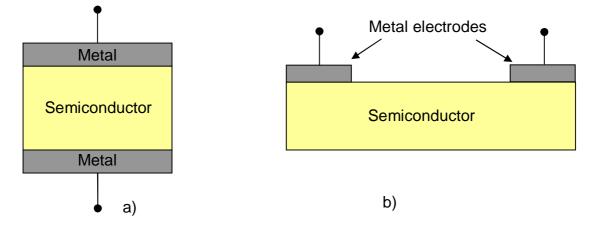

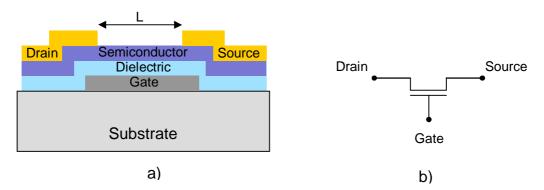

In thin film devices, metal electrodes are deposited to the structure in order to transport electrical current outside. In thin film devices, two types of electrical contact geometry can be found: the vertical and the planar contact configurations, Fig. 2.1.

Fig. 2.1 a) Vertical and b) planar contact geometry.

In the vertical contact geometry, Fig. 2.1a, the current is uniformly distributed along the whole contact, making the current lines perpendicularly oriented to the surface of the metal-semiconductor contact. The electrical contact is characterized by a contact resistance. In the case of the vertical contact geometry, the contact resistance,  $R_C$ , is given by:

$$R_c = \frac{\rho_c}{A} \tag{Eq. 2.1}$$

where  $\rho_c$  is defined as the specific contact resistance, and A is the contact area.

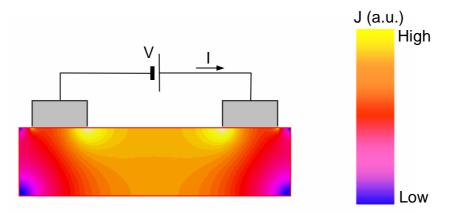

Most of the thin film devices are working in the way that the electrical current is transferred laterally through the device, Fig. 2.1b. The case of lateral current transfer is typical for the solar cells and also in the case of thin film transistors. In the case of the homogeneous semiconductor layers, the current distribution under the electrical contact is not anymore uniformly distributed along the area below (or above) the electrical contact, because the current is choosing a less resistive path to travel through the semiconductor material. The current density distribution in the case of the lateral contact configuration is shown in Fig. 2.2. One can see that the highest current density occurs on the inner part of electrical contact, and reduces its value along the horizontal contact area.

Fig. 2.2 Current density distribution in the lateral contact geometry.

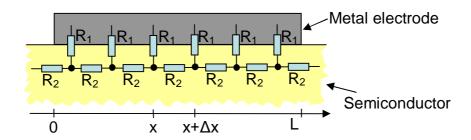

The charge injection from the semiconductor to the metal electrode (and vice versa) can be described with the resistive network shown in Fig. 2.3, which is obtained by slicing the structure into small sections with length  $\Delta x$ . The contact resistance, R<sub>1</sub>, and the resistance of a semiconductor, R<sub>2</sub>, are given by:

$$R_{1} = \frac{\rho_{c}}{W \cdot \Delta x},$$

(Eq. 2.2)

$$R_{2} = R_{Sh} \frac{\Delta x}{W},$$

(Eq. 2.3)

where  $\rho_c$  is the specific contact resistance of the metal-semiconductor interface,  $R_{Sh}$  is the sheet resistance of the semiconductor layer, and W is the width of the contact. Using the Kirchhoff's laws and switching to the differential domain, one obtains the following set of equation:

Fig. 2.3 The resistive network circuit of the lateral contact geometry structure.  $R_1$  and  $R_2$  represent the contact resistance of a metal-semiconductor junction and a semiconductor resistance of a slice  $\Delta x$ , respectively.

Equations 2.4 and 2.5 can be combined in the second order differential equation:

$$\frac{d^2I}{dx^2} = \frac{R_{sh}}{\rho_c} I(x).$$

(Eq. 2.6)

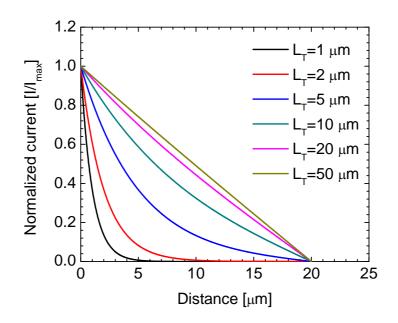

Using boundary conditions at the contact edges,  $I(0)=I_{max}$  and I(L)=0, the final solution for the current distribution long the contact is given by:

$$I(x) = I_{\max} \frac{\sinh\left(\frac{L-x}{L_T}\right)}{\sinh\left(\frac{L}{L_T}\right)}.$$

(Eq. 2.7)

L is the length of the electrode and the parameter  $L_T$ , known as the current transfer length, is defined as

$$L_T = \sqrt{\frac{\rho_c}{R_{Sh}}} \,. \tag{Eq. 2.8}$$

The transfer length represents the length of the contact used for transferring most of the current from the semiconductor to the metal or from the metal to the semiconductor. Distribution of the current that is flowing under a 20 µm contact is illustrated in Fig. 2.4 for different values of the transfer length parameter. In the case when the conductivity of semiconductor film is low, the transfer length becomes small, and most of the current is transferred to the semiconductor close to the edge of the electrical contact. If the conductivity of the semiconductor film is increased, the transfer length takes higher values and the entire electrical contact is used for transferring the electrical current.

Fig. 2.4 Influence of the transfer length on the lateral current distribution underneath a 20  $\mu$ m long contact.

The resistance of the metal-semiconductor contact in the lateral configuration is calculated as [1]:

$$R_{c} = \frac{\sqrt{\rho_{c}R_{Sh}}}{W} \operatorname{coth}\left(\frac{L}{L_{T}}\right).$$

(Eq. 2.9)

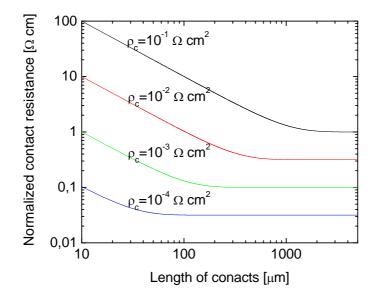

The influence of the length of electrical contacts on the normalized contact resistance, for different values of the specific contact resistance of the metal-semiconductor interface is shown in Fig. 2.5.

Fig. 2.5 The normalized contact resistance dependence on the length of electrodes for different values of the specific contact resistance of metal-semiconductor interface. The sheet resistance of the semiconductor film is Rs=10  $\Omega$ .

For an infinite long electrical contact (or when  $L>>L_T$ ), the normalized contact resistance becomes independent on the length of the electrical contacts, and reaches its minimal value:

$$R_{c}W = \sqrt{\rho_{c}R_{Sh}} = \frac{\rho_{c}}{L_{T}}$$

(Eq. 2.10)

In the limit for a short electrical contact ( $L << L_T$ ), the normalized contact resistance is given by:

$$R_{c}W = \sqrt{\rho_{c}R_{sh}} \frac{L_{T}}{L} = \frac{\rho_{c}}{L}.$$

(Eq. 2.11)

Electrical contacts of devices with narrower electrodes exhibit higher values of the contact resistance. In order to minimize it, one has to come with a design of electrical contact with longer electrodes, which will make electrical devices bigger. The other way for minimizing electrical losses in the contacts is by minimizing the specific contact resistance parameter of the metal-semiconductor interface. With lower values of the specific contact resistance, the normalized contact resistance is reduced.

### 2.2 Metal-semiconductor electrical contacts

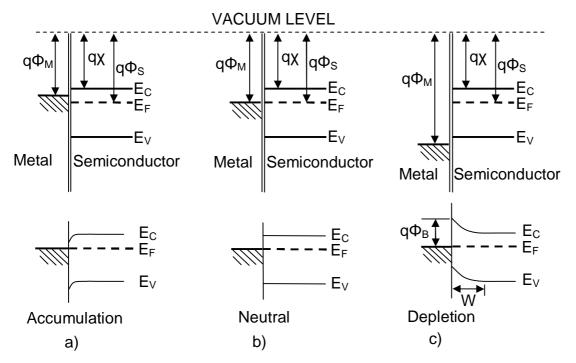

When a metal is making contact with a semiconductor, electrical charges drift from one side of the contact to another, until the thermal equilibrium is set and the Fermi levels in the two materials is coincident [2]. An ideal contact between a metal and an n-type semiconductor in the absence of surface states for three different types of metal-semiconductor contacts is shown in Fig. 2.6. Similar explanations can be derived for a p-type semiconductor.

Fig. 2.6 Three different types of the Schottky (metal-semiconductor) contact: a) accumulation, b) neutral and c) depletion contact type. The upper and the lower parts show the energy band diagrams before and after contact, respectively.

The energy band diagrams are shown before contact in the upper part of the figure and after contact in the lower part. The band diagrams are shown for different metal work functions,  $\Phi_{M}$ . The work function of a solid is defined as energy needed to elevate an electron from the Fermi level,  $E_{F}$ , to the vacuum level [3].

When the work function of the metal is lower than the semiconductor work function,  $\Phi_M < \Phi_S$ , electrons flow from the metal side towards semiconductor (Fig. 2.6a). The transfer of electrons will occur until equilibrium is achieved. Higher concentration of electrons on the side of semiconductor effects bending of the conduction and valence band of the semiconductor. This process is also known as an accumulation, since electrons are accumulated on the metal-semiconductor interface.

If both work functions are equal,  $\Phi_M = \Phi_S$ , there is no flow of charges from the metal to the semiconductor or vice versa. Hence, this is called as a neutral state, Fig. 2.6b.

Finally, when the work function of the metal is higher than the semiconductor work function,  $\Phi_M > \Phi_S$ , electrons flow from the semiconductor side towards the metal. The concentration of electrons in the semiconductor near the junction is reduced, and bending of the energy bands is observed, Fig. 2.6c. A depletion region and a barrier are formed. The height of the energy barrier is given by:

$$\phi_{\rm B} = \phi_{\rm M} - \kappa \,, \tag{Eq. 2.12}$$

where  $\chi$  is the electron affinity of the semiconductor, defined as the difference between the vacuum level, and the bottom of the conduction band, E<sub>C</sub>.

According to the Schottky model the work function of the metal has a distinct influence on the barrier height. However, experimental results showed that the work function of the metal sometimes does not have an influence on the barrier height of the metal-semiconductor contact. An improved electrical contact model of the metal-semiconductor junction is established by introducing surface states of the semiconductor [4]. According to this model, all semiconducting materials can be divided in two groups: covalent and ionic semiconductors.

Semiconductor materials from the fourth group of periodic table of the elements (Si, Ge), and most of III-V semiconductor compounds (i.e. GaAs) are highly covalent [5]. The experimental work showed that the barrier height of such covalent materials is almost independent on the metal work function. For the n-type semiconductor, the

barrier height is approximately 2/3 of the semiconductor band gap,  $\phi_{B,n} \approx 2E_g/3$ , and approximately 1/3 of the band gap for the p-type semiconductor,  $\phi_{B,p} \approx E_g/3$ .

For highly ionic materials, such as most of the II-VI compounds (i.e. ZnO, ZnS) and the transition-metal oxides (i.e. KTaO<sub>3</sub>, KNbO<sub>3</sub>), the barrier height is strongly dependent on the work function of the metal [5]. The formation of electrical contacts with zinc oxide leads to creation of the junction barrier. Different techniques are established to measure the barrier height of the metal-semiconductor junction [6], and here will be just mentioned without going into the details:

- the current-voltage measurement,

- the activation energy measurement,

- the capacitance-voltage measurement,

- and the photoelectric measurement.

In the most of cases the energy barrier between a metal and a semiconductor should be small, so that an ohmic contact is formed between the materials. The best way of forming ohmic contacts is by selecting the appropriate metal that will form neutral or accumulated type of contacts. This is also called barrier height engineering. Finding suitable metal material is usually rather difficult. Hence, a more common technique of forming ohmic contacts is by the deposition of a metal on a highly doped semiconductor.

Nearly all practical metal-semiconductor contacts form a depletion type of contact. The width of the depletion region is inversely proportional to the square root of the doping concentration of the semiconductor,  $W \sim N_D^{-1/2}$ . For very high doping

concentration the width of the depletion region is very small, so that charges can tunnel through the barrier.

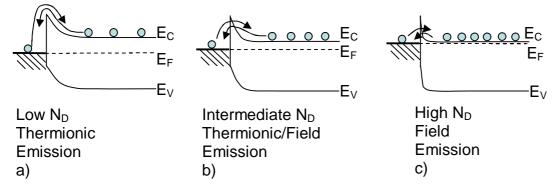

The energy band diagrams of a metal-semiconductor junction for different doping concentrations are shown in Fig. 2.7. For relatively low doped levels, Fig. 2.7a, electrons are thermally excited to energies equal or higher than the barrier height. This process is known as thermionic emission (TE) and the current-voltage relationship is given by:

$$J = A^* T^2 \exp\left[-\frac{q\phi_B}{kT}\right] \exp\left[\frac{qV}{kT} - 1\right],$$

(Eq. 2.13)

where A<sup>\*</sup> is the Richardson constant, T is the absolute temperature in Kelvin, q is the elementary charge, k is the Boltzmann constant. Electrical contacts are characterized by the specific contact resistance, defined as:

$$\rho_c = \left(\frac{\partial J}{\partial V}\right)^{-1} \bigg|_{V=0}.$$

(Eq. 2.14)

Unit of the specific contact resistance is  $\Omega cm^2$ . For the thermionic emission, the specific contact resistance is given by:

$$\rho_c(TE) = \rho_1 \exp\left(\frac{q\phi_B}{kT}\right),$$

(Eq. 2.15)

where

$$\rho_1 = \frac{k}{qA^*T}.$$

(Eq. 2.16)

For intermediate doping concentrations of the semiconductor, Fig. 2.7b, the thermionic-field emission (TFE) is the dominant charge transport process. Charges are thermally activated to energy below the barrier height where the barrier is

sufficiently narrow for tunneling to take place. In the case of the thermionic-field emission, the specific contact resistance is given by:

$$\rho_c(TFE) = \rho_1 C_1 \exp\left(\frac{q\phi_B}{E_0}\right).$$

(Eq. 2.17)

For semiconductors with relatively high doping concentrations the Fermi level is close to the bottom of the conduction band, or even inside the conduction band (degenerated semiconductors), Fig. 2.7c. In this case the barrier width is very narrow, and carriers can tunnel through it without additional excitation. This process is known as the field emission (FE). The expression for the specific contact resistance is given by:

$$\rho_c(FE) = \rho_1 C_2 \exp\left(\frac{q\phi_B}{E_{00}}\right).$$

(Eq. 2.18)

In previous equations, 2.17 and 2.18,  $C_1$  and  $C_2$  are functions of the doping concentration N<sub>D</sub>, temperature T, and the barrier height  $\Phi_B$ . The energies  $E_{00}$  and  $E_0$  used in equations 2.17 and 2.18 are defined as:

$$E_{00} = \frac{qh}{4\pi} \sqrt{\frac{N_D}{\varepsilon_s \varepsilon_0 m^*}},$$

(Eq. 2.19)

$$E_0 = E_{00} \coth\left(\frac{E_{00}}{kT}\right),$$

(Eq. 2.20)

where  $\varepsilon_s$  is the dielectric constant of the semiconductor, h is the Plank constant, and  $\varepsilon_0$  is the electrical permittivity of vacuum.

### 2.3 References

- [1] "Contact resistance Handout", Specialization Area Lab Course, Electronic Device Lab, Jacobs University Bremen, Fall 2008.

- [2] D.K. Schroder, "Semiconductor material and device characterization", 3<sup>rd</sup>

Edition, John Wiley & Sons, New Jersey, 2006.

- [3] J.A. Venables, "Introduction to Surface and Thin Film Processes", Cambridge, 2000.

- [4] R.T. Tung, "Recent Advances in Schottky Barrier Concepts", Materials Science and Engineering, R35, pages 1-138, 2001.

- [5] V.L. Rideout, "A Review of the Theory and Technology for Ohmic Contacts to Group III-V Compound Semiconductors", Solid State Electronics, Vol. 18, pages 541-550, 1975.

- S.M. Sze, "Physics of Semiconductor Devices", 2<sup>nd</sup> Edition, John Wiley & Sons, New Jersey, 1981.

### Chapter 3

## Thin film solar cells

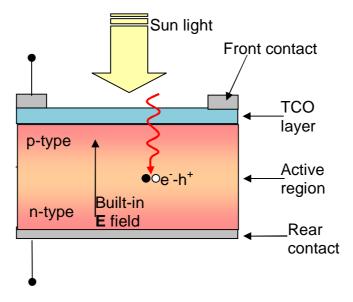

The energy conversion process of a solar cell can be divided into two parts, the photogeneration and charge separation. The solar cell has to be able to absorb a large fraction of the sun spectrum. A schematic cross section of a solar cell is shown in Fig. 3.1. Electron-hole pairs are generated if the photon energy is higher than the energy bandgap of the absorber of the solar cell. In the second step, the electron hole pairs are separated due to the built-in electrical field of the diode, resulting in a photocurrent flow.

Fig. 3.1. The schematic cross section of a solar cell.

The current-voltage characteristic of an ideal solar cell in dark can be described by [1]:

Thin film solar cells

$$I = I_s \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right],$$

(Eq. 3.1)

where  $I_s$  is the diode saturation current, q is the elementary charge, n is the diode ideality factor, k is the Boltzmann constant, and T is the absolute temperature in Kelvin. If the cell is illuminated, the light generated current  $I_L$  is superimposed to the dark (non-illuminated) diode current:

$$I = I_s \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right] - I_L.$$

(Eq. 3.2)

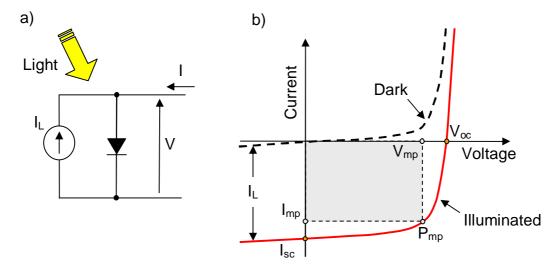

The equivalent electrical circuit and the current-voltage characteristic of an ideal solar cell are shown in Fig. 3.2. The maximum power generated from the solar cell is equal to the product of the short circuit current,  $I_{sc}$ , the open circuit voltage,  $V_{oc}$ , and the fill factor, FF. These three parameters together with the efficiency of the solar cell,  $\eta$ , are the key characterization parameters of the solar cell performance.

Fig. 3.2. a) The equivalent circuit of an ideal solar cell. b) The current-voltage characteristic of a solar cell with and without illumination.

The short circuit current is given by the photogenerated current at short circuit. The open circuit voltage is obtained when there is no current flow through the cell. According to equation 3.2, the open circuit voltage is defined as:

$$V_{oc} = \frac{nkT}{q} \ln \left( \frac{I_L}{I_s} + 1 \right).$$

(Eq. 3.3]

The open circuit voltage depends on the photocurrent and the diode saturation current,  $I_s$ . Lowering of the saturation current will increase the open circuit voltage of the solar cell.

The fill factor of a solar cell, FF, is defined by the ratio of the maximal output power of the cell to the product of the short circuit current and the open circuit voltage:

$$FF = \frac{P_{mp}}{I_{sc}V_{oc}} = \frac{I_{mp}V_{mp}}{I_{sc}V_{oc}}.$$

(Eq. 3.4)

The conversion efficiency,  $\eta$ , defines the ratio of the photogenerated electrical output to the total power of the incident light:

$$\eta = \frac{V_{mp}I_{mp}}{P_{in}} = \frac{V_{oc}I_{sc}FF}{P_{in}}.$$

(Eq. 3.5)

### 3.1 Materials for thin film solar cells

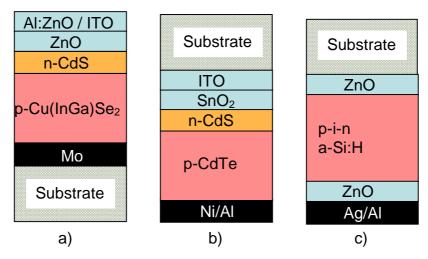

Crystalline silicon based solar cells are nowadays well performing and reliable, commercially available and widely used in a variety of photovoltaic systems. However, their cost is still too high to be competitive with classical electricity production. The thickness of 200 µm of a silicon wafer is needed to absorb sun light (if no light trapping techniques are introduced), and this is the main reason for the high cell cost. On the other hand, thin film solar cells have thickness of several hundred nanometers to a few micrometers. Thin film solar cells consist of sequence of thin film layers which form a photodiode. The thin film solar cells are electrically connected by a metal back contact and a front contact which is usually realized by transparent conductive oxide (TCO). Schematic cross sections of various thin film solar cells are shown in Fig. 3.3. Different absorber materials have been used for thin film solar cells. The most promising thin film solar cells are based on chalcopyrite

compounds (CuInGaSeS), cadmium telluride, and amorphous silicon, Fig. 3.3a-c respectively [2], [3].

Fig. 3.3. a) Chalcopyrite CIGS solar cell in the substrate configuration. b) CdTe solar cell in the superstrate configuration. c) Amorphous silicon solar cell in the superstrate configuration.

Thin film solar cells can be realized in substrate or superstrate configuration. In the superstrate configuration the substrate acts as a carrier for the solar cell. Since the light enters the light through the substrate, the substrate has to perform with high transparency, and thus glass substrates have been widely used.

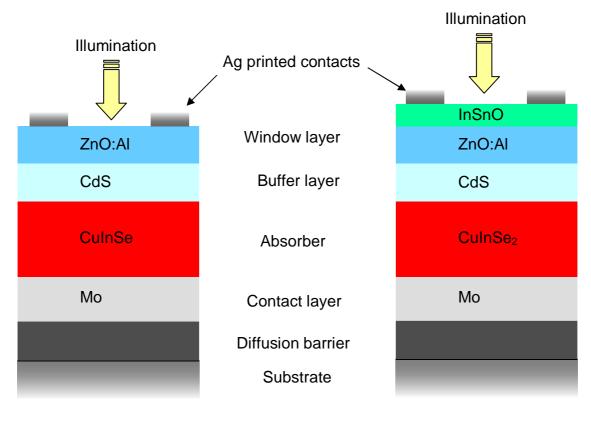

In the substrate configuration the substrate just acts as a carrier for the solar cell. Since the transparency is not the key issue for such solar cell, different materials (i.e. the stainless steel foil) may be used to perform as a substrate for a solar cell. The light enters the solar cell through the transparent conductive oxide (TCO) layer, which is deposited on the top of the solar cell. Transparent conductive oxides are mainly deposited by sputtering processes or by low pressure chemical vapor deposition. Typically, transparent conductive oxides are n-type degenerated semiconductor layers with good electrical conductivity and high transparency in the visible part of the spectrum. Although there are huge numbers of materials that suit in these demands, the most often used TCO layers are aluminum doped zinc-oxide (AI:ZnO) and indium tin oxide (ITO).

### 3.2 From individual solar cells to solar modules

In order to boost electrical output, the solar cells are connected in series and/or in parallel to form a solar cell module. When the solar cells are connected in series, the current that is going through the solar cells is identical through each of them, and the output voltage is equal to the sum of all output voltages of individual solar cells. If the solar cells are connected in parallel, the output voltage over all connected solar cells is identical, and the output current of the device is equal to the sum of the electrical current values generated by individual solar cells. Standard module technology is based on interconnecting the p- type silicon (Si) based solar cells. The interconnections have to connect the rear side of one solar cell with the front side of the neighboring solar cell. The interconnecting process is not simple, and different practical solutions were presented in order to simplify fabrication process and also to achieve some additional esthetical credits [4].

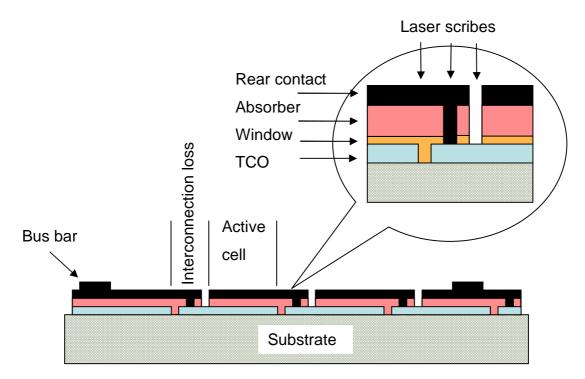

Depending on the thin film solar cell technology and the substrate configuration different concepts are used for serially connection of individual solar cells. In the rigid thin film modules, solar cells and solar modules are manufactured in the same production line. Solar cells are created in the substrate or superstrate configuration, and the electrical connections are created in situ, also known as monolithic integration. The serial connection over a solar module on a glass substrate is illustrated in Fig. 3.4. A laser ablation process is used to pattern the individual layers of the solar cell. Three laser scribing steps are needed to interconnect thin film solar cells on a glass substrate. After the deposition of the TCO layer on the substrate, the TCO layer is structured in a way to define solar cells on the substrate. The production continues with deposition of the window and the active layers. The second laser step is used for patterning the active layer of the solar cell in order to make serial connections between the rear electrode of one solar cell and the front electrical contact of neighboring one. Finally, the rear electrode is deposited and the third laser scribing step is used to remove shortcuts. The losses made by interconnecting cells and modules in such way, strongly depends on the accuracy of the laser scribing steps. The fabrication process is finalized with encapsulation process of the module.

The module is laminated with an encapsulant to a front and/or back sheet, typically with a sheet of glass or EVA (ethyl vinyl acetate) encapsulants.

Fig. 3.4. The schematic cross section of a thin film solar module with monolithic integration connections.

Recently, flexible thin film solar cells and modules were demonstrated by depositing the photoactive layer and other necessary layers on a flexible substrate. When the substrate is an insulator, interconnection of solar cells to a module may be done by using the monolithic integration process. In the case when the substrate is a conductor, other techniques for electrical connection must be used. Solar modules may be realized by interconnecting individual solar cells similarly to conventional interconnection process of crystalline silicon solar cells. In this work, the electrical contact formation on CuInSe thin film solar cells was studied. The solar cells were deposited on the flexible stainless steel foil by sputtering processes. The interconnections between individual solar cells were made with copper wire technique. The front electrical contact grid is formed by screen printing metal paste on the top/front surface of a solar cell. The interconnecting process uses copper wire that is glued with the metal paste on the front side of one solar cell. The electrical connection is closed by soldering/gluing the wire to the conductive substrate (in this

28

case stainless steel foil) of the neighboring cell. The process is repeated over the whole solar cell module.

### 3.3 Power losses in solar cells

The performance of a solar cell is reduced due to the influence of several power loss mechanisms. To achieve high conversion efficiency the losses in the solar cell have to be minimized. According to the origin, these losses can be divided into two groups, optical and electrical losses.

Optical losses can occur due to:

- surface reflection the reflection loss is proportional to the refractive index difference between the solar cell and air.

- front contact shading shadowing losses are proportional to the area of solar cell covered with the front contact grid.

- absorption losses light is also absorbed in regions that do not contribute to the photocurrent. As an example, the absorption can occur in the window layer of thin film solar cell reducing the amount of light transmitted into the active layer of a solar cell.

The electrical losses can be further classified in recombination and ohmic losses. Recombination processes play an important role in solar cells. Photogenerated charges can recombine before reaching the electrodes of the solar cell. The recombination of charges mainly reduces the open circuit voltage of a solar cell and increases the diode ideality factor, which have a consequence the reduction of the solar cell fill factor. In solar cells, two different types of recombination are observed:

- the surface recombination,

- and the bulk recombination.

In the case of a crystalline silicon solar cell, which is a diffusion controlled solar cell, bulk recombination can be reduced by using material with high diffusion length. In the case of a thin film silicon solar cell, which is a drift controlled device, bulk recombination can be reduced by using material with high mobility lifetime product. On the other hand, the surface recombination may be minimized with the surface passivation.

Fig. 3.5. The equivalent electrical circuit of a real solar cell.

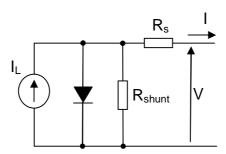

The parasitic Ohmic losses in solar cells are undesirable and also unavoidable effects. Parasitic resistances, the series and the shunt resistance, reduce the conversion efficiency of a solar cell. The equivalent circuit of a real solar cell is shown in Fig. 3.5. The shunt resistance,  $R_{shunt}$ , represents the resistive losses caused by the current leakage across the diode and along the edge of a solar cell. Impurities and crystal defects in the depletion region are also contributors to a low parallel resistance. Contributors to the series resistance,  $R_s$ , will be analyzed separately in the next subchapter.

The current-voltage characteristic of a real solar cell with the parasitic resistances is given by:

$$I = I_L - I_s \left\{ \exp\left[\frac{q}{kT} (V + IR_s)\right] - 1 \right\} - \frac{V + IR_s}{R_{shunt}}.$$

(Eq. 3.6)

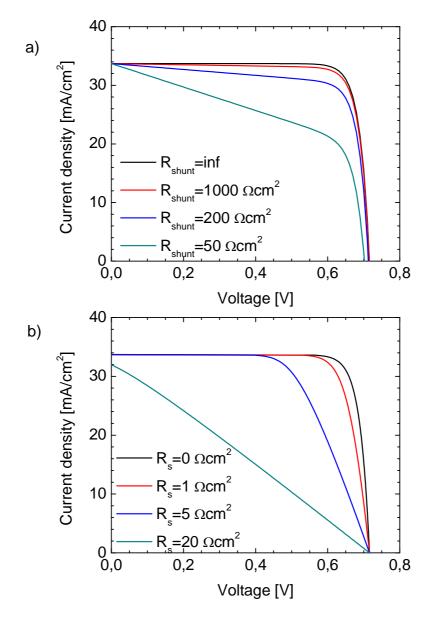

The influence of the series and the shunt resistance on the current-voltage characteristics for a thin film solar cell is shown in Fig. 3.6. The illustration has been modeled for the chalcopyrite based CIGS thin film solar cell according to [5]. The solar cell performed with the short circuit current of 34.8 mA/cm<sup>2</sup> and the open circuit voltage of 713 mV over the area of 0.996 cm<sup>2</sup>. In the ideal case, the shunt resistance is taking infinite value and the value of the series resistance is zero. As the shunt resistance of the solar cell decreases, the current-voltage characteristic perform with curve bending and the solar cell fill factor reduces its value. For very low values of the shunt resistance (lower than 200  $\Omega$ cm<sup>2</sup>) the open circuit voltage of the solar cell reduces its value. Values for the shunt resistance higher than 1 k $\Omega$ cm<sup>2</sup> may be

assumed as a satisfactory value for the shunt resistance of a CIGS solar cell because the current-voltage characteristic is not strongly affected.

Fig. 3.6. a) Influence of the shunt resistance on the current-voltage characteristics of the CIGS solar cell with neglected influence of the series resistance. b) Influence of the series resistances on the current-voltage characteristic of the CIGS solar cell assuming no effect of shunt resistance. The solar cell parameters in this model were taken from [5] and [6].

On the other hand, the series resistance may cause change of the output characteristic of a solar cell. As the series resistance increases, the bending of

current-voltage characteristic of the solar cell occurs (the characteristic becomes less "squared") and the fill factor reduces, while the open circuit voltage and the short circuit current remain unchanged. As the series resistance is increased to values above 20  $\Omega$ cm<sup>2</sup>, the short circuit current is reduced, as well as the fill factor of the solar cell. By neglecting the influence of the shunt resistance on the solar cell performance, the generated output power from the solar cell may be calculated as:

$$P = IV = I\left[\frac{kT}{q}\ln\left(\frac{I_{L}-I}{I_{s}}+1\right)+R_{s}I\right].$$

(Eq. 3.7)

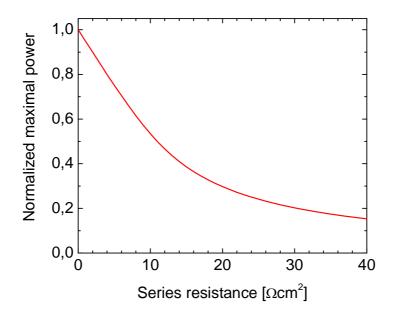

Fig. 3.7. Normalized maximal generated power versus series resistance (according to the Fig. 3.6b).

The Fig. 3.7 illustrates the influence of the series resistance on the generated output power of the CIGS solar cell. The solar cell has been modeled with the same parameters as in Fig. 3.6 and assuming the infinite shunt resistance in the solar cell. As the series resistance increases, the output power of the solar cell reduces, and the drop of the power is very prominent for the small values of the series resistance. The solar cell with the series resistance of 2  $\Omega$ cm<sup>2</sup>, would perform with 10% lower output power then when there would be no electrical losses generated in the solar cell. As the series resistance of the CIGS solar cell increases to 5  $\Omega$ cm<sup>2</sup> the output

### Thin film solar cells

power of the CIGS solar cell will be only 75% of its maximal. Thus, minimization of the series resistance is necessary step in order to achieve solar cells with high conversion efficiency.

### 3.4 Contributors to series resistance of thin film solar cell

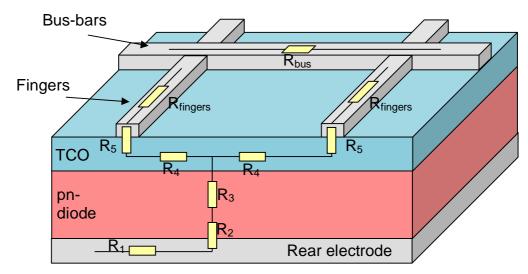

The series resistance of a solar cell can be described as the sum of several different resistances, Fig. 3.8:

- Lateral resistance of the rear contact, R<sub>1</sub>,

- Contact resistance between the rear electrode and the diode, R<sub>2</sub>,

- Bulk/semiconductor resistance, R<sub>3</sub>,

- Resistance of the transparent conductive oxide, R<sub>4</sub>,

- Contact resistance between the front electrode and the semiconductor, R<sub>5</sub>,

- Grid fingers resistive losses, R<sub>fingers</sub>,

- Collection bus ohmic losses, R<sub>bus</sub>.

Fig. 3.8. The cross section of a thin film solar cell with an illustration of the resistive losses.

The resistance of the rear metal electrode, R<sub>1</sub>, is calculated as:

$$R_1 = \rho_{m,back} \frac{t_m}{A}, \qquad (Eq. 3.8)$$

where  $\rho_{m,back}$  is the resistivity of the rear metal electrode,  $t_m$  is the thickness of the rear electrode, and A is the unit area of a cell. Due to very high conductivity of used metal, this resistance is (usually) negligible.

The contact resistance of the back contact electrode to the semiconductor layer,  $R_2$ , is given by:

$$R_2 = \frac{\rho_{c,back}}{A}, \qquad (Eq. 3.9)$$

where  $\rho_{c,back}$  is the specific contact resistance of the metal-semiconductor contact on the back side of a solar cell. In the case of the CIGS solar cells studied in this work, the back electrode is in the contact with entire area of the solar cell. Hence, the contact resistance between the rear electrode and the solar cell can be in general neglected.

The bulk resistance, R<sub>3</sub>, represents resistive losses in the active region of the solar cell. Since the thickness of thin film solar cells is approximately 1-2 µm, the bulk resistance,  $R_3 = \rho_{bulk} \cdot t_{bulk} / A$ , is negligible.

The resistance of the transparent conductive oxide layer, R<sub>4</sub>, is calculated as [7]:

$$R_4 = \frac{R_{Sh-TCO}d^2}{12A} , \qquad (Eq. 3.10)$$

where d is the spacing between adjacent fingers, and  $R_{Sh-TCO}$  is the sheet resistance of the transparent conductive oxide layer, Fig. 3.9. According to the equation 3.10, as the spacing between contact fingers decreases and the conductivity of the TCO layer increases, the contribution of the window layer to the series resistance may be reduced. However, narrowing the distance between the contact fingers has as a consequence of an increase in the number of fingers over the solar cell. The higher amount of finger structures on the front side of the solar cell would result with an increase in the shadowing losses, which can be further on reduced only by narrowing the width of the contact fingers.

The resistance between the front contact grid and the transparent conductive oxide layer,  $R_5$ , is calculated as:

$$R_{5} = \frac{d}{2A} \sqrt{\rho_{c} R_{Sh-TCO}} \operatorname{coth}\left(W_{f} \sqrt{\frac{R_{Sh-TCO}}{\rho_{c}}}\right), \quad (\text{Eq. 3.11})$$

where  $\rho_c$  is the specific contact resistance of the contact finger, and W<sub>f</sub> is the width of the finger. The contact resistance has been already introduced in the Chapter 2 of this thesis. It has been shown that the contact resistance can be reduced by increasing the contact geometry (i.e. W<sub>f</sub>) and decreasing the specific contact resistance  $\rho_c$ .

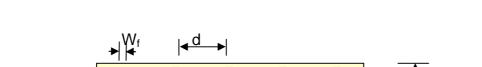

Fig. 3.9 illustrates the front contact grid pattern on a front side of a solar cell. The pattern consists of a wide metal bus-bar and numerous number of narrow finger structures. The grid fingers are characterized with the length  $L_f$  and the width  $W_f$ . The resistance of the grid's fingers is proportional to the resistivity of the fingers and to the geometry of the finger structures:

$$R_{\text{fingers}} = \frac{\rho_{m,\text{front}} dL_{f}^{2}}{3W_{f} t_{\text{finger}} A}, \qquad (\text{Eq. 3.12})$$

where  $\rho_{m,front}$  is the resistivity of the front contact grid and  $t_{finger}$  is the thickness of deposited metal fingers.

The current collected by individual finger structures of the contact grid are further transfer to the bus-bar of a front contact grid. The length of the bus-bar is defined as  $L_b$ =nd, where n is the number of fingers and d distance between adjacent fingers. If the current enters the bus bar continuously, the resistance over the bus-bar is given as:

$$R_{bus} = \frac{n^2 L_f \rho_{m,front} d^2}{12 W_b t_{bus}},$$

(Eq. 3.13)

where  $W_b$  and  $t_{bus}$  are the width and the thickness of the bus-bar, respectively.

Fig. 3.9. Schematic of the front contact grid pattern on a front side of a solar cell.

The shadowing losses are calculated as a ratio of the total grid area to the total area of a cell. For a rectangular solar cell with the simple grid pattern, as the one in Fig. 3.9, the power lost within the shadowing of the front contact grid is given as:

$$P_{shadow} = P_L \eta \frac{W_b L_b + n W_f L_f}{n d L_f} , \qquad (Eq. 3.14)$$

where  $P_L$  is the power density of the incident light and  $\eta$  is the conversion efficiency of the cell.

According to the equations 3.10 - 3.14, dimensions of contact fingers and the busbar have a strong influence on the series resistance of a solar cell and also power losses due to the shadowing effect. As an example, the narrower contact fingers may decrease the shadowing losses, but it ought to result in an increase of the series resistance through the contact resistance,  $R_5$ , and the finger resistance,  $R_{fingers}$ . Hence, a detail optimization of the front contact grid parameters is needed.

#### 3.5 References

- M. A. Green, "Solar Cells Operating Principles, Technology and System Applications", Prentice Hall, Inc., New Jersey, 1982.

- K. L. Chopra, P. D. Paulson, V. Dutta, "Thin Film Solar Cells: An Overview", Progress in Photovoltaics: Research and Applications, Vol. 12, pages 69-92, 2004.

- [3] A. Shah, P. Torres, R. Tscharner, N. Wyrsch, H. Keppner, "Photovoltaic Technology: The Case for Thin Film Solar Cells", Science, Vol. 285, pages 692-698, 1999.

- W. P. Mulligan, D. H. Rose, M. J. Cudzinovic, D. M. De Ceuster, K. R. McIntosh, D. D. Smith and R. M. Swanson, "Manufacturing of solar cells with 21% efficiency", 19<sup>th</sup> EPVSEC, Paris 2004, pages 387-391

- [5] I. Repins, M. Contreras, Y. Romero, Y. Yan, W. Metzger, J. Li, S. Johnston, B. Egaas, C. De Hart, J. Scharf, B. E. McCandless, R. Noufi, "Characterization of 19.9%-efficient CIGS Absorbers", IEEE Photovoltaics Specialists Conference Record, Vol. 33, 2008.

- [6] M. A. Green, K. Emery, Y. Hishikawa, W. Warta, E. D. Dunlop, "Solar Cell Efficiency Tables (Version 39)", Progress in Photovoltaics: Research and Applications, Vol. 20, pages 12-20, 2012.

- [7] D. L. Meier, D. K. Schroder, "Contact resistance: Its Measurement and Relative Importance to Power Loss in a Solar Cell", IEEE Transactions on Electronic Devices, Vol. 31, pages 647-653, 1984.

Chapter 4

# Front electrical contacts of thin film solar cells

In this chapter, the screen printed technique for making front electrical contacts will be described. Details regarding measurement techniques for quantitatively determining properties of electrical contacts will be presented along with industrial requirements that should be reached for electrical contacts of chalcopyrite thin film solar cells.

### 4.1 Transmission line method

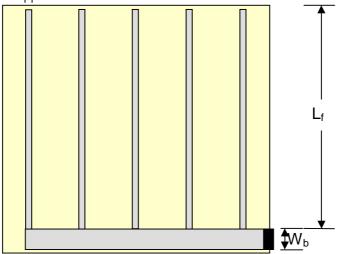

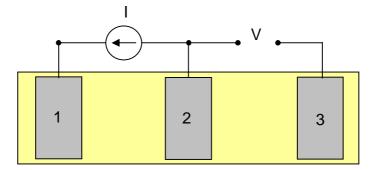

The resistance of a metal-semiconductor contact may be measured with several methods. The standardized technique of measuring the contact resistance is by the 4-probe setup, as depicted in Fig. 4.1. When the current, I, is passing through the sample from the contact 1 to the contact 2, and the voltage V is measured across the two contacts, the total resistance,  $R_{\tau} = V/I$ , is given as:

$$R_{T} = 2R_{C} + R_{Semi} = 2R_{C} + R_{Sh} \frac{d}{W}$$

, (Eq. 4.1)

where  $R_C$  is the contact resistance given by equation 2.9, d is the electrode spacing, W is the width of the electrodes, and  $R_{Semi}$  and  $R_{Sh}$  are the resistance and the sheet resistance of the semiconductor layer, respectively. By knowing the sheet resistance of the semiconductor layer, the width of the electrodes and the spacing between them, the contact resistance can be calculated.

Fig. 4.1 Four probe measurement technique.

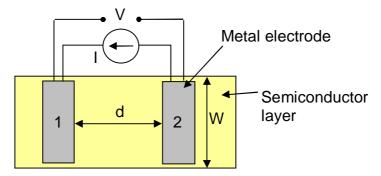

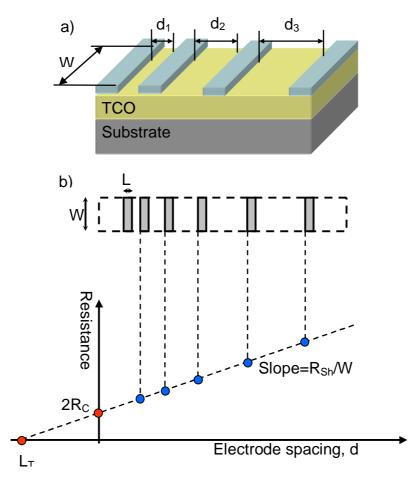

The most commonly used technique for measuring the contact resistance is the transmission line method (TLM). The TLM test structure consists of several electrodes as shown in Fig. 4.2a, that exhibit with the same geometry of length L and width W. The measurements of resistances are made between adjacent electrical contacts while the separation between electrodes is varied. The resistance values are plotted for different space distances between electrodes, and linearly fitted to a graph, Fig. 4.2b. From the plot of the total resistance as a function of the electrode spacing, four parameters can be extracted: sheet resistance, contact resistance, specific contact resistance, and the current transfer length. The slope of the linear fit is proportional to the sheet resistance of the sample, Slope=R<sub>Sh</sub>/W. The intercept with the ordinate is equal to two times the contact resistance of the metal-semiconductor interface, the specific contact resistance and the current transfer length can be determined according to the equations 2.8 and 2.9.

#### 4.1.1 Three electrodes measurement technique – Enhanced TLM method

The transmission line method is a very powerful method for determining the contact resistance. However, it does not yield correct results if the sheet resistance below the electrical contacts is different from the sheet resistance between the contacts. In this case the model has to be extended resulting in the following expression for the total resistance:

$$R_{T} = R_{Sh} \frac{d}{W} + 2R_{c} = R_{Sh} \frac{d}{W} + 2\frac{\rho_{c}}{L_{Tc}W} \operatorname{coth}\left(\frac{L}{L_{Tc}}\right), \quad (\text{Eq. 4.2})$$

where  $L_{Tc}$  is the transfer length calculated as  $L_{Tc}=(\rho_c/R_{Sh-c})^{1/2}$ , and  $R_{Sh-c}$  represents the sheet resistance under the contacts.

Fig. 4.2 Transmission line method (TLM) a) test structure, and b) measurement technique for determining the contact resistance.

The slope of the linear fit, the plot of the total resistance as a function of the electrode spacing, still leads to the sheet resistance, and more precisely, it is the sheet resistance between the electrodes. The intercept of linear fit with the y-axis is double the value of the contact resistance. However, the specific contact resistance and the sheet resistance under the contacts cannot be determined with the standard TLM method. Thus, additional information can be obtained by using the modified test structure shown in Fig. 4.3. The current probes are applied to the electrodes 1 and 2,

while the voltage is measured between the electrodes 2 and 3. This configuration is also known as the contact end resistance configuration.

Fig. 4.3 The contact end resistance test structure.

By dividing the voltage between electrodes 2 and 3 by current flowing between electrodes 1 and 2, the contact end resistance,  $R_{CE}$  is determined. An analytical expression for the contact end resistance is given as:

$$R_{CE} = \frac{V}{I} = \frac{\rho_c}{L_{Tc}W} \frac{1}{\sinh\left(\frac{L}{L_{Tc}}\right)},$$

(Eq. 4.3)

where  $L_{Tc}$  represent the transfer length in the case when the sheet resistance under the electrodes differs from the sheet resistance between the electrodes. The ratio of the contact end resistance and the contact resistance is:

$$\frac{R_{CE}}{R_{C}} = \frac{1}{\cosh\left(\frac{L}{L_{Tc}}\right)}.$$

(Eq. 4.4)

By measuring the contact resistance with the transmission line method and determining the contact end resistance with the three electrodes setup, the specific contact resistance and the transfer length parameter can be calculated. In addition, it is possible to determine the sheet resistances between and under the electrical contacts. The enhanced TLM method demands the accurate measurement of small resistances on the milliohm scale, otherwise the specific contact resistance may be incorrectly calculated.

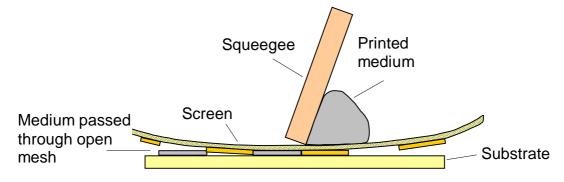

# 4.2 Screen printing technique for making electrical contacts

In industrial applications, the formation of the electrical contacts is one key steps towards the fabrication of final solar cell, yet often, industries are turning towards less expensive deposition techniques and less expensive materials. Printing techniques have a special place in various industry branches because of their simplicity, financial costs, promptness, and flexibility to be used within different technologies. Commonly used printing techniques are: screen printing, syringe printing [1], [2], stencil printing [3], [4], pad printing [5], [6], and roller printing [1], [2]. In the photovoltaic industry, screen printing is the most commonly used method for deposition of thick paste films onto a substrate. In this thesis, electrical contacts for applications in thin film solar cells were fabricated by the screen printed technique.

Fig. 4.4 The screen printing process.

The key advantages of the screen printing are the simplicity, the effectiveness, and the speed of the process [7], [8]. The screen printing is also known as the off-contact printing, since the screen is fixed just above the substrate before printing actually takes place. The process uses a squeegee to press the fluid (i.e. metal paste, ink) through predefined openings in the screen. The screen is a wire netting, typically made from stainless steel, which is then coated with an emulsion layer. As the squeegee starts moving across the screen, it pushes the mesh down into contact with the substrate, and the surplus medium is rolled in advance of the passing squeegee, Fig. 4.4. As the squeegee moves forward, the section of the screen initially pressed then peels away from the substrate behind the advancing squeegee, depositing the paste on the surface as the screen peels off. After leveling, the printed

films are dried, and compound films of very small grain sizes, some reaching up to a few micrometers, are formed.

The printing quality depends on the mesh openings, the wire diameter, and the mesh thickness. Furthermore, the printing process can be controlled with the speed of the squeegee, as well as with the pressure and the angle that squeegee makes on the screen. In order to achieve printing lines with a high quality, the perfect combination of mentioned parameters must be met.

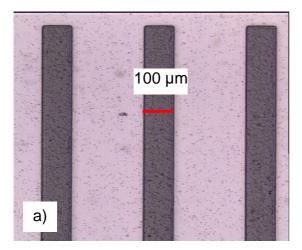

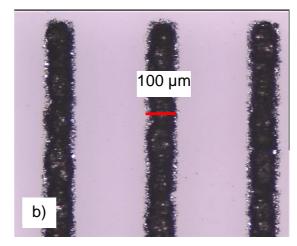

Fig. 4.5 a) Micrograph of a predefined pattern on the screen used for the formation of electrical contacts. b) Micrograph of screen printed structures of CE3104WXL silver paste on the sputtered ZnO substrates, after a thermal treatment.

In this work, all electrical contacts for solar cell applications were produced by a semiautomated screen printing machine. At first, the screen printing process was optimized by varying screen printing parameters, until the resulting printed structures exhibited performances within a desired tolerance. Fig. 4.5a demonstrates a typical designed pattern micrograph for screen printing electrical contacts. Through the openings in the screen, which appear as dark stripes, various metal pastes may be printed on semiconductor substrates, followed by a thermal process to form the electrical contacts. Fig. 4.5b exhibits a micrograph of the screen printed structures of silver paste CE3104 on a sputtered zinc oxide layer. The printed film was then thermally treated for 5 minutes at 125 °C in an air flow oven. The shape and the dimensions of the screen printed structures correspond to the pattern of the screen, however, the silver paste may spread during the screen printing process, which sets the limitation of fine line printing to approximately 100  $\mu$ m.

#### 4.3 Requirements for front side metallization

Metal pastes used to form screen printed electrical contacts contain two main components. The first component consists of an organic binder and a low vapor pressure solvent. The binder and solvent determine the viscosity of the metal paste, which is the key parameter in fine line printing. The component consists of fine metal particles which ensures a high lateral conductivity and governs the electrical properties of the final contact.

Certain requirements must be met in order to use metal pastes for the fabrication of front electrical contacts on CIGS solar cells. A metallic paste should establish sufficient mechanical contact with the substrate, or as in the case of front electrical contacts of CIGS thin film solar cells, a paste ought to provide good adhesion with to a layer of transparent conductive oxide (TCO). The commonly used technique for testing the adhesion quality of a manufactured electrical contact is the scotch tape test. Scotch tape is applied on a sample with screen printed electrical contacts for certain duration of time, and then swiftly removed. The amount of residuals on the tape indicates the adhesion quality. Moreover, printed pastes must be chemically inert for solar cells and module components.

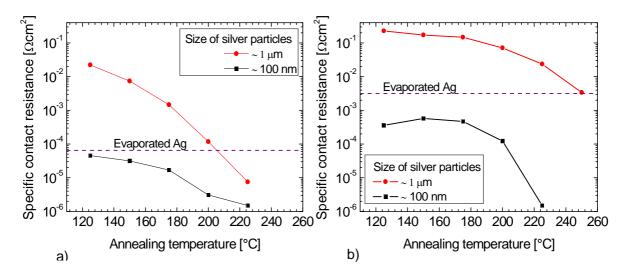

The specific resistance, or resistivity, of deposited metal films must be kept a minimum as to reduce losses in the front contact grid which contributes to the series resistance of a solar cell. The optimal value for the sheet resistance of metallic films should not exceed  $2 \cdot 10^{-4} \Omega$ . The resistivity a metal paste may be further improved by using higher drying temperatures to remove any residual organic binders, but to avoid degradation with CIGS solar cells, the thermal treatment of the screen printed electrical contacts should not exceed temperatures of 170 °C. Low annealing temperatures may also permit the use of metal pastes within devices processed on plastic substrates. In addition to annealing temperature limitations, the annealing time should be kept as short as possible in order to minimize fabrication costs.

In the Chapter 3, it was demonstrated that one of the main contributors to the series resistance of solar cells is the contact resistance of the interface between a metal and a semiconductor layer. In the case of thin film solar cells, the screen printed metal pastes must provide low resistivity electrical contacts with transparent

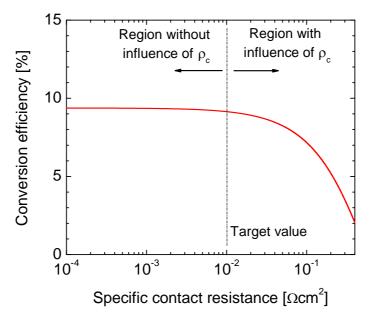

conductive oxide layers. Fig. 4.6 demonstrates the influence of the specific contact resistance of the metal-TCO interface on the conversion efficiency of a CuInS (CIS) thin film solar cell. The given model assumes the width of printed fingers of 100  $\mu$ m and a sheet resistance of 10  $\Omega$  for the TCO layer, while neglecting other contributing influences to the solar cell series resistance [9]. The influence of the specific contact resistance on the efficiency can be divided in two regions. For the values below 10 m $\Omega$ cm<sup>2</sup>, the conversion efficiency is independent on the performance of the front electrical contacts. As the specific contact resistance of metal-TCO electrical contacts increases above 10 m $\Omega$ cm<sup>2</sup>, the conversion efficiency of CIS solar cells drop, and this drop becomes more prominent as the specific contact resistance increases further. Hence, metal pastes used in the fabrication of the front contact grid on CIS solar cells must result in an electrical contact with a specific contact resistance below 10 m $\Omega$ cm<sup>2</sup>.

Fig. 4.6 Influence of the specific contact resistance on the efficiency of CIS solar cell.

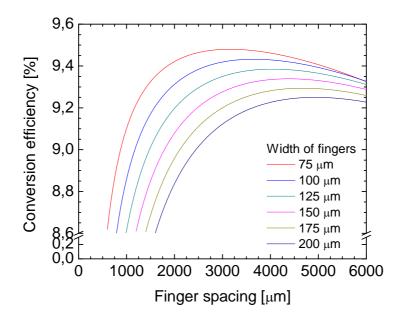

Furthermore, metal pastes must fulfill the fine printed line requirement in order to be used for screen printing of grid fingers and bus-bars of a solar cell. As explained in the Chapter 3, the geometry of the front contact grid influences the series resistance of the solar cell, and therefore the conversion efficiency is as well affected. Fig. 4.7 demonstrates the dependence of the conversion efficiency of a CIS solar cell on the geometry of printed fingers. A 10 cm x 10 cm solar cell has been used as a model,

with a 10  $\Omega$  sheet resistance of the TCO layer and a specific contact resistance between the front contact grid and the TCO layer of 1 m $\Omega$ cm<sup>2</sup>. A low value of  $\rho_c$  has been selected in order to minimize the influence of the front contact grid resistance in the total series resistance of the solar cell. When the spacing between fingers is small, the solar cell is largely shadowed resulting in a reduced conversion efficiency. As the finger spacing increases, the conversion efficiency increases until a maximum value is reached. At maximal conversion efficiency, the more light that enters the cell outweighs the liability of the increased series resistance on account of the increase in finger spacing. For the optimal spacing between fingers when the optical benefits are canceled with resistive losses in the solar cell, the conversion efficiency reaches its maximal value. After this point when the conversion efficiency of the solar cell is maximized, further increasing the finger spacing results in increasing the series resistance, and hence the conversion efficiency drops.

Fig. 4.7 Influence of the geometry of printed contacts on the efficiency of a CIS solar cell.

A higher conversion efficiency may be reached by further narrowing the fingers. As the width of the fingers reduces, the conversion efficiency increases as a result of more light shining on the solar cell. Furthermore, as the width of the fingers reduces, the optimal finger spacing when the conversion efficiency is maximized reduces as well as a result of the increase in the series resistance of the solar cell. Finally, the screen printed metal pastes must fulfill a reliability performance. The properties of the electrical contacts must perform without deviation in their functionality and in the appearance of the solar cell under an accelerated aging test. The long term reliability test, also known as the damp heat test or simply as the aging test, is carried out at elevated temperatures of 85 °C and 85% relative air humidity. Electrical devices and their components are typically exposed for 1000 hours to such harsh conditions.

| Silver paste | Manufacturer              | Average size     | Binder/Solvent                       | Curing       |

|--------------|---------------------------|------------------|--------------------------------------|--------------|

|              |                           | of silver flakes |                                      | temperature  |

| CE 3104      | Emerson & Cuming          | ~ 1000 nm        | Not available                        | Above 120 °C |

| PV410        | DuPont Ltd.               | ~ 100 nm         | Dipropylenglykol-<br>monomethylether | Above 120 °C |

| TEN          | Advanced Nano<br>Products | ~ 5 nm           | α-Terpineol                          | Above 120 °C |

| TESN5050     | Advanced Nano<br>Products | ~ 80 nm          | α-Terpineol                          | Above 120 °C |

| TES          | Advanced Nano<br>Products | ~ 600 nm         | α-Terpineol                          | Above 120 °C |

| TESM8020     | Advanced Nano<br>Products | ~ 1000 nm        | α-Terpineol                          | Above 120 °C |

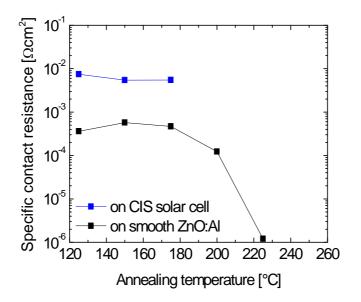

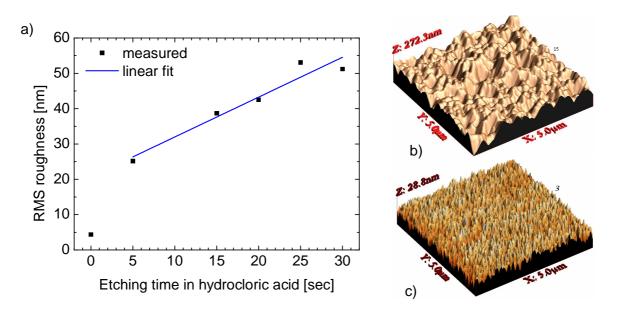

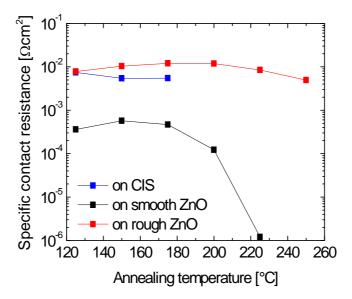

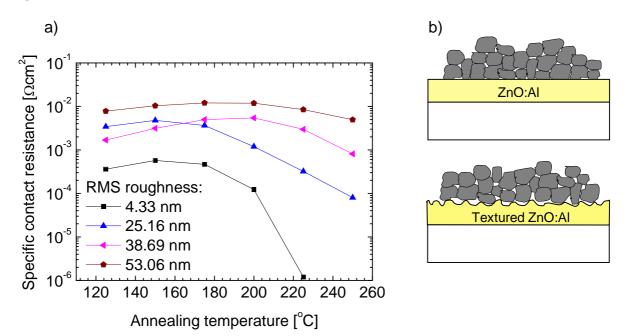

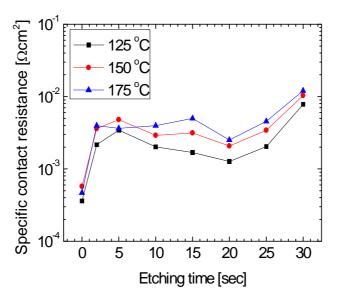

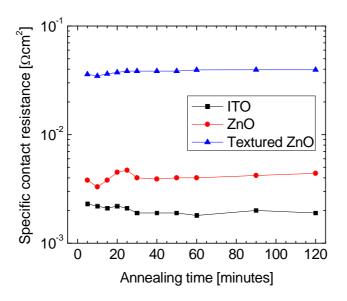

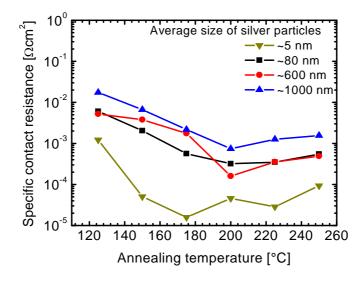

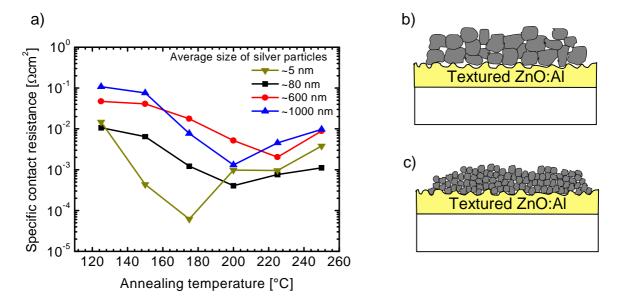

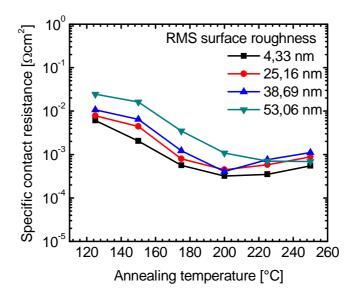

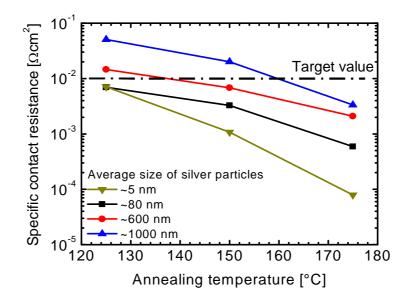

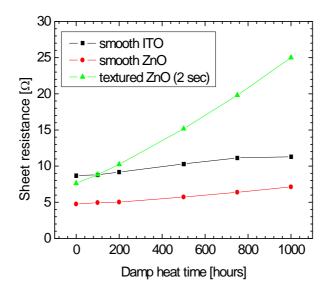

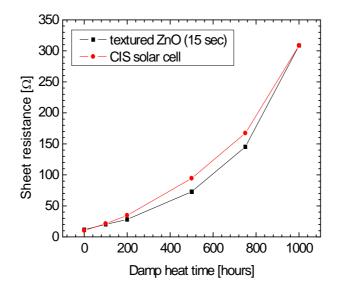

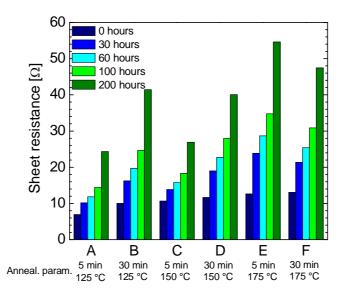

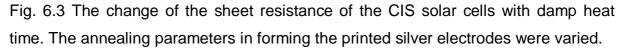

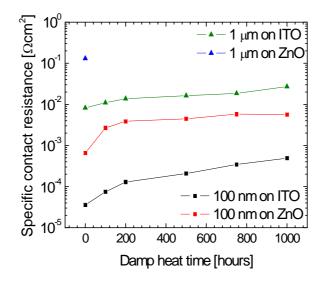

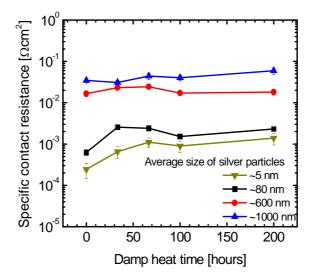

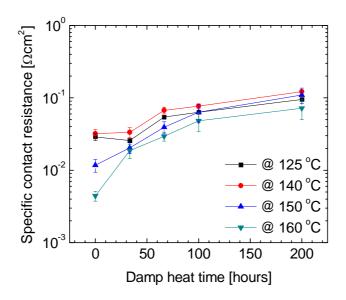

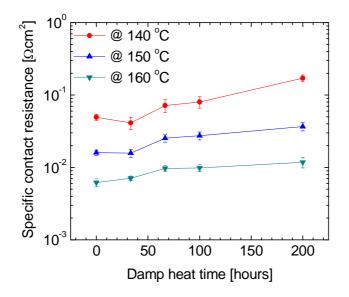

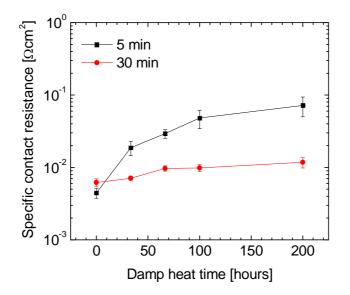

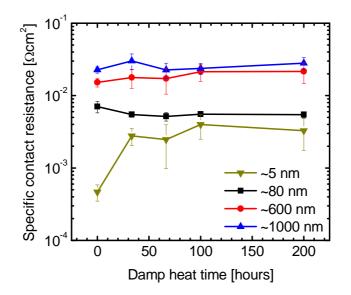

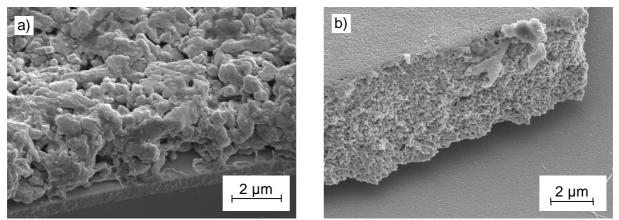

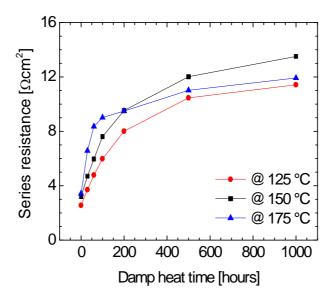

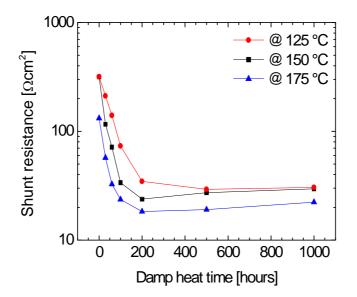

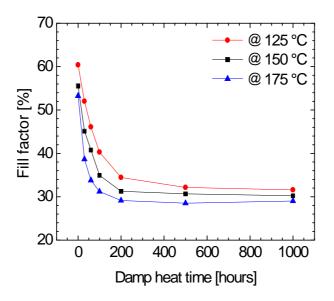

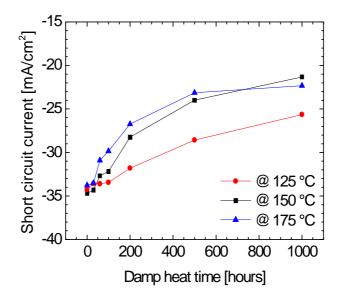

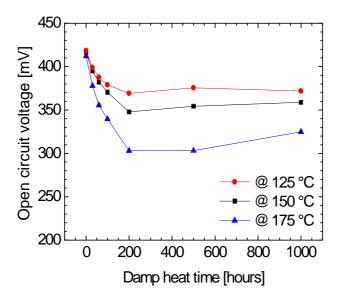

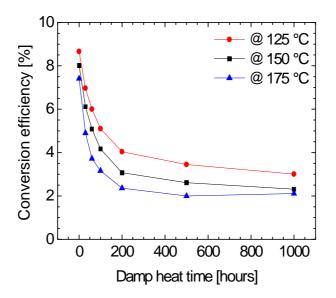

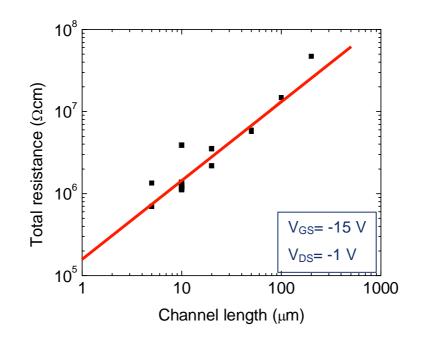

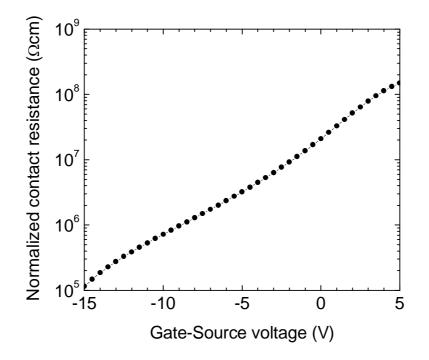

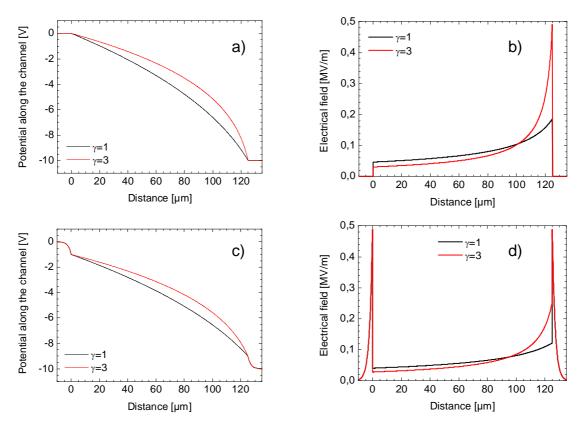

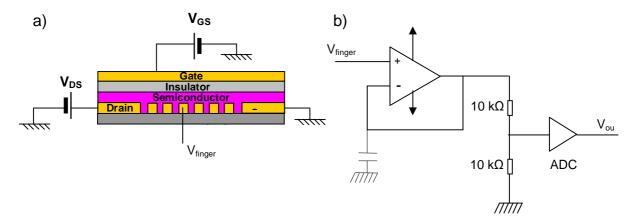

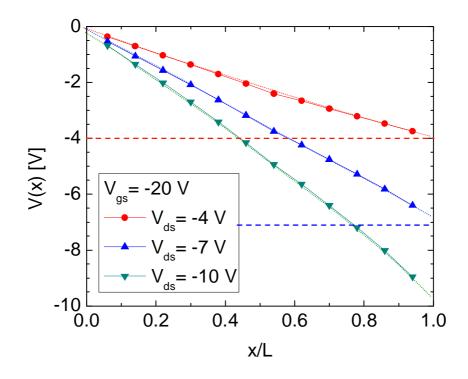

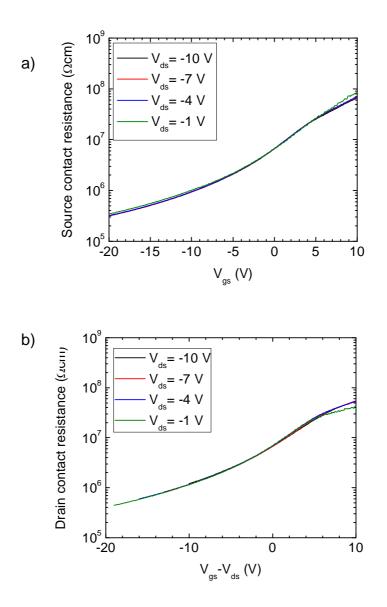

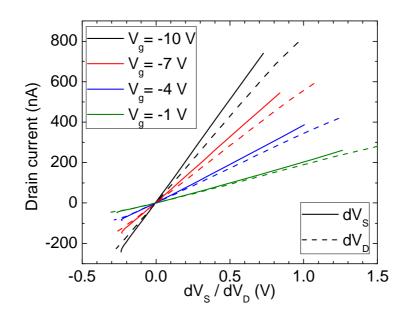

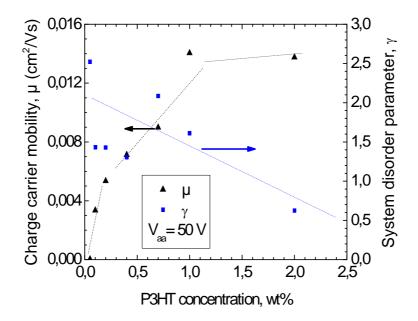

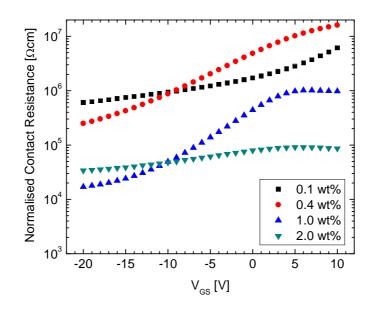

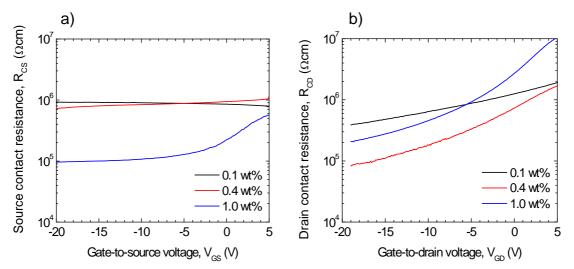

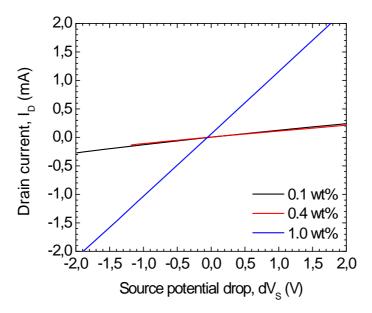

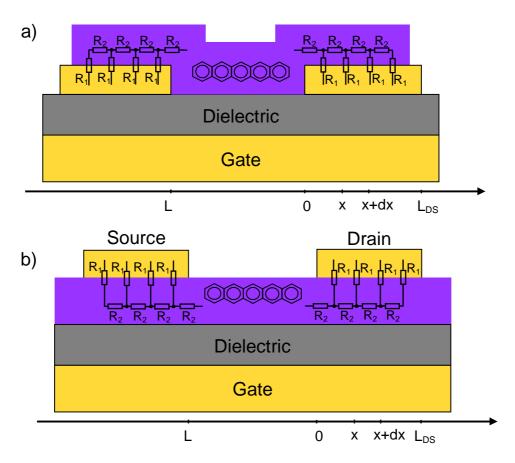

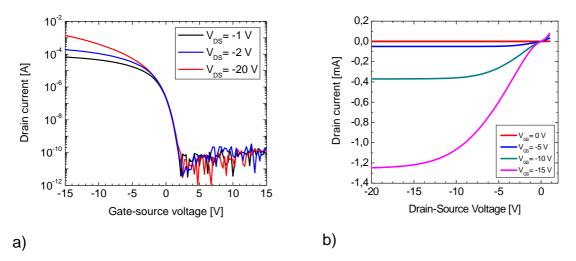

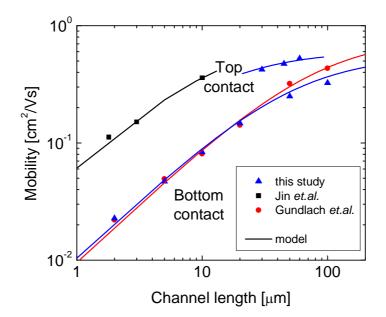

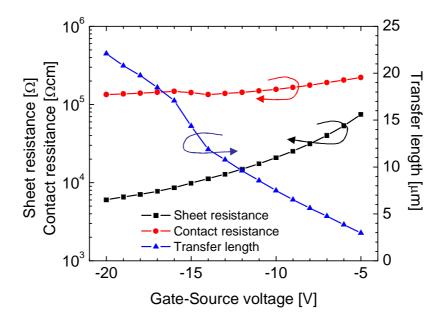

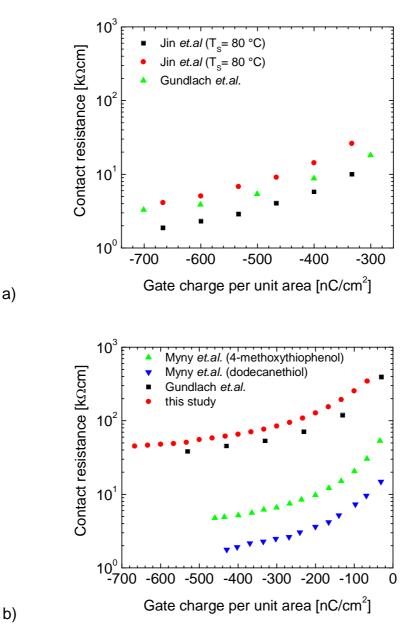

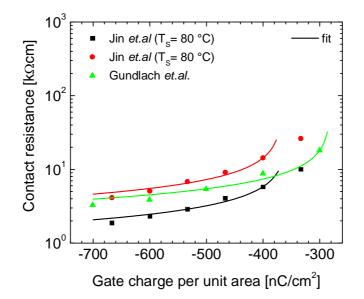

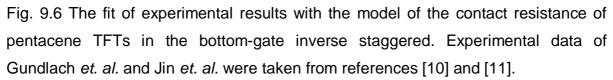

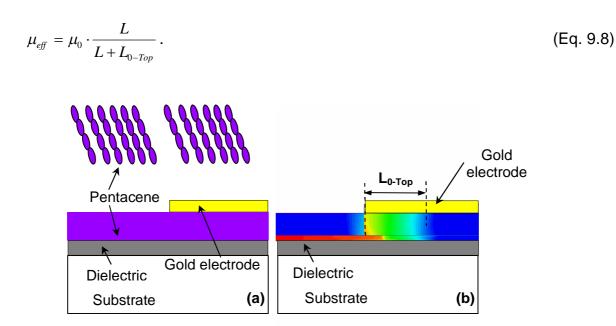

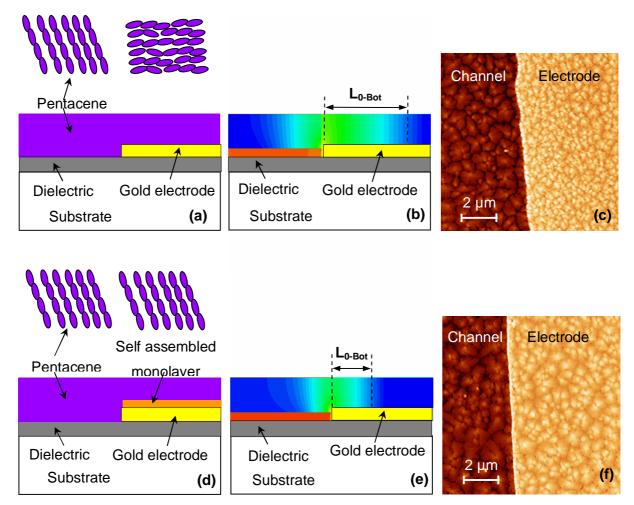

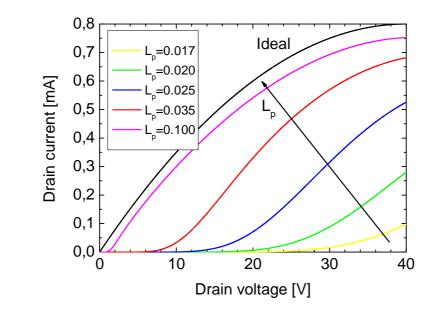

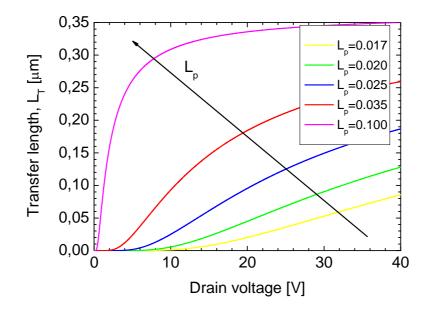

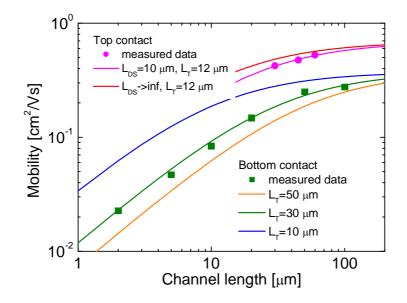

Table 1 List of silver pastes used in this study.